.png) STMCU小助手

发布时间:2022-4-19 22:00

STMCU小助手

发布时间:2022-4-19 22:00

1、基础介绍

通过DMA控制器进行介质访问控制 这部分内容应用于STM32F20X和STM32F21系列,其他的 不适用 ![EEN)SLJ{}Q)$B%]V6}0}95R.png EEN)SLJ{}Q)$B%]V6}0}95R.png](data/attachment/forum/202204/18/223942cnzmmgmv8m8fz3q8.png)

28.1 以太网简介 部分版权 2004 2005 新思科技(美国公司)。所有权利保留,使用需要认可。 借助STM32F20X和STM32F21的以太网外设可接受和发送数据按照IEE 802.3-2002标准 以太网提供一个完整的、灵活的外设去满足不同应用和要求。它支持与外部相连(PHY)的两个标准的工业接口:默认情况使用在IEEE802.3规范找中定义的独立介质接口(MII)和精简介质独立接口(RMII)。它可以被用于大量的需求,例如开关(交换机)、网络接口卡等等

以太网满足下列标准 IEEE802.3-2002,用于以太网 MAC IEEE1588-2008 标准,用于规定联网时钟同步的精度 AMBA2.0,用于AHB 主/从端口 RMII联盟的RMII 规范

28.2 以太网的主要特性 以太网外设包括以下特性,通过类型列举

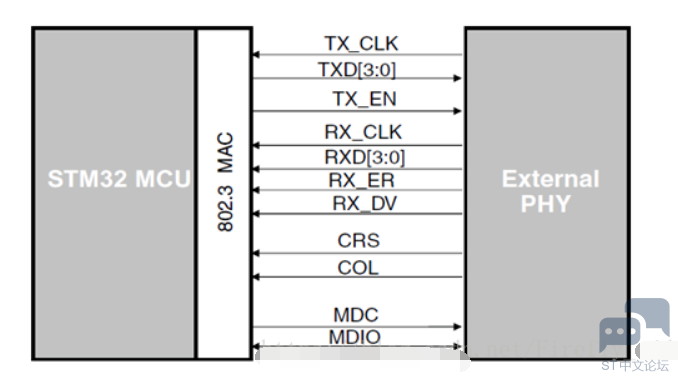

28.2.1 MAC内核特性 支持外部 PHY 接口实现 10/100 Mbit/s 数据传输速率 通过符合 IEEE 802.3 的 MII 接口与外部快速以太网 PHY 进行通信 支持全双工和半双工操作 1.支持适用于半双工操作的 CSMA/CD 协议 2.支持适用于全双工操作的 IEEE 802.3x 流量控制 3.全双工操作时可以将接收的暂停控制帧转发到用户应用程序 4.半双工操作时提供背压流量控制 5.全双工操作中如果流量控制输入信号消失,将自动发送零时间片暂停帧 ![Y2_@RXP$FA]GIZ(0XW_917C.png Y2_@RXP$FA]GIZ(0XW_917C.png](data/attachment/forum/202204/18/223440umuz1u6pcdjmaica.png)

两组 FIFO:一个具有可编程阈值功能的 2 KB 发送 FIFO 和一个具有可配置阈值(默认为 64 个字节)功能的 2 KB 接收FIFO ![PSBLU{4W4]~DU[}]{41Z0H8.png PSBLU{4W4]~DU[}]{41Z0H8.png](data/attachment/forum/202204/18/223440kh8s2npknnxi2fbp.png)

从这里我们可以看出207支持MII接口和RMII接口 ![O76]XMO7H2F5OZVA1X~)0.png O76]XMO7H2F5OZVA1X~)0.png](data/attachment/forum/202204/18/223439km8cjd9jsuqrchcc.png)

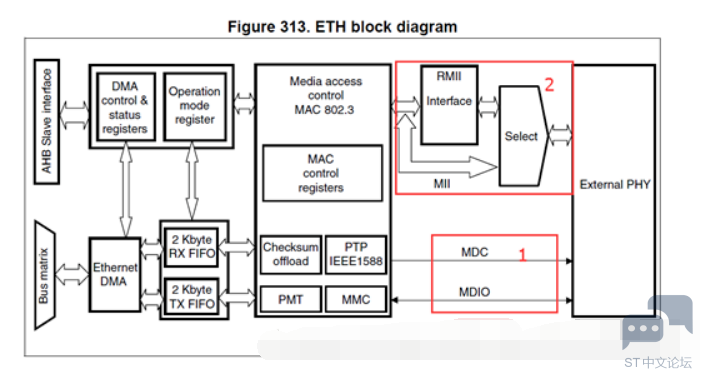

28.4 网络功能描述 以太网外设包括一个MAC 802.3(介质访问控制)和一个DMA控制器。它默认情况下支持MII和RMII接口,通过一个选择位进行切换(参考SYSCFG_PMC寄存器) ![{[D7}5V]]L$(ZV8ZMGL3%FQ.png {[D7}5V]]L$(ZV8ZMGL3%FQ.png](data/attachment/forum/202204/18/223439dgdp8i5dwsip3vv1.png)

DMA控制器通过AHB主从接口和内核与内存相连。AHB主接口控制数据传输,AHB从接口用于访问控制和状态寄存器(CSR)空间 ![8OL~T[RG_{_$RLSSPQH58]V.png 8OL~T[RG_{_$RLSSPQH58]V.png](data/attachment/forum/202204/18/223439ohss1uum12jsnzz1.png)

在MAC内核发送数据之前,数据进过DMA的方式发送到FIFO中缓存。同样的,接收FIFO存储通过线路收到的以太网数据帧,直到这些数据帧通过DMA被传输到系统内存。

以太网外设也包括一个SMI,用于和外部PHY通讯。通过一组寄存器的配置,用户可以选择MAC和DMA控制器的不同模式和功能

当使用以太网时,AHB时钟必须至少25MHZ。下面试ETH的框图

区域1:我们称为SMI接口,用于配置外部PHY芯片区域2:是数据交换接口,也就是上面我们说的MII接口和RMII接口 关于AHB的连接信息

2、数据接口 2.1、SMI接口

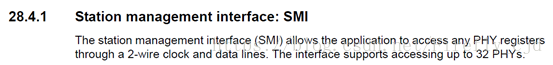

28.4.1 站管理接口:SMI站管理接口允许任何PHY寄存器请求通过2线时钟和数据线。这个接口支持最多到32个PHY ![E7L~HQYNFDD0~}K%[~]D$@9.png E7L~HQYNFDD0~}K%[~]D$@9.png](data/attachment/forum/202204/18/223438qukkjhjr1tgjlgjh.png)

应用程序可以从 32 个 PHY 中选择一个 PHY,然后从任意 PHY 包含的 32 个寄存器中选择 一个寄存器,发送控制数据或接收状态信息。任意给定时间内只能对一个 PHY 中的一个寄 存器进行寻址

MDC时钟线和MDIO 数据线在微控制器中均用作复用功能 I/O: MDC:周期性时钟,提供以最大频率 2.5 MHz 传输数据时的参考时序。MDC 的最短高电平时间和最短低电平时间必须均为 160 ns。MDC 的最小周期必须为 400 ns。在空闲状态下,SMI 管理接口将 MDC 时钟信号驱动为低电平 MDIO:数据输入/输出比特流,用于通过 MDC 时钟信号向/从 PHY 设备同步传输状态信息

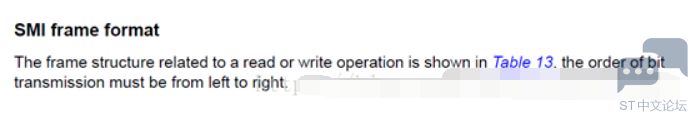

SMI帧结构 给出了读操作和写操作帧结构,位传输必须要求从左到右,SMI的帧格式,读写操作

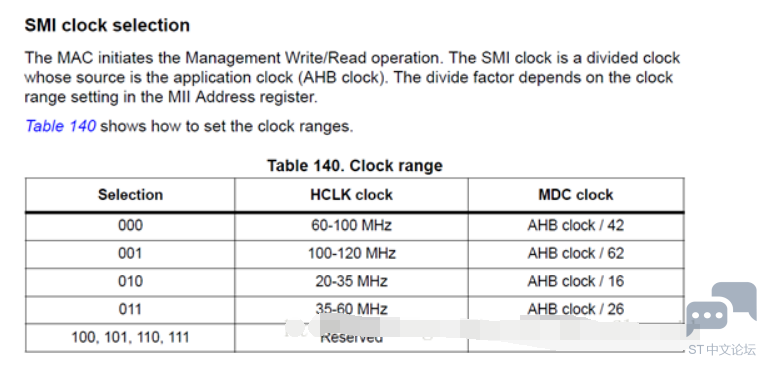

SMI时钟选择 MAC 启动管理写/读操作。SMI 时钟是一个分频时钟,其时钟源为应用时钟(AHB 时钟)。 分频系数取决于 MII 地址寄存器中设置的时钟范围。 2.2、MII接口

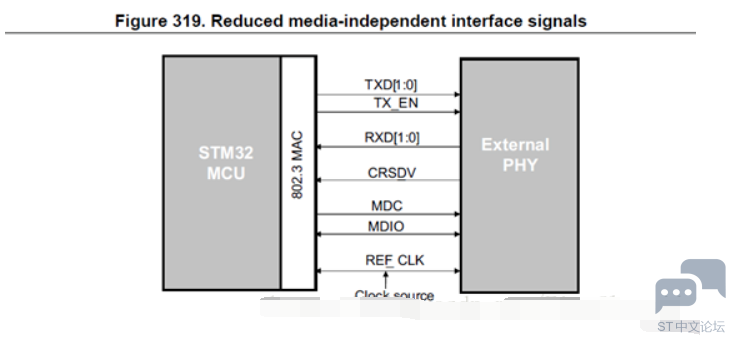

介质独立接口 (MII) 定义了 10 Mbit/s 和 100 Mbit/s 的数据传输速率下 MAC 子层与 PHY 之 间的互连。

剩余的部分基本都是管脚介绍

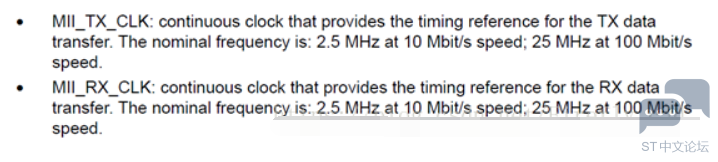

MII_TX_CLK:连续时钟信号。该信号提供进行 TX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz MII_RX_CLK:连续时钟信号。该信号提供进行 RX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz

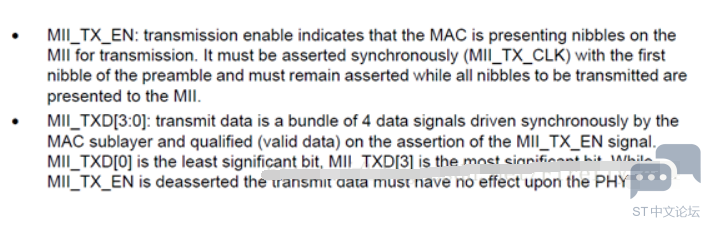

MII_TX_EN:发送使能信号。该信号表示 MAC 当前正针对 MII 发送半字节。该信号必须与报头的前半字节进行同步 (MII_TX_CLK),并在所有待发送的半字节均发送到 MII时必须保持同步 MII_TXD[3:0]:数据发送信号。该信号是 4 个一组的数据信号,由 MAC 子层同步驱动,在MII_TX_EN 信号有效时才为有效信号(有效数据)。MII_TXD[0] 为最低有效位,MII_TXD[3] 为最高有效位。禁止MII_TX_EN 时,发送数据不会对 PHY 产生任何影响

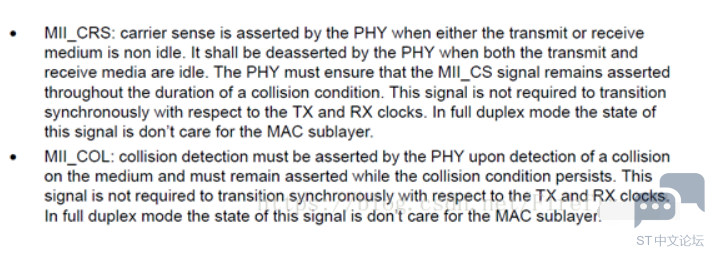

MII_CRS:载波侦听信号。当发送或接收介质处于非空闲状态时,由 PHY 使能该信号。发送和接收介质均处于空闲状态时,由 PHY 禁止该信号。PHY 必须确保MII_CS 信号在冲突条件下保持有效状态。该信号无需与 TX 和 RX 时钟保持同步。在全双工模式下,该信号没意义 MII_COL:冲突检测信号。检测到介质上存在冲突后,PHY 必须立即使能冲突检测信号,并且只要存在冲突条件,冲突检测信号必须保持有效状态。该信号无需与 TX 和 RX 时钟保持同步。在全双工模式下,该信号没意义 ![]X](RKW[U@OPJTXH84I497L.png ]X](RKW[U@OPJTXH84I497L.png](data/attachment/forum/202204/18/223436gbj8ggg2j2moob3m.png)

MII_RXD[3:0]:数据接收信号。该信号是 4 个一组的数据信号,由 PHY 同步驱动,在MII_RX_DV 信号有效时才为有效信号(有效数据)。MII_RXD[0] 为最低有效位,MII_RXD[3] 为最高有效位。当 MII_RX_DV 禁止、MII_RX_ER 使能时,特定的MII_RXD[3:0] 值用于传输来自 PHY 的特定信息(请参见表 142) MII_RX_DV:接收数据有效信号。该信号表示 PHY 当前正针对 MII 接收已恢复并解码的半字节。该信号必须与恢复帧的头半字节进行同步(MII_RX_CLK),并且一直保持同步到恢复帧的最后半字节。该信号必须在最后半字节随后的第一个时钟周期之前禁止。为了正确地接收帧,MII_RX_DV 信号必须在时间范围上涵盖要接收的帧,其开始时间不得迟于 SFD 字段出现的时间

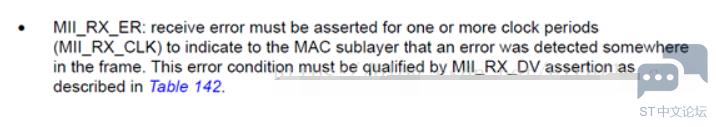

MII_RX_ER:接收错误信号。该信号必须保持一个或多个周期(MII_RX_CLK),从而向MAC 子层指示在帧的某处检测到错误。该错误条件必须通过 MII_RX_DV 验证,如表142 所示 表141.TX 接口信号编码 ![K6TTY)}IVH]M@S@YJC8IRCA.png K6TTY)}IVH]M@S@YJC8IRCA.png](data/attachment/forum/202204/18/223435iwrjlfwasywqs4l7.png)

表142. RX 接口信号编码

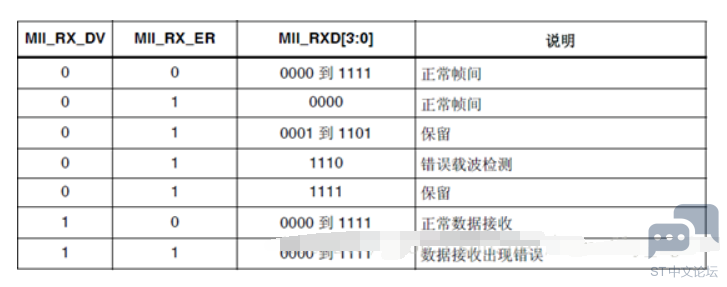

要生成 TX_CLK 和 RX_CLK 时钟信号,必须向外部 PHY 提供 25MHz 时钟,如图 所 示。除了使用外部 25 MHz 石英晶体提供该时钟,还可以通过 STM32F20xx 微控制器的 MCO引脚输出该信号。这种情况下,必须对 PLL 倍频进行配置,以通过 25 MHz 外部石英晶体在 MCO 引脚上获得所需频率。 ![(YH`N%IZSF]IO@Y3`E7Y3BQ.png (YH`N%IZSF]IO@Y3`E7Y3BQ.png](data/attachment/forum/202204/18/223435wpgbaevgzpy5abzn.png)

2.3、RMII接口 Reducedmedia-independent interface: RMII 翻译:精简介质独立接口:RMII

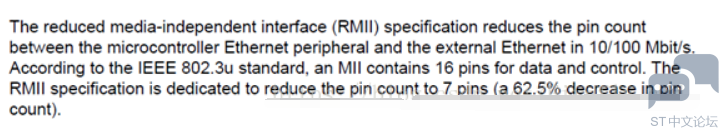

精简介质独立接口 (RMII) 规范降低了 10/100 Mbit/s 下微控制器以太网外设与外部 PHY 间的 引脚数。根据 IEEE 802.3u 标准,MII 包括 16 个数据和控制信号的引脚。RMII 规范将引脚 数减少为 7 个(引脚数减少 62.5%) ![~PFB`TV@3[]EN4C{GDDXV]E.png ~PFB`TV@3[]EN4C{GDDXV]E.png](data/attachment/forum/202204/18/223434uq98qs8bqyy8y8qb.png)

RMII接口是MAC和PHY之间的实例化对象。这些有助于MAC的MII接口转化为RMII接口。RMII接口具有以下特点 10-Mbit/s和100-Mbit/s 的运行速率 参考时钟必须是 50 MHz 相同的参考时钟必须从外部提供给 MAC 和外部以太网PHY 它提供了独立的 2 位宽(双位)的发送和接收数据路径 这里时钟管脚比MII接口少, 又一个非常重要的点,那就是时钟源必须是50MHZ 时钟源

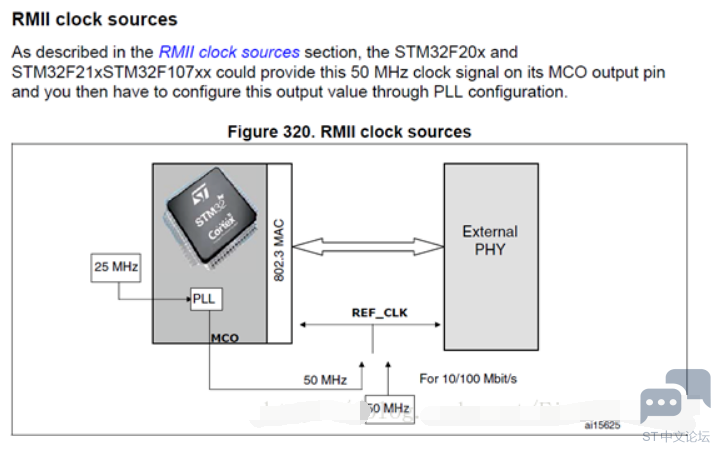

使用外部 50 MHz 时钟驱动 PHY 或使用嵌入式 PLL 生成 50 MHz 频率信号来驱动 PHY 2.5、MII和RMII的接口选择

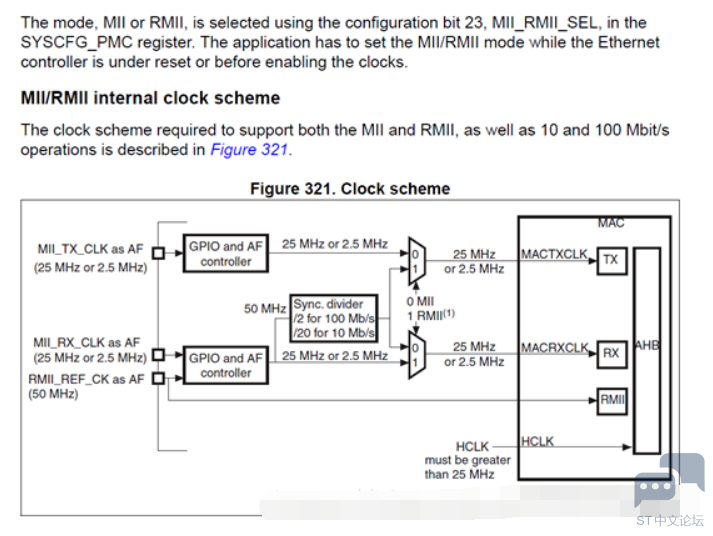

使用 SYSCFG_PMC 寄存器中的配置位 23 MII_RMII_SEL 选择 MII 或 RMII 模式。以太网控 制器处于复位模式或使能时钟前,应用程序必须设置 MII/RMII 模式 MII/RMII内部时钟方案 支持 MII 和 RMII 以及 10 和 100 Mbit/s 运行所需的时钟方案如图 321所示 ![AQ`4]JGVO%X1X%(9M0S@2.png AQ`4]JGVO%X1X%(9M0S@2.png](data/attachment/forum/202204/18/223433z3wq3cqq7q37mw37.png)

1. 通过 SYSCFG_PMC 寄存器中的位 23 MII_RMII_SEL 控制 MII/RMII 选择

要节省引脚,需在同一个 GPIO 引脚上复用 RMII_REF_CK 和 MII_RX_CLK 这两个输入时 钟信号。 3、MAC 802.3 跳过 4、DMA控制器操作

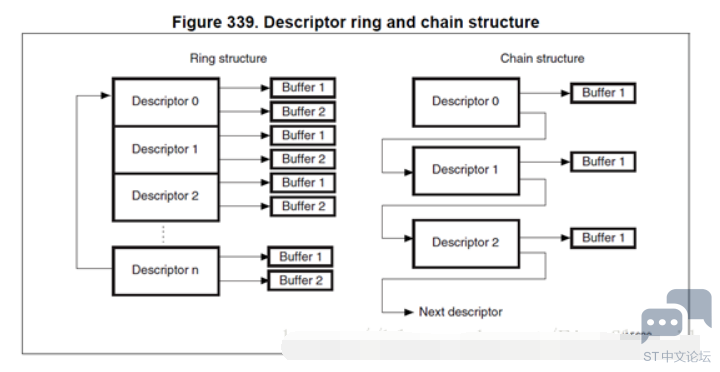

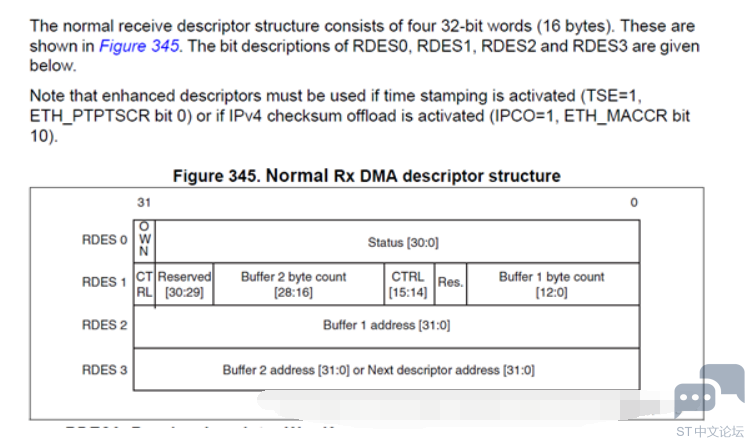

28.6 以太网功能说明:DMA控制器操作 DMA具有自主的发送和接收引擎,还有一个 CSR(控制和状态寄存器)空间。发送引擎将数据从系统存储器传送到 Tx FIFO,而接收引擎将数据从 Rx FIFO 传送到系统存储器。控制器(也就是DMA)利用描述符有效的将数据从源地址移动到目的地,很小的CPU干预。DMA 专为面 向包的数据传送(如以太网中的帧)而设计。控制器可以编程去打断CPU,例如完成帧发送和接收传送操作时以及其它正常/错误条件下。DMA 和STM32F20x 和STM32F21x 通过以下两种数 据结构进行通信: 控制和状态寄存器 (CSR) 描述符列表和数据缓冲区

控制和状态寄存器在28.8节第895页。细节的介绍和描述在875页。

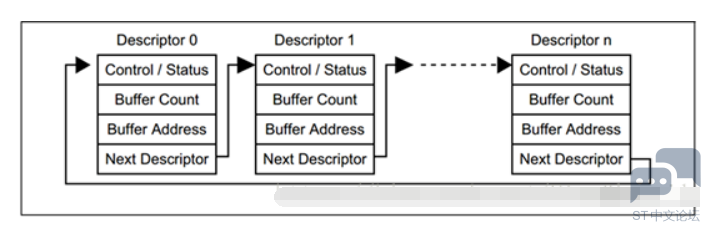

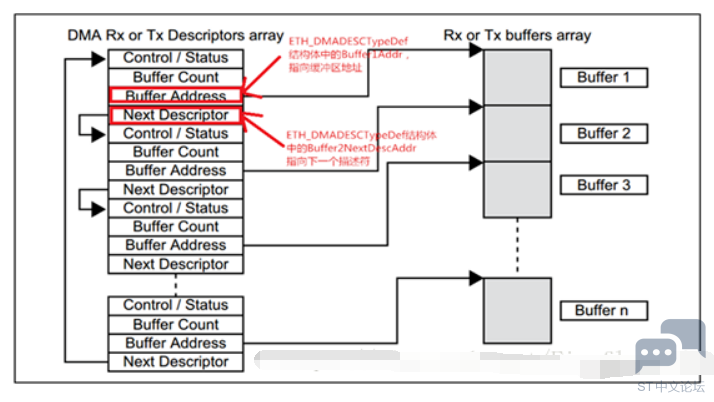

DMA控制器发送接收到的数据帧到STM32F20x 的接收缓存中和STM32F21x 存储器中,也可以发送数据帧从STM32F20x 和STM32F21x 的存储器的发送缓存。位于STM32F20x 和STM32F21x存储器的描述符指向这些缓存。这里有两个描述符列表:一个用于接收,一个用于发送。两个列表的基地址被写入DMA寄存器3和4。描述符是前向列表(无论是隐式还是显式)。最后一个描述符会指向第一个描述符,形成环形结构。显 式链接的描述完成,通过配置在接收和发送描述符(RDES1[14] 和 TDES0[20])的第二个地址连接。描述符列表位于主机的物理存储空间。每一个描述符最多可以指向两个缓冲区。这样可以使用连个物理缓冲区代替存储器中两个连续的缓冲区。数据缓冲区位于主机的物理存储空间,通常由整个帧或部分帧组成,但不会超过单个帧。缓冲区中仅包含数据。缓冲区的住哪个台保存在描述符中。一个单一的描述符不能跨越多个帧。当帧结束时,DMA会跳到下一帧缓冲区。数据连接可以被使能或终止。描述符环形和链式结构显示在图片339。

注意:这里说的描述符是软件,不是硬件,其实就是个结构体。图片的左边是环形结构,右图是链式结构(关于环形和链式结构,英文直译这样,这个地方比较乱,不管这些,我们就使用上图右边的结构,链式结构) ![F[]UQGA39_BTAL0(UOG`}32.png F[]UQGA39_BTAL0(UOG`}32.png](data/attachment/forum/202204/18/223431ovoiohtkz9iig88i.png)

使用DMA传送进行的初始化 MAC的初始化步骤如下: 1.对 ETH_DMABMR 执行写操作以设置 STM32F20x 总线访问参数 2.对 ETH_DMAIER 寄存器执行写操作以屏蔽不必要的中断源 3.软件驱动器创建发送和接收描述符列表。随后对 ETH_DMARDLAR 和 ETH_DMATDLAR 寄存器执行写操作,为 DMA 提供各列表的起始地址 4.对 MAC 寄存器 1、2 和 3 执行写操作以选择所需的过滤选项 5.对 MAC ETH_MACCR 寄存器执行写操作以配置和使能发送与接收工作模式。可根据自 动协商结果将 PS 位与 DM 位置 1(读取自 PHY) 6.对 ETH_DMAOMR 寄存器执行写操作,将位 13 和位 1 置 1 以启动发送和接收 7.发送与接收引擎进入运行状态,并尝试从相应描述符列表中获取描述符。这两个引擎随后开始处理接收和发送操作。发送和接收处理过程彼此独立,可单独进行启动或停止 5、DMA描述符 ST提供的以太网驱动库stm32f2x7_eth.c中使用是链接结构,链接结构如下

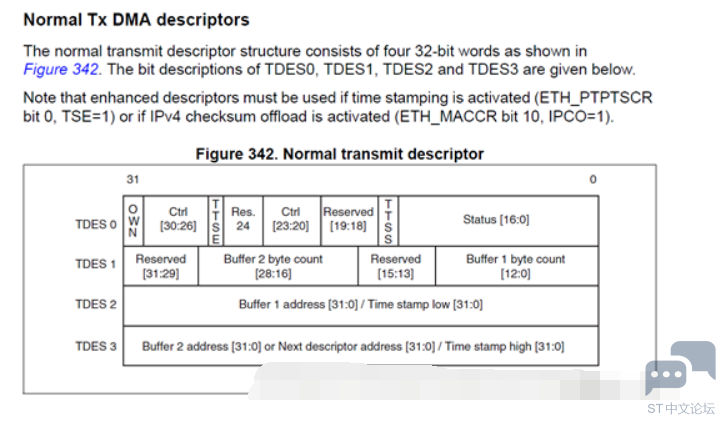

描述符注意事项: 1.一个以太网数据包可以跨越一个或多个DMA描述符 2.一个DMA描述符只能用于一个以太网数据包 3.DMA描述符列表中的最后一个描述符指向第一个,形成链式结构! 描述符有分为增强描述符和常规描述符,我们只讲常规描述符!因为我们的网络例程只使用到了常规描述符。常规描述符和增强描述符的结构体成员变量不同。常规描述符只使用了描述符的前4个成员变量 常规描述符和增强描述符又有发送描述符和接收描述符两种,下图是常规Tx DMA描述符:

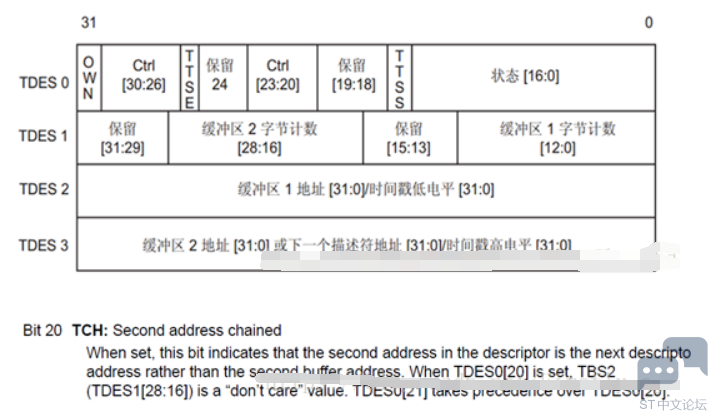

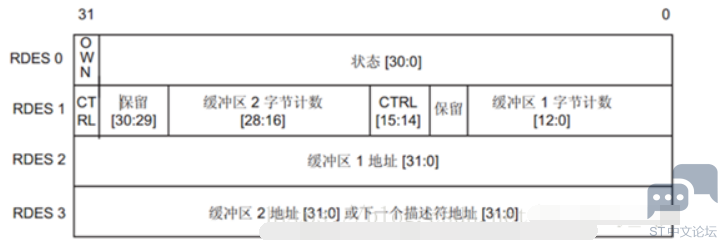

位 20 TCH:链接的第二个地址 (Second address chained) 该位置 1 时,表示描述符中的第二个地址是下一个描述符地址,而非第二个缓冲区地址。TDES0[20] 置 1 时,TBS2 (TDES1[28:16])为“无 关”值。TDES0[21] 优 先 级 高 于TDES0[20] 常规Tx DMA描述符中TDES0的bit20用来表示描述符中的第二个地址是用来保存下一个描述符地址还是第二个缓冲区的地址,这点很重要! 常规Rx DMA描述符如下

常规Tx DMA描述符和常规Rx DMA描述符的成员变量的意义不同! 常规Rx DMA描述符中RDES1的bit14用来表示描述符中的第二个地址是用来保存一个描述符地址还是第二个缓冲区的地址 ST官方以太网库stm32f2x7中使用链接结构的DMA描述符,那么在以太网描述符结构体ETH_DMADESCTypeDef中Buffer1Addr就是缓冲区的地址,Buffer2NextDescAddr就是下一个描述符的地址,如下图。

5、网络中断 ![NTIV~7V)9_WX%A[J9PF}I]B.png NTIV~7V)9_WX%A[J9PF}I]B.png](data/attachment/forum/202204/18/223429v5r233h293h833b2.png)

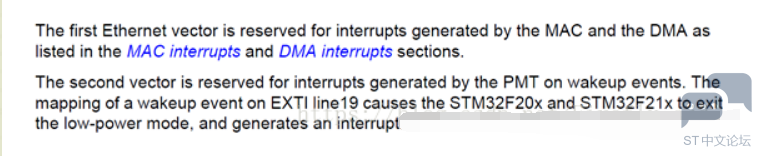

网络中断向量:一个用于正常的网络操作,另一个当它映射到EXIT线路19的时候,用于以太网唤醒事件(带有唤醒帧或魔术数据包检测)

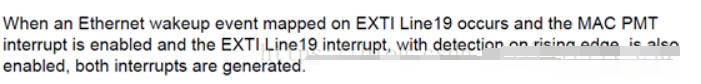

第一个网络中断保留为MAC和DMA产生的中断,正如在MAC中断和DMA中断部分。 第二个中断保留为唤醒事件时PMT产生的中断。唤醒事件对EXIT线路19的映射是造成STM32F20X和STM32F21X退出低功耗模式,并且产生中断。

当映射到EXIT线路19的以太网唤醒事件发生和,MACPMT中断使能并且有一个上升沿的EXIT线路19中断也被使能,他们都能唤醒中断

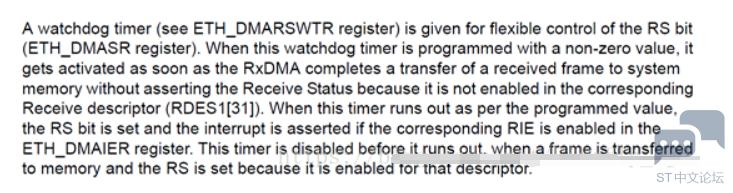

可使用看门狗定时器(请参见 ETH_DMARSWTR 寄存器)灵活控制 RS 位(ETH_DMASR 寄存器)。当此看门狗定时器使用非零值编程时,看门狗定时器激活,只要RXDMA完成发送一个接收的数据帧到系统存储,在没有触发接收状态,因为它不是使能的在相应的接收描述符(RDES1[31])(也就是:未在相应接收描述符 (RDES1[31]) 使能接收状态)。当定时器按照编程值运行时,RS位被置1并且中断发生,如果ETH_DMAIER寄存器中相应位使能。看门狗定时失效在运行前,当数据帧被发送到内存,并且RS置1,因为定时器被使能为描述符。 ![]KKZEIQBF35~]K61J`[RVBQ.png ]KKZEIQBF35~]K61J`[RVBQ.png](data/attachment/forum/202204/18/223428tndts1mhggaazugd.png)

注意: 读取 PMT 控制和状态寄存器会自动将接收的唤醒帧和接收的魔术数据包 PMT 中断标志清零。 但是,由于用于这些标志的寄存器位于 CLK_RX 域,因此在固件能发现此更新前可能有显著 的延迟。当 RX 时钟很慢(在 10 Mbit 模式)和当 AHB 总线为高频时,该延迟会特别长。 由于从 PMT 到 CPU 的中断请求基于 CLK_RX 域中的相同寄存器,所以即使在读取 PMT_CSR 之后,CPU 也可能错误地第二次调用中断例程。因此,可能需要固件轮询接收的 唤醒帧和接收的魔术数据包位,并仅在发现它们都为‘0’时退出中断服务程序。 |

实战经验 | Keil工程使用NEAI库的异常问题

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

微信公众号

微信公众号

手机版

手机版