.png) STMCU小助手

发布时间:2022-4-19 23:00

STMCU小助手

发布时间:2022-4-19 23:00

|

1、IIC定义 IIC 即Inter-Integrated Circuit(集成电路总线),这种总线类型是由飞利浦半导体公司(后被NXP收购)在八十年代初设计出来的一种简单、双向、二线制、同步串行总线,主要是用来连接整体电路(ICS) ,IIC是一种多向控制总线,也就是说多个芯片可以连接到同一总线结构下,同时每个芯片都可以作为实时数据传输的控制源。多主多从的通讯协议。 下文将结合NXP官方的IIC手册讲解IIC协议。下载链接见文末。

I2C串行总线一般有两根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上。速率最高400Kbit/s。

在1998年的修订中增加了高速模式,速率高达3.4Mbit/s。(这里不讲,只说快速模式)。

2、IIC协议规范 2.1 SDA和SCL信号

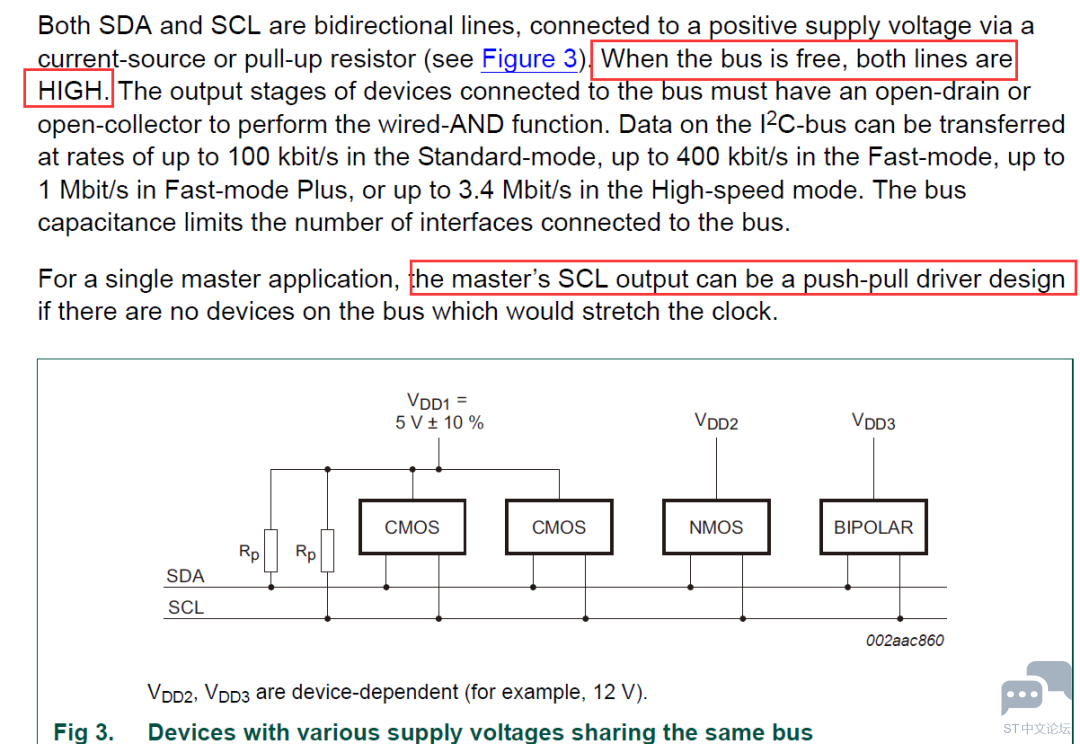

连接到总线的器件输出级必须是漏极开路或集电极开路才能执行线与的功能,当总线空 闲时这两条线路都是高电平。SDA 和SCL 都是双向线路都通过一个电流源或上拉电阻连接到正的电源电压。一般情况下我们都采用上拉电阻的方式 2.2 数据有效性

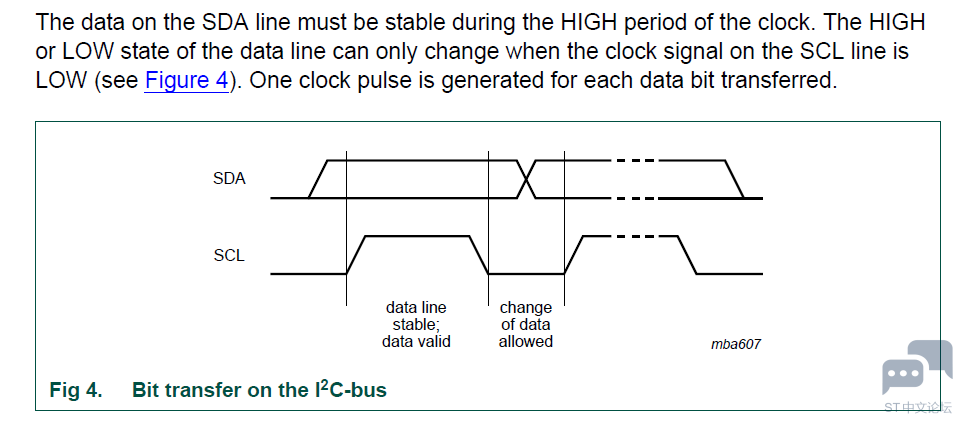

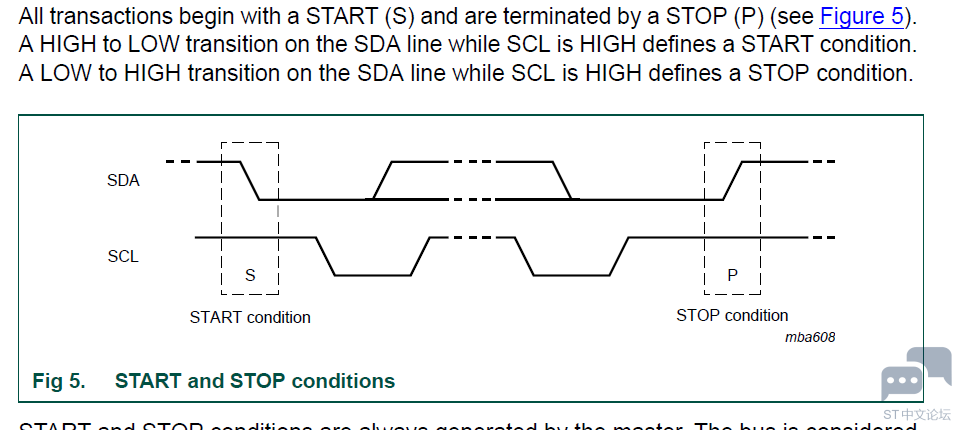

在SCL高电平的时候采样,也就是有效。低电平的时候切换数据 2.3 开始和结束信号 起始条件:SCL线是高电平时,SDA线从高电平向低电平切换。 停止条件:SCL线是高电平时,SDA线从低电平向高电平切换。

动画展示启动信号

代码实现

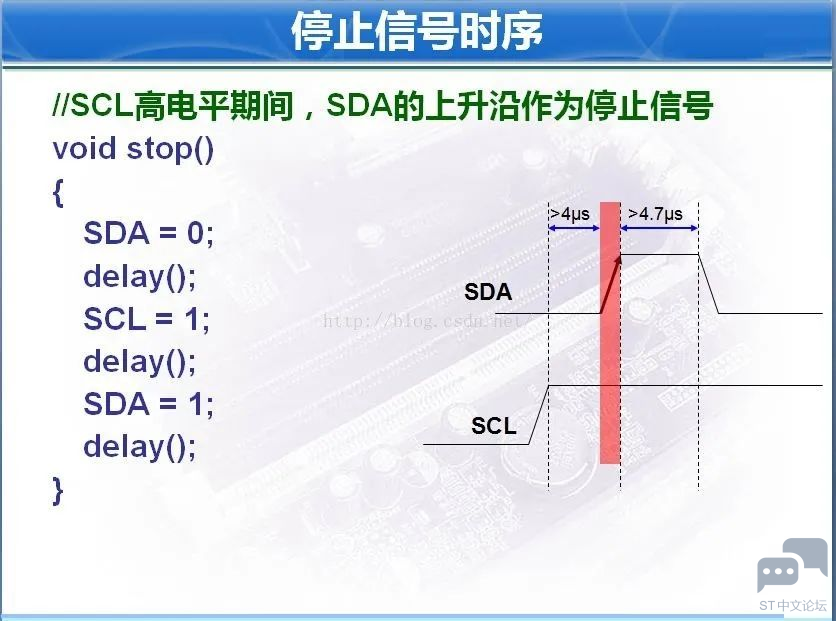

结束信号时类似的方式(不是动图)

代码实现

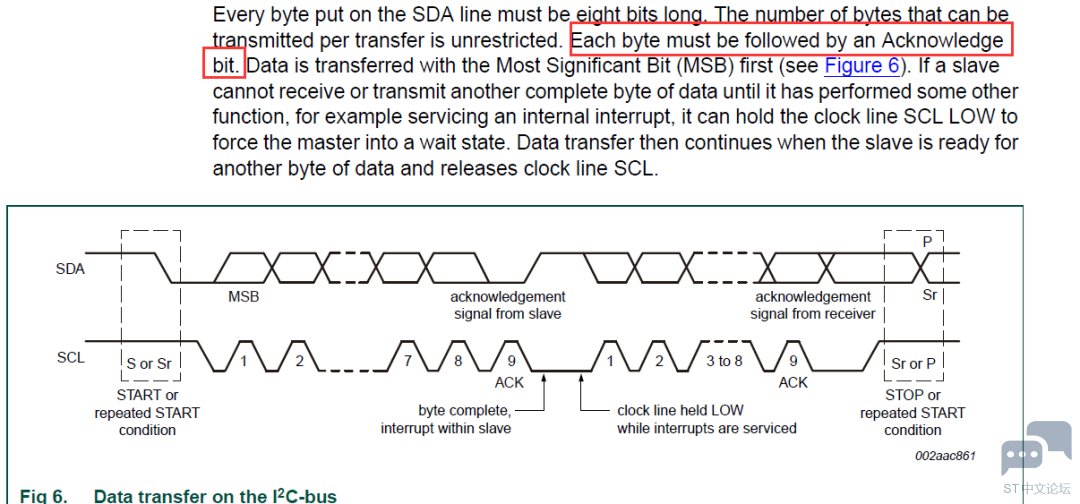

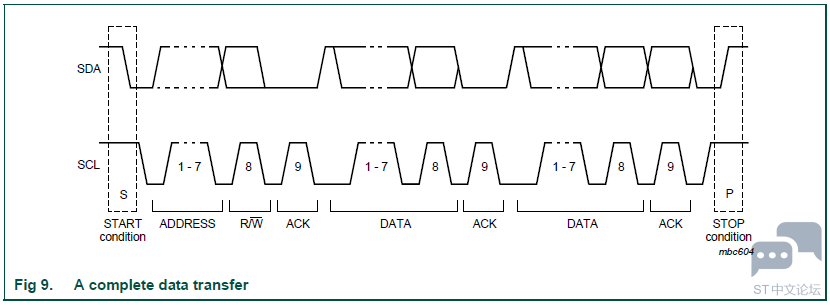

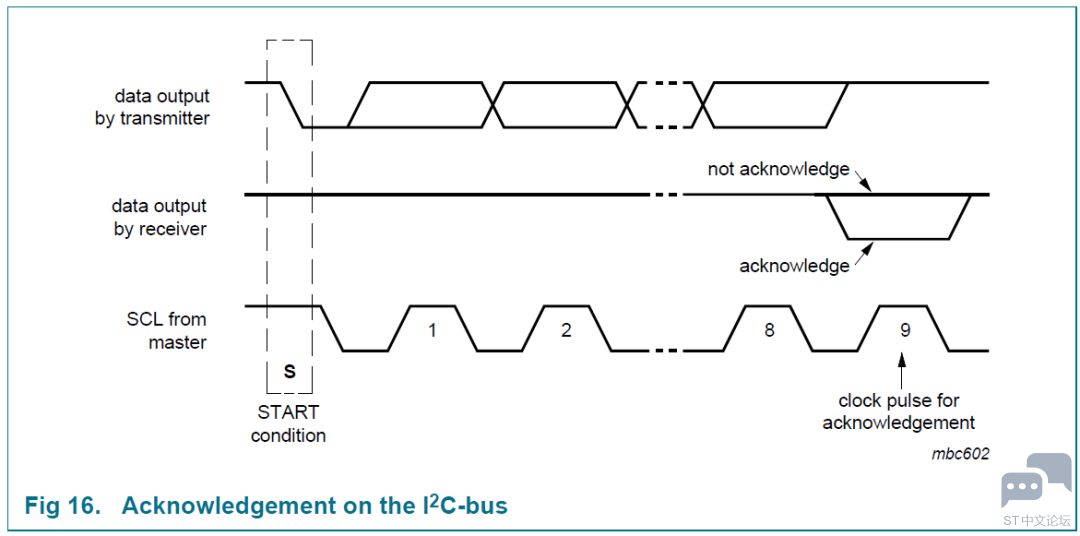

2.4 字节格式 SDA数据线上的每个字节必须是8位,每次传输的字节数量没有限制。每个字节后必须跟一个响应位(ACK)。首先传输的数据是最高位(MSB),SDA上的数据必须在SCL高电平周期时保持稳定,数据的高低电平翻转变化发生在SCL低电平时期。

每一个字节后面跟着一个ACK,有ACK就可以继续写或读。NACK,就停止 ACK:主机释放总线,传输完字节最后1位后的SCL的高电处,从机拉低电平。 NACK:主机释放总线,传输完字节最后1位后的SCL的高电处,从机无响应,总线为高电平。 动画描述写入的过程

代码实现

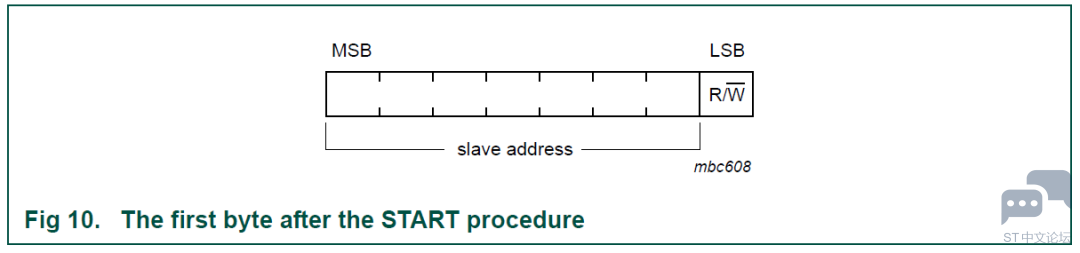

2.5 从机地址和读写位 开始信号—>地址—>读写位—>ACK—>数据—>ACK.............—>停止位

这里只说7位地址,前7位为地址,最后一位为读写位,1表示读操作,0表示写操作

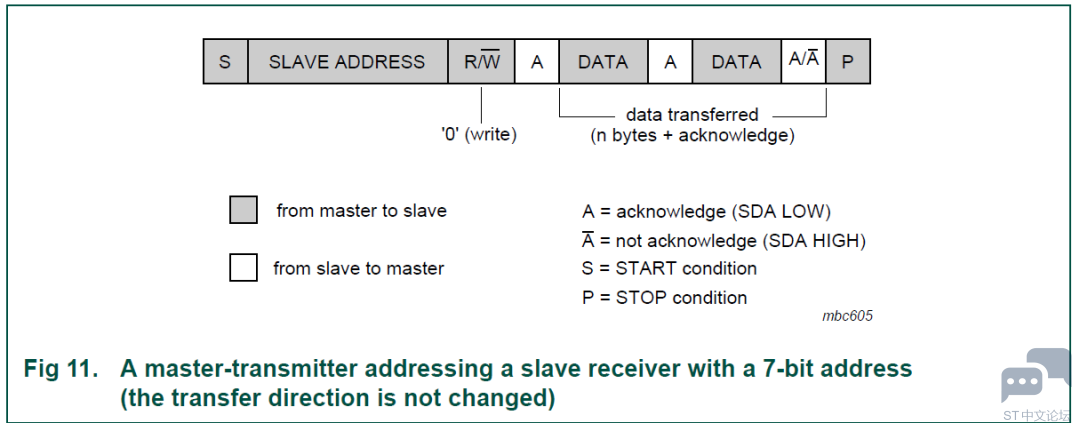

主机发给从机数据,也就是写,没有数据转向时

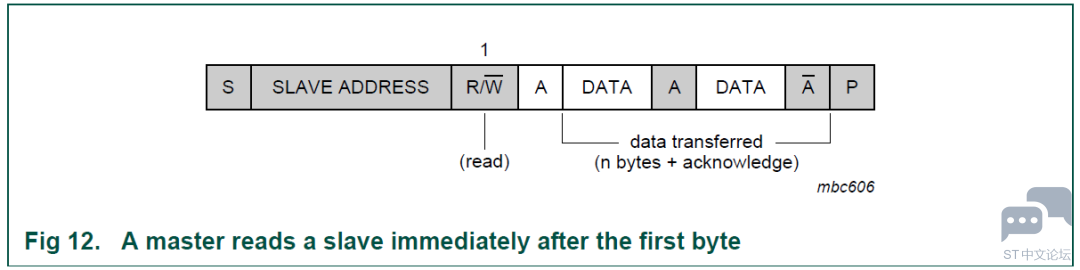

主机立即读从机数据,从第一个字节

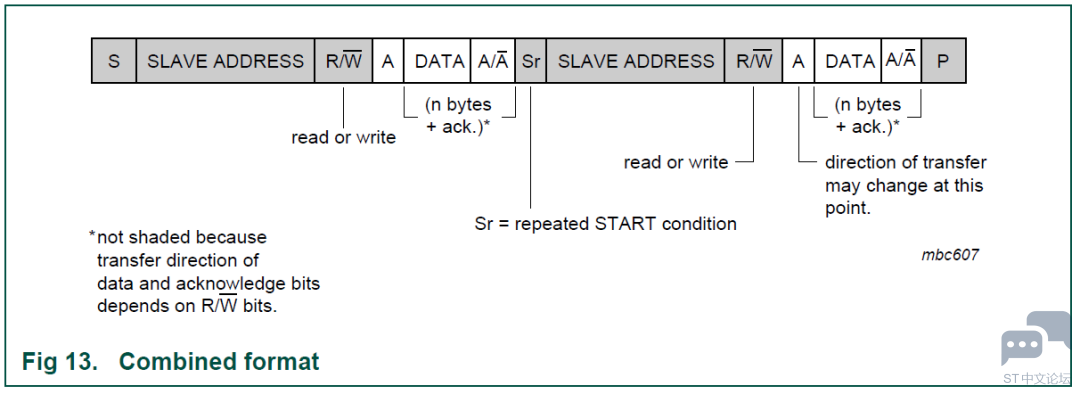

(Combined)综合数据格式

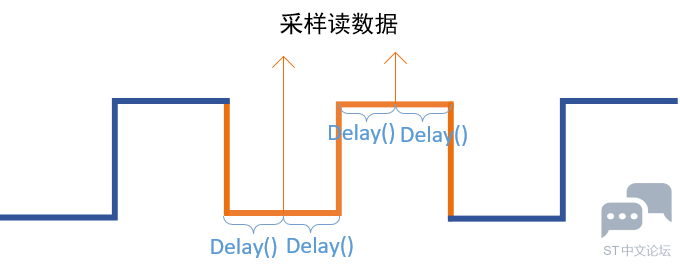

3、计算IIC的频率 通信频率由主机掌控,也就是代码中的延时函数决定的 从上面,我们得知最高速为400Kbit/s。我们设计300Kbit/s。

速率300Kbit/s,对应周期1/300ms=10/3us≈3us,4分频就是3/4us。 我们使用的延时是,1/120MHZ*3*30 =3/4us 也就是频率是300Kbit/s 和SPI类似,时钟下降沿时,数据转换,时钟上升沿时,采样数据。也就是时钟高电平数据有效。

4、PCF8536 4.1 Acknowledge 这个地方能看到关于2.4节关于ACK和NACk的说明。

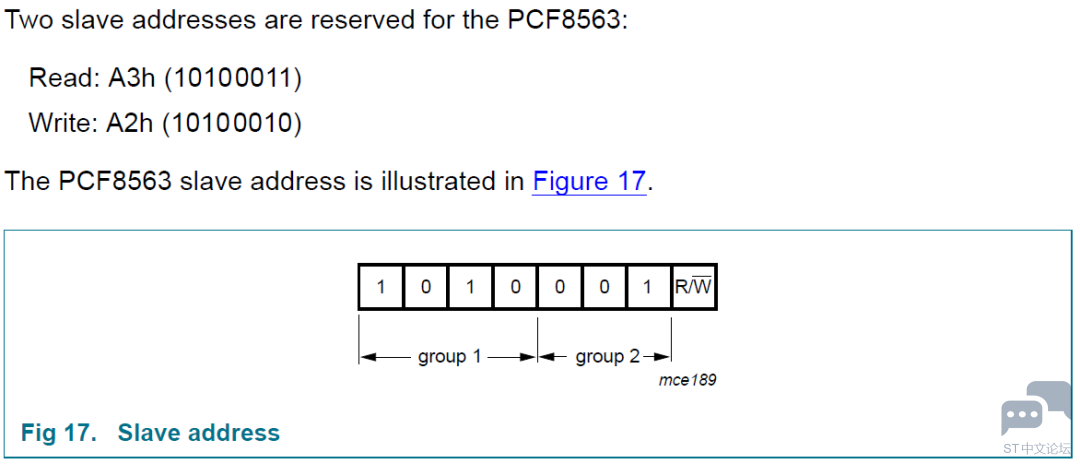

4.2 Addressing 这里直接给出读地址和写地址,也就是最后一位的区别

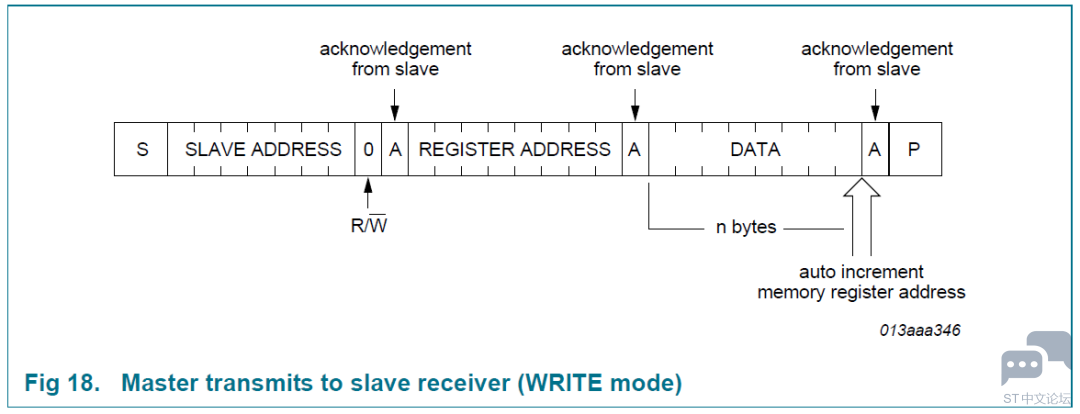

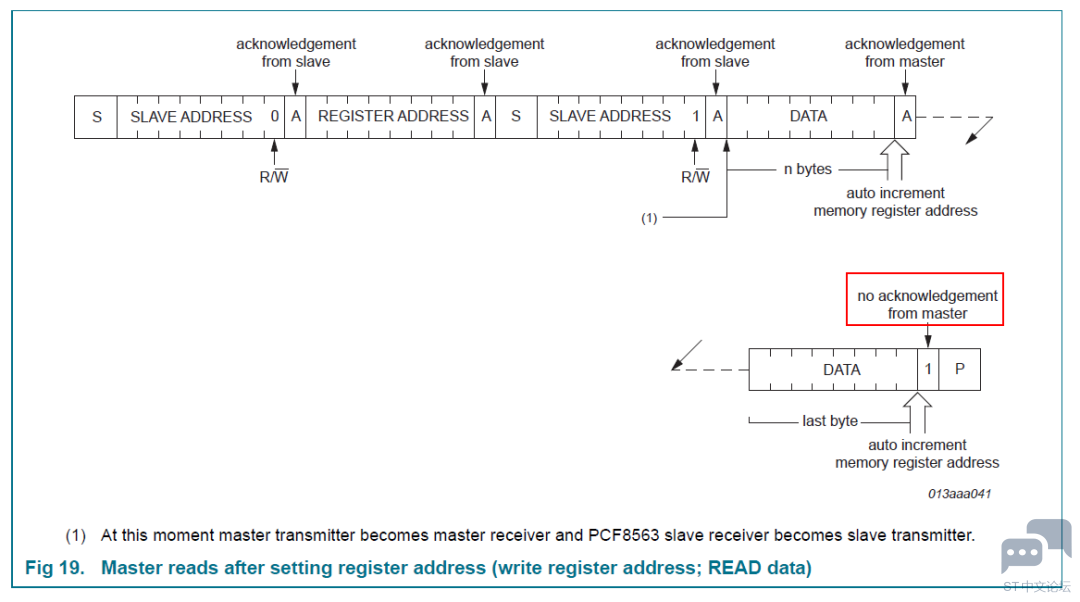

4.3 读写时序 其实就是按照IIC协议的 读指定器件的指定寄存器

主机设置完寄存器地址之后,再去读写 注意:读取多个字节,最后一个字节的回包应该是NACK

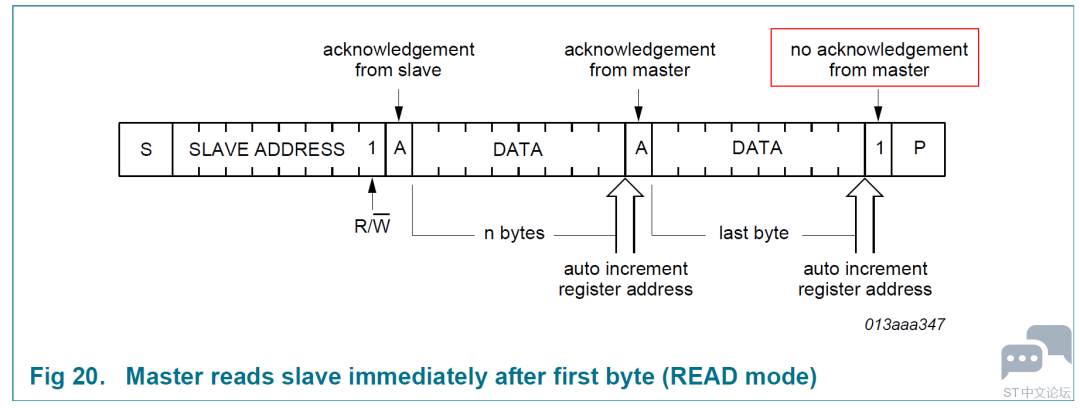

主机立即从机第一个字节读取 注意:读取多个字节,最后一个字节的回包应该是NACK

|

实战经验 | Keil工程使用NEAI库的异常问题

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

微信公众号

微信公众号

手机版

手机版