.png) STMCU小助手

发布时间:2022-6-14 14:52

STMCU小助手

发布时间:2022-6-14 14:52

|

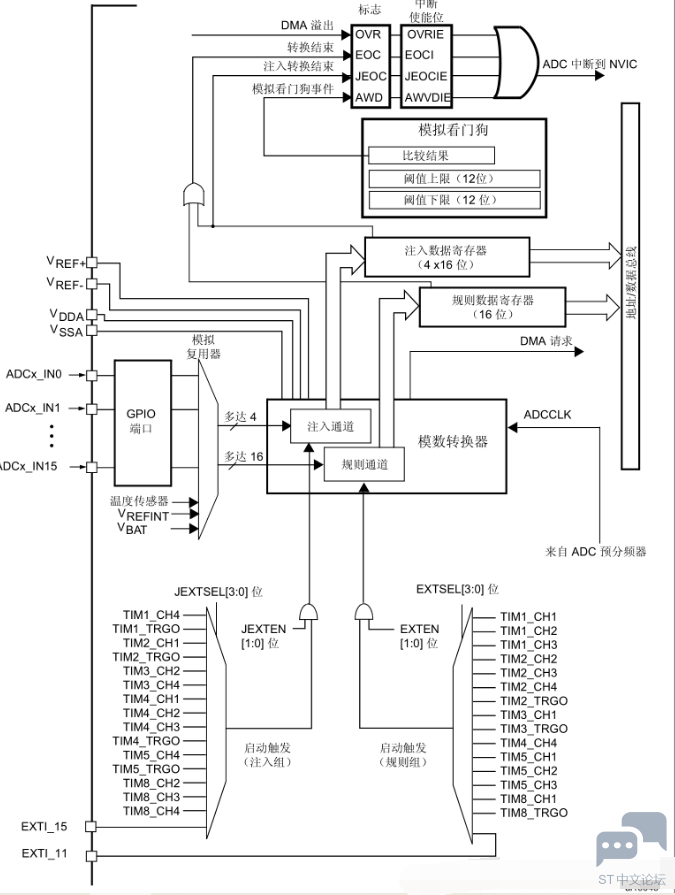

01. ADC简介 12 位 ADC 是逐次趋近型模数转换器。它具有多达 19 个复用通道,可测量来自 16 个外部源、两个内部源和 V BAT 通道的信号。这些通道的 A/D 转换可在单次、连续、扫描或不连续采样模式下进行。ADC 的结果存储在一个左对齐或右对齐的 16 位数据寄存器中。ADC 具有模拟看门狗特性,允许应用检测输入电压是否超过了用户自定义的阈值上限或下限。 02. ADC主要特性 ● 可配置 12 位、10 位、8 位或 6 位分辨率 ● 在转换结束、注入转换结束以及发生模拟看门狗或溢出事件时产生中断 ● 单次和连续转换模式 ● 用于自动将通道 0 转换为通道“n”的扫描模式 ● 数据对齐以保持内置数据一致性 ● 可独立设置各通道采样时间 ● 外部触发器选项,可为规则转换和注入转换配置极性 ● 不连续采样模式 ● 双重/三重模式(具有 2 个或更多 ADC 的器件提供) ● 双重/三重 ADC 模式下可配置的 DMA 数据存储 ● 双重/三重交替模式下可配置的转换间延迟 ● ADC 转换类型(参见数据手册) ● ADC 电源要求:全速运行时为 2.4 V 到 3.6 V,慢速运行时为 1.8 V ● ADC 输入范围:V REF— V IN V REF+ ● 规则通道转换期间可产生 DMA 请求 注意: V REF— 如果可用(取决于封装),则必须将其连接到 V SSA 。 03. ADC功能说明 框图

![5BR_]HTDOCDA~CLS9RXR.png 5BR_]HTDOCDA~CLS9RXR.png](data/attachment/forum/202206/14/145343tjeswgjbvpg7g4ja.png)

04. ADC开关控制 可通过将 ADC_CR2 寄存器中的 ADON 位置 1 来为 ADC 供电。首次将 ADON 位置 1 时,会将 ADC 从掉电模式中唤醒。 SWSTART 或 JSWSTART 位置 1 时,启动 AD 转换。 可通过将 ADON 位清零来停止转换并使 ADC 进入掉电模式。在此模式下,ADC 几乎不耗电(只有几 μA) 05. ADC时钟 ADC 具有两个时钟方案: ● 用于模拟电路的时钟:ADCCLK,所有 ADC 共用 此时钟来自于经可编程预分频器分频的 APB2 时钟,该预分频器允许 ADC 在 f PCLK2 /2、/4、/6 或 /8 下工作。有关 ADCCLK 的最大值,请参见数据手册。 ● 用于数字接口的时钟(用于寄存器读/写访问) 此时钟等效于 APB2 时钟。可以通过 RCC APB2 外设时钟使能寄存器 (RCC_APB2ENR)分别为每个 ADC 使能/禁止数字接口时钟。 06. 通道选择 有 16 条复用通道。可以将转换分为两组:规则转换和注入转换。每个组包含一个转换序列,该序列可按任意顺序在任意通道上完成。例如,可按以下顺序对序列进行转换:ADC_IN3、ADC_IN8、ADC_IN2、ADC_IN2、ADC_IN0、ADC_IN2、ADC_IN2、ADC_IN15。 ● 一个 规则转换组最多由 16 个转换构成。必须在 ADC_SQRx 寄存器中选择转换序列的规则通道及其顺序。规则转换组中的转换总数必须写入 ADC_SQR1 寄存器中的 L[3:0] 位。 ● 一个 注入转换组最多由 4 个转换构成。必须在 ADC_JSQR 寄存器中选择转换序列的注入通道及其顺序。注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位 如果在转换期间修改 ADC_SQRx 或 ADC_JSQR 寄存器,将复位当前转换并向 ADC 发送一个新的启动脉冲,以转换新选择的组。 温度传感器、V REFINT 和 V BAT 内部通道 ● 对于 STM32F40x 和 STM32F41x 器件,温度传感器内部连接到通道 ADC1_IN16。内部参考电压 VREFINT 连接到 ADC1_IN17。 ● 对于 STM23F42x 和 STM32F43x 器件,温度传感器内部连接到与 VBAT 共用的通道ADC1_IN18。一次只能选择一个转换(温度传感器或 VBAT)。同时设置了温度传感器和 VBAT 转换时,将只进行 VBAT 转换。 内部参考电压 VREFINT 连接到 ADC1_IN17。 V BAT 通道连接到通道 ADC1_IN18。该通道也可转换为注入通道或规则通道。 注意: 温度传感器、 V REFINT 和 V BAT 通道只在主 ADC1 外设上可用。 07. 转换模式 单次转换模式 在单次转换模式下,ADC 执行一次转换。CONT 位为 0 时,可通过以下方式启动此模式: ● 将 ADC_CR2 寄存器中的 SWSTART 位置 1(仅适用于规则通道) ● 将 JSWSTART 位置 1(适用于注入通道) ● 外部触发(适用于规则通道或注入通道) 完成所选通道的转换之后: ● 如果转换了规则通道: — 转换数据存储在 16 位 ADC_DR 寄存器中 — EOC(转换结束)标志置 1 — EOCIE 位置 1 时将产生中断 ● 如果转换了注入通道: — 转换数据存储在 16 位 ADC_JDR1 寄存器中 — JEOC(注入转换结束)标志置 1 — JEOCIE 位置 1 时将产生中断 然后,ADC 停止。 连续转换模式 在连续转换模式下,ADC 结束一个转换后立即启动一个新的转换。CONT 位为 1 时,可通过外部触发或将 ADC_CR2 寄存器中的 SWSTRT 位置 1 来启动此模式(仅适用于规则通道)。 每次转换之后: ● 如果转换了规则通道组: — 上次转换的数据存储在 16 位 ADC_DR 寄存器中 — EOC(转换结束)标志置 1 — EOCIE 位置 1 时将产生中断 温馨提示 无法连续转换注入通道。连续模式下唯一的例外情况是,注入通道配置为在规则通道之后自动转换(使用 JAUTO 位),请参见自动注入一节 08. 时序图 ![EMK5LWHRZ3]VT_6H0[D{]}2.png EMK5LWHRZ3]VT_6H0[D{]}2.png](data/attachment/forum/202206/14/145343xor3ijnanf5a24dl.png)

09. 扫描模式 此模式用于扫描一组模拟通道。 通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后,ADC 会扫描在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的所有通道。为组中的每个通道都执行一次转换。每次转换结束后,会自动转换该组中的下一个通道。如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再次从第一个所选通道继续转换。 如果将 DMA 位置 1,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。 在以下情况下,ADC_SR 寄存器中的 EOC 位置 1: ● 如果 EOCS 位清零,在每个规则组序列转换结束时 ● 如果 EOCS 位置 1,在每个规则通道转换结束时 从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。 10. 数据对齐 ADC_CR2 寄存器中的 ALIGN 位用于选择转换后存储的数据的对齐方式。可选择左对齐和右对齐两种方式,如 图 38 和 图 39 所示 注入通道组的转换数据将减去 ADC_JOFRx 寄存器中写入的用户自定义偏移量,因此结果可以是一个负值。SEXT 位表示扩展的符号值。 对于规则组中的通道,不会减去任何偏移量,因此只有十二个位有效。 ![OCUXBJ9Me(89QUT4Q]GBR.png OCUXBJ9Me(89QUT4Q]GBR.png](data/attachment/forum/202206/14/145343qieb70vsviieggxa.png)

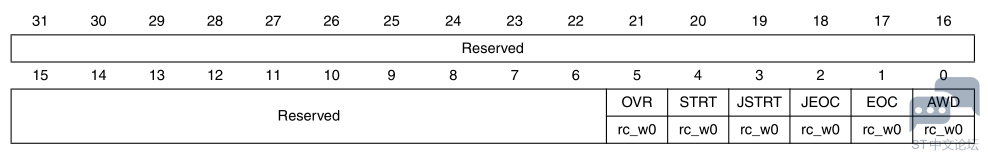

11. 寄存器 11.1ADC 状态寄存器 (ADC_SR) ADC status register 偏移地址:0x00 复位值:0x0000 0000

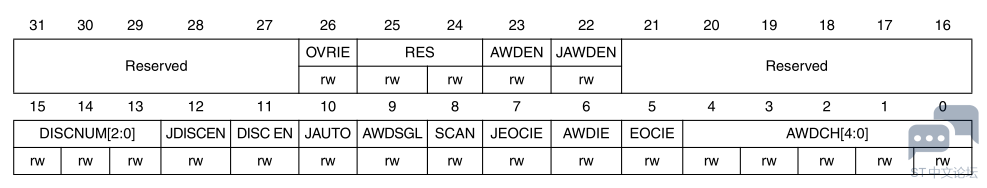

11.2 ADC 控制寄存器 1 (ADC_CR1) ADC control register 1 偏移地址:0x04 复位值:0x0000 0000

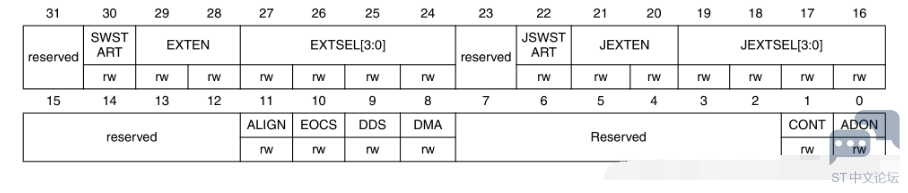

11.3 ADC 控制寄存器 2 (ADC_CR2) ADC control register 2 偏移地址:0x08 复位值:0x0000 0000

11.4 ADC 采样时间寄存器 1 (ADC_SMPR1) ADC sample time register 1 偏移地址:0x0C 复位值:0x0000 0000

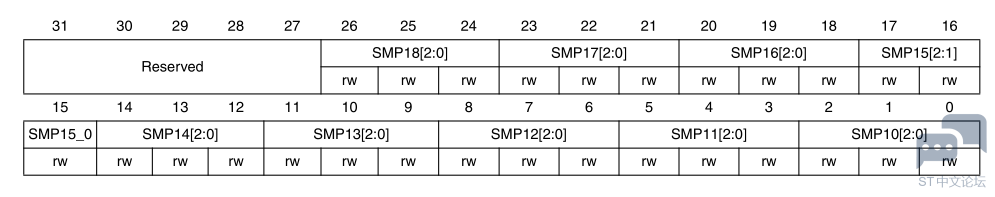

11.5 ADC 采样时间寄存器 2 (ADC_SMPR2) ADC sample time register 2 偏移地址:0x10 复位值:0x0000 0000 ![SKV`G_[PR4$$]794GP[X.png SKV`G_[PR4$$]794GP[X.png](data/attachment/forum/202206/14/145343v5w0f1w60636p1ry.png)

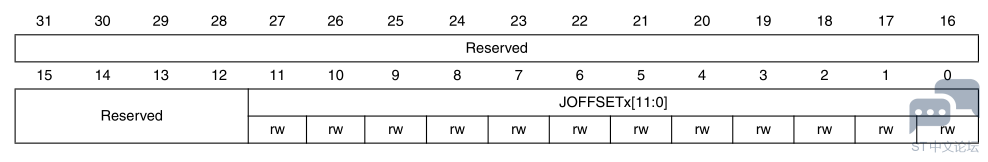

11.6 ADC 注入通道数据偏移寄存器 X (ADC_JOFRx)(x=1…4) ADC injected channel data offset register x 偏移地址:0x14-0x20 复位值:0x0000 0000

11.7 ADC 看门狗高阈值寄存器 (ADC_HTR) ADC watchdog higher threshold register 偏移地址:0x24 复位值:0x0000 0FFF

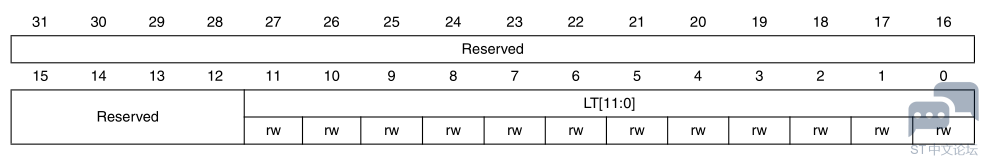

11.8 ADC 看门狗低阈值寄存器 (ADC_LTR) ADC watchdog lower threshold register 偏移地址:0x28 复位值:0x0000 0000

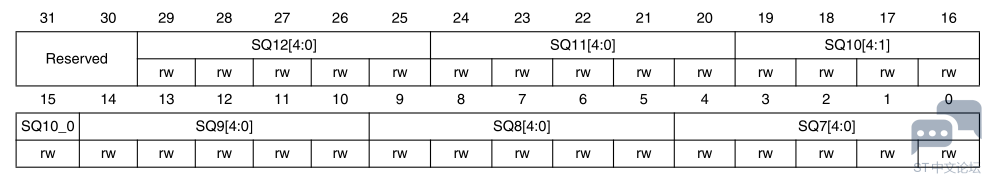

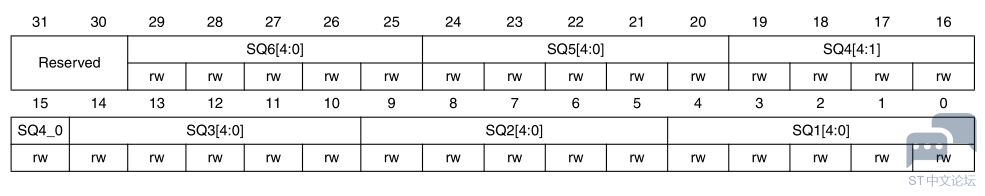

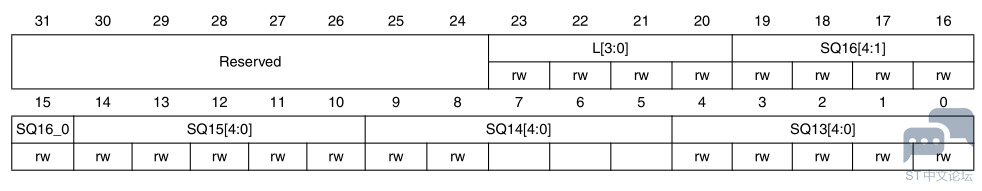

11.9 ADC 规则序列寄存器 1 (ADC_SQR1) ADC regular sequence register 1 偏移地址:0x2C 复位值:0x0000 0000 11.10 ADC 规则序列寄存器 2 (ADC_SQR2) ADC regular sequence register 2 偏移地址:0x30 复位值:0x0000 0000

11.11 ADC 规则序列寄存器 3 (ADC_SQR3) ADC regular sequence register 3 偏移地址:0x34 复位值:0x0000 0000

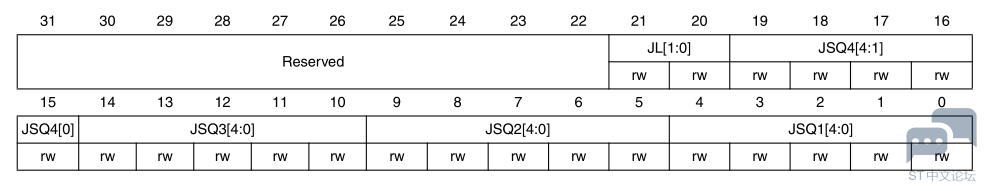

11.12 ADC 注入序列寄存器 (ADC_JSQR) ADC injected sequence register 偏移地址:0x38 复位值:0x0000 0000

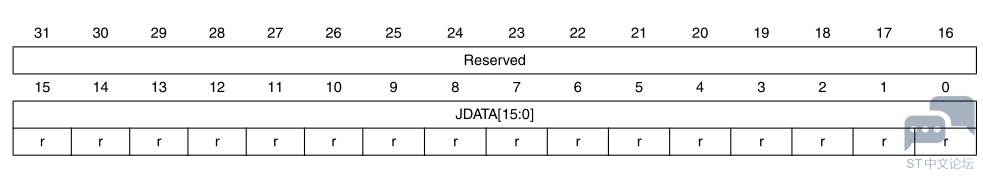

11.13 ADC 注入数据寄存器 x (ADC_JDRx) (x= 1…4) ADC injected data register x 偏移地址:0x3C - 0x48 复位值:0x0000 0000

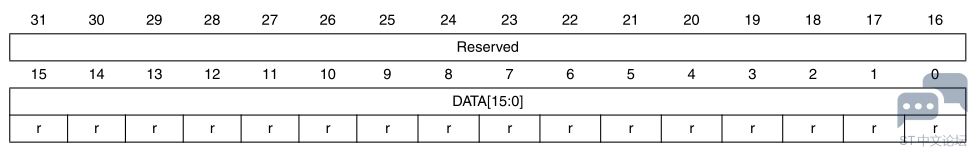

11.14 ADC 规则数据寄存器 (ADC_DR) ADC regular data register 偏移地址:0x4C 复位值:0x0000 0000

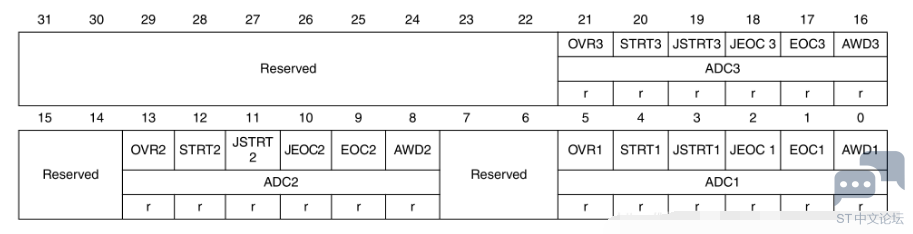

11.15 ADC 通用状态寄存器 (ADC_CSR) ADC Common status register 偏移地址:0x00(该偏移地址与 ADC1 基地址 + 0x300 相关) 复位值:0x0000 0000 该寄存器可提供不同 ADC 的状态位图像。但是,它为只读形式且不允许将不同的状态位清零。必须在对应的 ADC_SR 寄存器中将其写为 0,才能将各个状态位清零。

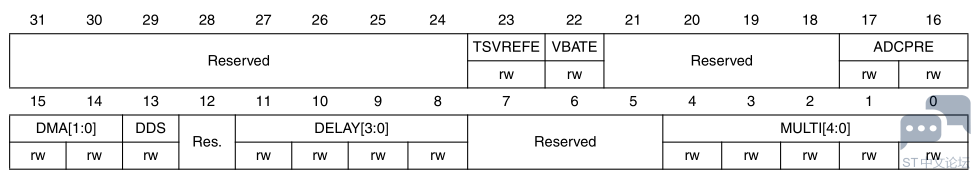

11.16 ADC 通用控制寄存器 (ADC_CCR) ADC common control register 偏移地址:0x04(该偏移地址与 ADC1 基地址 + 0x300 相关) 复位值:0x0000 0000

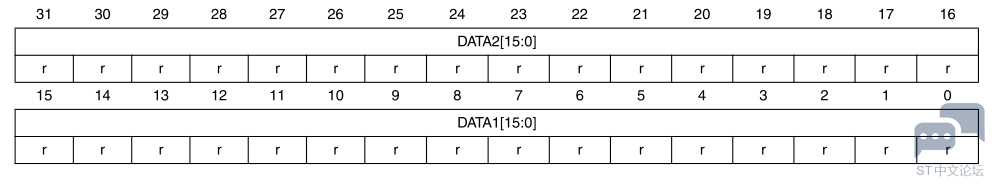

11.17 适用于双重和三重模式的 ADC 通用规则数据寄存器(ADC_CDR) ADC common regular data register for dual and triple modes 偏移地址:0x08(该偏移地址与 ADC1 基地址 + 0x300 相关) 复位值:0x0000 0000

|

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

2024意法半导体工业峰会:赋能智能电源和智能工业,构筑可持续未来

ST推出灵活、面向未来的智能电表通信解决方案,助力能源转型

意法半导体 x Qu-Bit Electronix:推动新一轮的数字声音合成革命

微信公众号

微信公众号

手机版

手机版