.png) STMCU小助手

发布时间:2022-6-26 11:46

STMCU小助手

发布时间:2022-6-26 11:46

|

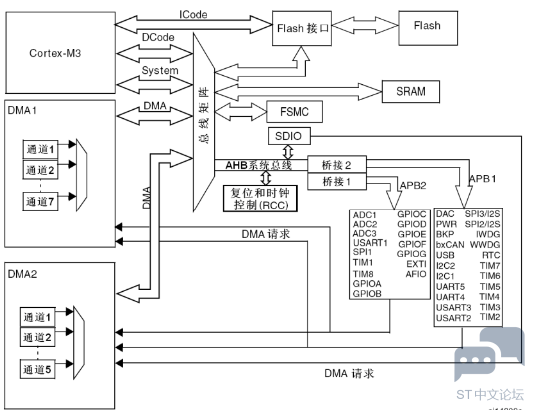

在小容量、中容量和 大容量产品中,主系统由以下部分构成: ● 四个驱动单元: ─ Cortex™-M3内核DCode总线(D-bus),和系统总线(S-bus) ─ 通用DMA1和通用DMA2 ● 四个被动单元 ─ 内部SRAM ─ 内部闪存存储器 ─ FSMC ─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备 这些都是通过一个多级的AHB总线构架相互连接的,如下图所示:

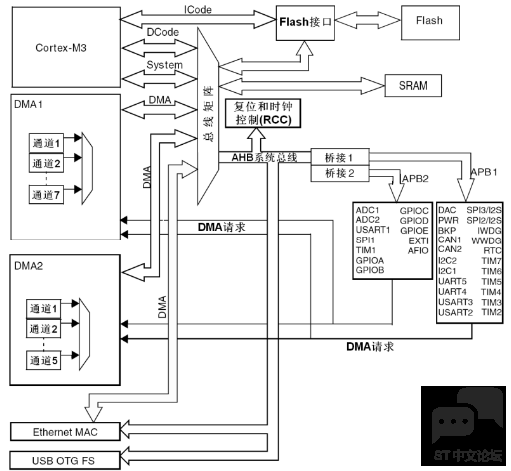

在互联型产品中,主系统由以下部分构成: ● 五个驱动单元: ─ Cortex™-M3内核DCode总线(D-bus),和系统总线(S-bus) ─ 通用DMA1和通用DMA2 ─ 以太网DMA ● 三个被动单元 ─ 内部SRAM ─ 内部闪存存储器 ─ AHB到APB的桥(AHB2APBx),它连接所有的APB设备 这些都是通过一个多级的AHB总线构架相互连接的,如下图所示:

ICode总线 该总线将Cortex™-M3内核的指令总线与闪存指令接口相连接。指令预取在此总线上完成。 DCode总线 该总线将Cortex™-M3内核的DCode总线与闪存存储器的数据接口相连接,常量加载和调试访问。 系统总线 此总线连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。 DMA总线 此总线将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到SRAM、闪存和外设的访问。 总线矩阵 总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。在互联型产品中,总线矩阵包含5个驱动部件(CPU的DCode、系统总线、以太网DMA、 DMA1总线和DMA2总线)和3个从部件(闪存存储器接口(FLITF)、 SRAM和AHB2APB桥)。 在其它产品中总线矩阵包含4个驱动部件(CPU的DCode、系统总线、 DMA1总线和DMA2总线)和4个被动部件(闪存存储器接口FLITF、 SRAM、 FSMC和AHB2APB桥)。 AHB外设通过总线矩阵与系统总线相连,允许DMA访问。 AHB/APB桥(APB) 两个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz, APB2操作于全速,最高72MHz。在每一次复位以后,所有除SRAM和FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外设的时钟。当对APB寄存器进行8位或者16位访问时,该访问会被自动转换成32位的访问:桥会自动将8位或者32位的数据扩展以配合32位的向量。 |

STM32 GUI LTDC 最大像素时钟评估方法

【2025·STM32峰会】GUI解决方案实训分享1-对LVGL咖啡机例程的牛刀小试以及问题排查

OpenBLT移植到STM32F405开发板

为什么要先开启STM32外设时钟?

【STM32MP157】从ST官方例程中分析RPMsg-TTY/SDB核间通信的使用方法

【经验分享】STM32实例-RTC实时时钟实验④-获取RTC时间函数与中断服务函数

STM32 以太网 MAC Loopback 的实现

STM32功能安全设计包,助力产品功能安全认证

基于STM32启动过程startup_xxxx.s文件经验分享

HRTIM 指南

微信公众号

微信公众号

手机版

手机版