.png) STMCU小助手

发布时间:2022-7-17 22:19

STMCU小助手

发布时间:2022-7-17 22:19

|

前言 本应用笔记为系统设计人员提供了 STM32F3xx 硬件特性概述,例如供电、时钟管理、复位控制、自举模式设置和调试管理等。它显示了如何使用 STM32F3xx 产品系列,说明了开发STM32F3xx 应用所需的最低硬件资源。 禁用嵌入式调压器的STM32F3xx器件与启用嵌入式调压器的STM32F3xx器件共享相同的特性 / 外设,仅有部分不同。 在第 6 章节中对差别进行了汇总。 本文还包含了详细的参考设计原理图,说明了主要元件、接口和模式。 在本文其余部分 (除非特别说明), STM32F3xx 一词指下面表 1 中的部件编号。 ![(I5C`K1`P[)16R}N{TR]NJ2.png (I5C`K1`P[)16R}N{TR]NJ2.png](data/attachment/forum/202207/17/221316ocoxcoi5nhl5k2jx.png)

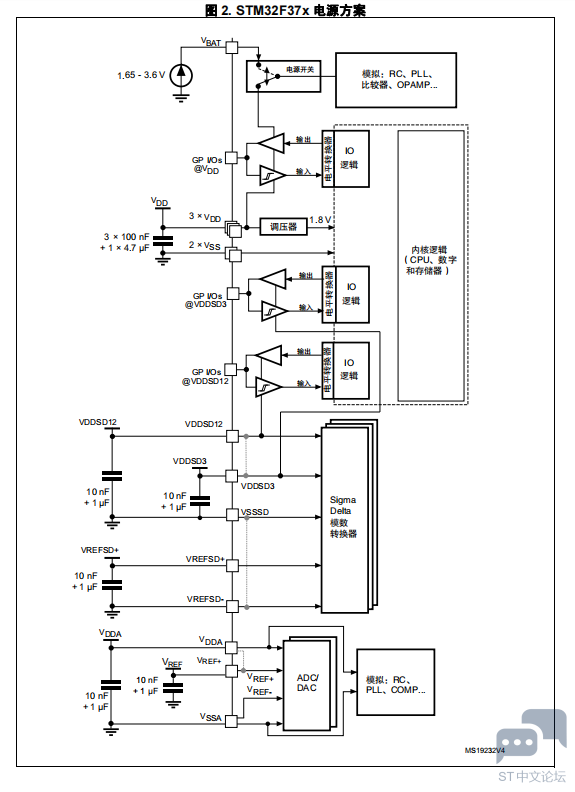

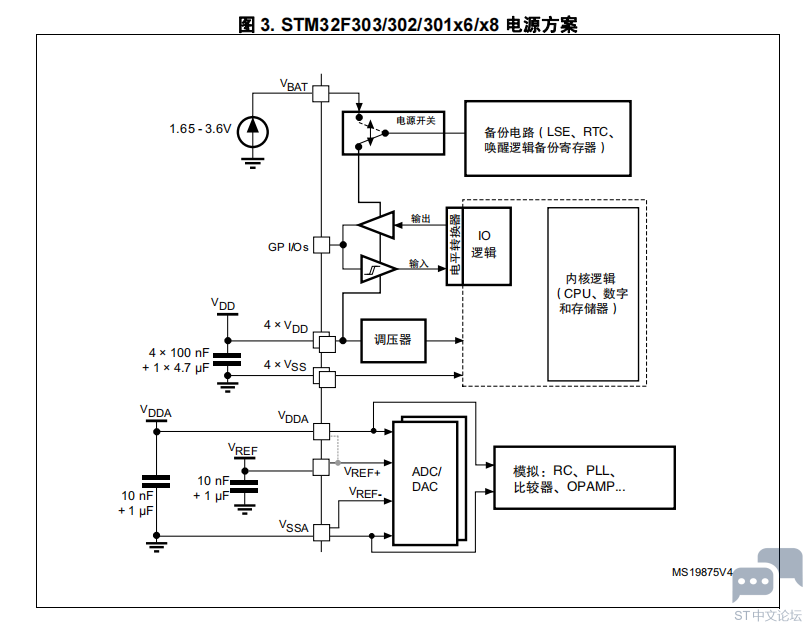

1电源 1.1电源方案 有多种供电方案: •VDD = 2.0 V 到 3.6 V:I/O 和内部调压器的外部电源。 通过 VDD 引脚从外部提供。 •VDDA = 2.0 到 3.6 V:ADC/DAC、比较器、复位块、 RC、 PLL 的外部模拟供电 (在STM32F30x 中,当使用 OPAMP 和 DAC 时,施加于 VDDA 的最低电压为 2.4 V。在STM32F37x 中,当使用 ADC 和 DAC 时,施加于 VDDA 的最低电压为 2.4 V)。 VDDA 电平必须一直大于等于 VDD 电平,且必须首先提供。 •VBAT = 1.65 V 到 3.6 V:当 VDD 不存在时,作为 RTC、 32 kHz 外部时钟振荡器和备份寄存器的电源 (通过电源开关供电)。 •VDDSD12= 2.2 到 3.6 V:SDADC1/2、PB2、PB10、PE7 至 PE15 I/O 引脚的外部供电(I/O引脚接地内部连接于 VSS)。 VDDSD12 必须一直小于等于 VDDA。若 VDDSD12 未使用,则必须连接到 VDDA。 •VDDSD3= 2.2 到 3.6 V:SDADC3、PB14 至 PB15、PD8 至 PD15 I/O 引脚的外部供电(I/O引脚接地内部连接于 VSS)。 VDDSD3 必须一直小于等于 VDDA。若 VDDSD3 未使用,则必须连接到 VDDA。 注 : VDDSD12 和 VDDSD3 仅在 STM32F37x 上可用。 ![]W5{PPM4__UE31E}6HF{3L6.png ]W5{PPM4__UE31E}6HF{3L6.png](data/attachment/forum/202207/17/221406o9igegelzwed2vh0.png)

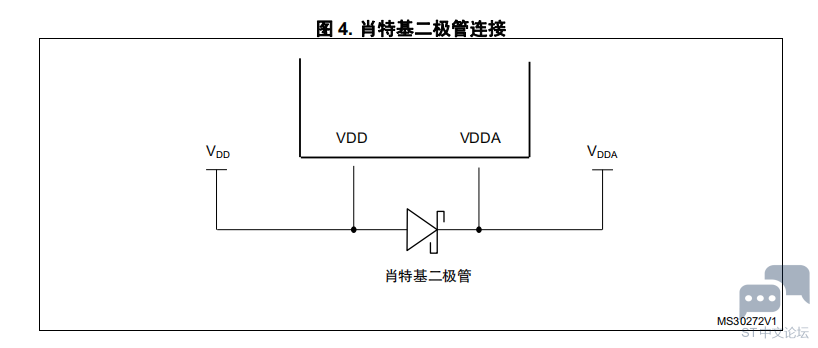

1.1.1独立模拟电源 为了提高转换精度、扩展供电的灵活性,模拟域配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。 •ADC 和 DAC 电源电压从单独的 VDDA 引脚输入。 •VSSA 引脚提供了独立的电源接地连接。 VDDA 供电可大于等于 VDD。这使得 VDD 在保持为低的同时仍可为模拟块提供全部性能。 当使用单供电时, VDDA 可外部连接至 VDD,为得到无噪声的 VDDA,需通过外部滤波电路。 当 VDDA 不等于 VDD 时, VDDA 必须一直大于等于 VDD。在开机 / 关机期间,为在 VDDA 和VDD 之间保持安全的电位差,可在 VDD 和 VDDA 之间使用外部肖特基二极管。请参考数据手册以得到最大允许的电位差。

1.1.2 Sigma Delta 供电电压 (仅适用于 F37x) 为提高 Sigma delta ADC (SDADC)外设的性能,设备有两个独立的电源,用以对 SDADC外设供电。两个供电引脚有公共的接地引脚 (VDDSD12、 VDDSD3、 VSSSD)。 这些电源也定义了数字 GPIO 引脚上的电平,它们对于给定的 SDADC 外设共享 SDADC 模拟输入。请参考设备数据手册,以了解哪些 GPIO 由 VDDSD12 供电,哪些由 VDDSD3 供电。 Sigma delta 供电必须一直小于等于模拟供电:VDDSDx < VDDA,但它们可小于或大于 VDD。 若应用中不使用 SDADC,则 VDDSDx 必须外部连接至 VDD。 VSSSD 必须一直连接至 VSS。 关于 VDDSD12 和 VDDSD3,还有一些限制条件与用于 SDADC 的参考电压有关: •若 VREFSD+ 引脚被选为 SDADC 的外部参考电压: –若 SDADC1 或 SDADC2 在 PWR 控制器中启用 (ENSD1、 ENSD2 比特),则:VDDSD12 > VREFSD+, VDDSD3 > VREFSD+ –若 SDADC1 和 SDADC2 在 PWR 控制器中禁用,则:VDDSD3 > VVREFSD+ •若 VDDSDx 供电被选为 SDADC 的参考电压: –若 SDADC1 或 SDADC2 在 PWR 控制器中启用 (ENSD1、 ENSD2 比特),则: VDDSD12 = VDDSD3 •若 SDADC1 和 SDADC2 在 PWR 控制器中禁用, SDADC3 启用 (ENSD1、 ENSD2、ENSD3 比特),则:VDDSD12 <= VDDSD3。 1.1.3 电池备份 要在 VDD 关闭后保留备份寄存器的内容,可以将 VBAT 引脚连接到通过电池或其它电源供电的可选备用电压。 VBAT 引脚还为 RTC 单元供电,因此即使当主数字供电 (VDD)关闭时 RTC 也能工作。 VBAT 电源的开关由复位模块中内置的掉电复位 (PDR)电路进行控制。 若应用中没有使用外部电池,则强烈建议将 VBAT 外部连至 VDD。 1.1.4 调压器 此调压器在复位后始终处于使能状态。 根据应用模式的不同,可采用三种不同的模式工作: •运行模式:调压器为 1.8 V 域 (内核、存储器和数字外设)提供全功率。 •停止模式:调压器为 1.8 V 域提供低功率,保留寄存器和内部 SRAM 中的内容。 •待机模式:调压器关。除待机电路和备份域外,寄存器和 SRAM 的内容都将丢失。这包括下列特性,可通过对单个控制位编程对其选择: –独立的看门狗 (IWDG):IWDG 通过写入其密钥寄存器或使用硬件选项来启动。而且一旦启动便无法停止,除非复位。 –实时时钟 (RTC):通过备份域控制寄存器 (RCC_BDCR) 中的 RTCEN 位进行配置。 –内部 RC 振荡器 (LSI):通过控制 / 状态寄存器 (RCC_CSR) 中的 LSION 位进行配置。 –外部 32.768 kHz 振荡器 (LSE):通过备份域控制寄存器 (RCC_BDCR) 中的LSEON 位进行配置。 1.2复位和供电监控器 1.2.1复位 共有三种类型的复位,分别为系统复位、电源复位和备份域复位。 系统复位 除了时钟控制寄存器 CSR 中的复位标志和备份域中的寄存器外,系统复位会将其它全部寄存器都复位为复位值。只要发生以下事件之一,就会产生系统复位: 1. NRST 引脚低电平 (外部复位)。 2. 系统窗口看门狗事件 (WWDG 复位)。 3. 独立看门狗事件 (IWDG 复位)。 4. 软件复位 (SW 复位)。 5. 低功耗管理复位。 6. 选项字节加载复位。 7.电源复位 可通过查看控制状态寄存器 (RCC_CSR)中的复位标志确定复位源。 RESET 复位入口向量在存储器映射中固定在地址 0x0000_0004。 芯片内部的复位信号会向 NRST 引脚上输出一个低电平脉冲。脉冲发生器可确保每个内部复位源的复位脉冲都至少持续 20 µs。对于外部复位,在 NRST 引脚处于低电平时产生复位脉冲。 ![~N@TSIAVB{$WK25]C4L2$)C.png ~N@TSIAVB{$WK25]C4L2$)C.png](data/attachment/forum/202207/17/221817gbqy4p1l45l1keey.png)

电源复位 只要发生以下事件之一,就会产生电源复位: 1.开机 / 关机复位 (POR/PDR 复位) 2. 在退出待机模式时 备份域复位 备份域具有两个特定的复位,这两个复位仅作用于备份域本身。只要发生以下事件之一,就会产生备份域复位: 1.软件复位通过设置备份域控制寄存器 (RCC_BDCR)中的 BDRST 位触发。 2. 在电源 VDD 和 VBAT 都已掉电后,其中任何一个又再上电。 完整版请查看:附件 |

DM00070391_ZHV3.pdf

下载704.57 KB, 下载次数: 5

微信公众号

微信公众号

手机版

手机版