|

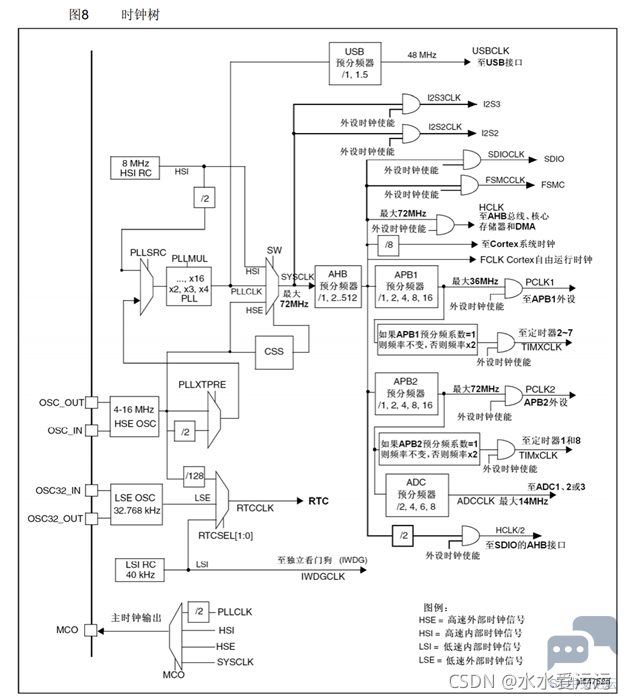

一、STM32F103时钟树 首先先放一张STM32参考手册中的一张时钟树,对照着来讲,如图所示:

首先对图里出现的几个名词做个介绍:

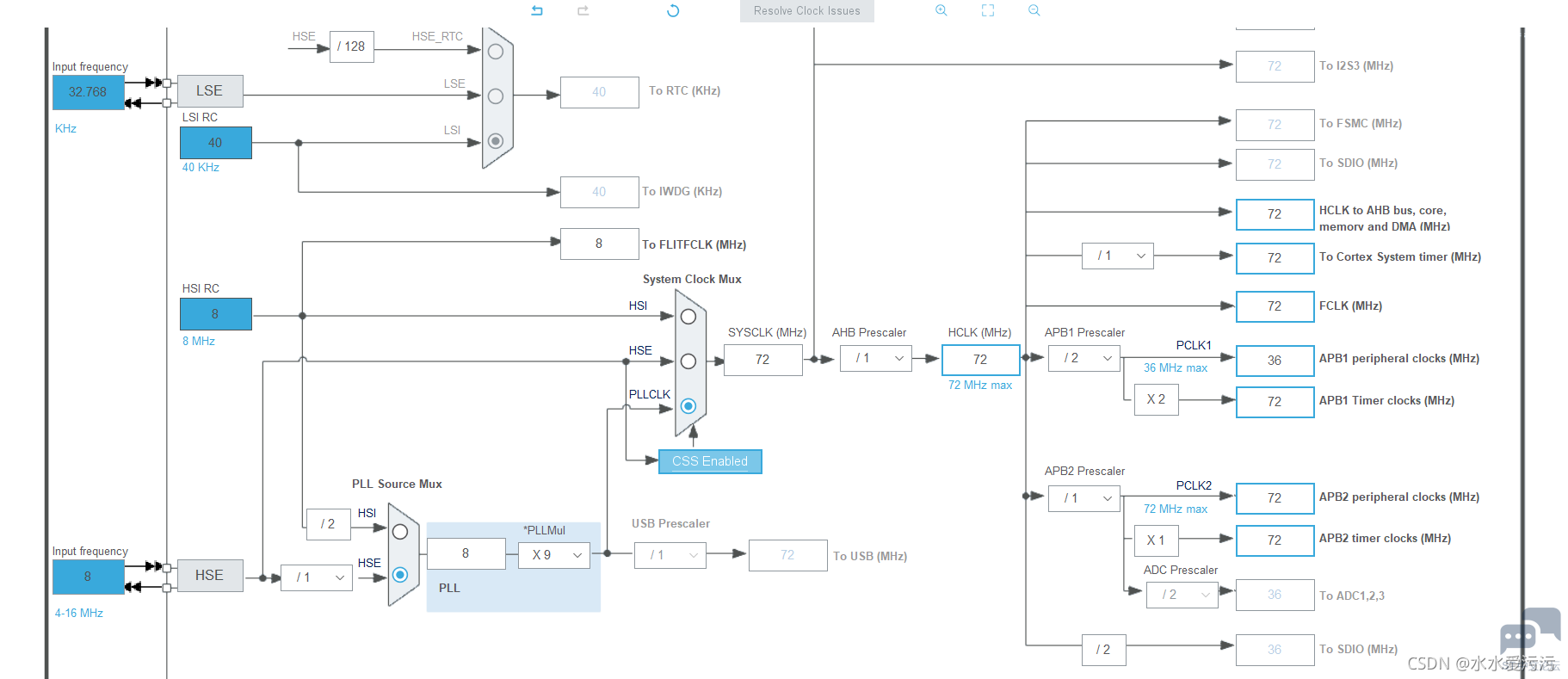

为了更加清晰直观,再放上一张STM32CUBEMX里配置时钟系统的图:

首先先明确一点我们的STM32有HSE、HSI、LSE、LSI、PLL五个时钟源,接下来会对这五个时钟源进行介绍。 1.1 HSE、HSI、PLL、SYSCLK 我们想要配置的时钟是SYSCLK即系统时钟,我们一般说的STM32F103时钟72M就是指这个SYSCLK系统时钟,从图里可以看到,配置系统时钟的时钟来源主要有三个:

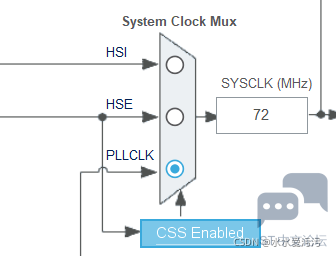

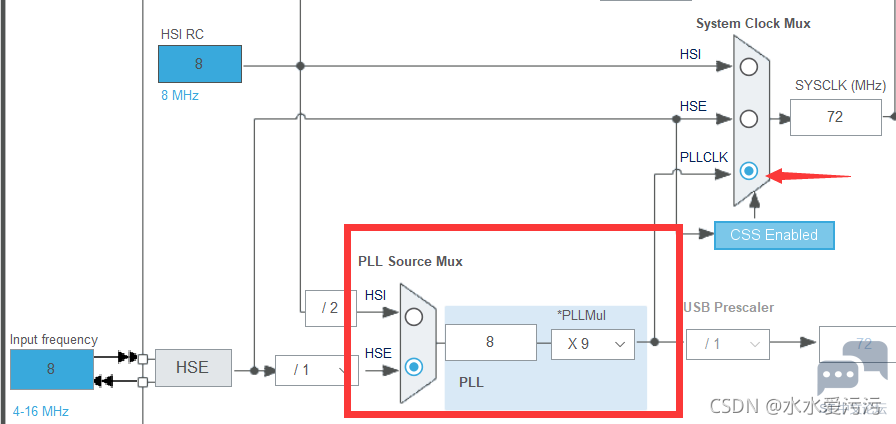

分别是HSI、HSE、PLLCLK,我们配置系统时钟的来源可以是外部高速时钟、内部高速时钟和锁相环PLL出来的时钟信号,我们都知道在MCU没有超过最高时钟频率运行之前,时钟频率越高,系统运行更加稳定,故我们配置时钟时一般都是希望配置的时钟频率接近上限。 在STM32F103芯片里HSI给定了是内部8M的高速时钟,HSE可以是从4~16M之间自己选择焊接任意频率的晶振,而PLL锁相环是可以将时钟频率倍频提高可以实现稳定且高频的时钟信号。我们先来看一下PLL锁相环的时钟线:

PLL锁相环的输入可以是经过二分频的HSI也就是4M的内部时钟提供的信号,还有外部高速时钟HSE可以不分频或者二分频的信号,一般来说我们都会采用外部的时钟信号更加的稳定和准确,这里我们单片机外部焊接的是8M的晶振故我们选择PLL输入来源是HSE,在PLL内是经过*PLLMul(*9)来实现达到72M的频率,最后输出给到SYSCLK。 1.2 LSE、LSI、RTC 讲到这里HSE、HSI、PLL、SYSCLK相信大家都有了认识,接下来还有两个LSI和LSE有什么作用呢,我们看到STM32参考手册里有这样一段话:

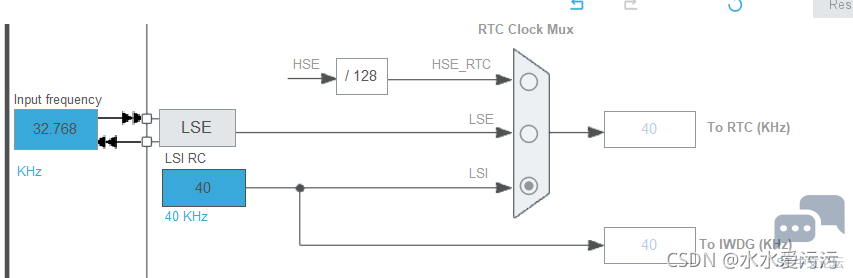

我们的芯片内部低速时钟LSI是40khz的,用来驱动看门狗或者是RTC时钟的,外部的低速时钟是32.768khz可以用来驱动RTC,很遗憾我没有做过关于RTC的实验,故对实时时钟的解释不是很充分,没有特殊要求一般不会去用到,如图所示:

1.3 重要提示 上面介绍了五个时钟源,我们在不使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗,比如说我只用了一个HSE和PLL来配置SYSCLK,那么其他的时钟源可以不需要开启,以此降低功耗。 1.4 HCLK、PCLK1、PCLK2 配置完SYSCLK算是完成了时钟配置的一半,我们接着看时钟图后面,如图所示:

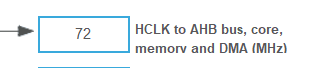

SYSCLK系统时钟出来后可以看到会经过一个AHB预分频器,将分频后的信号给至HCLK高速外设时钟,STM32规定最大的时钟信号是72MHz,和我们配置的SYSCLK一致,一般都是将SYSCLK配置为最高的HCLK时钟频率之后预分频器分频系数给1,将SYSCLK和HCLK时钟信号频率配置最高,以此达到系统高稳定性高性能状态,HCLK出来的时钟信号会给至AHB总线、核心存储器、DMA:

STM32还设置了两条外设时钟线,一条是PCLK1低速时钟,另一条是PCLK2高速时钟,PCLK1经过AHB1预分频器分频最高可达36M,PCLK2经过AHB2预分频器分频最高可达72M,如图所示:

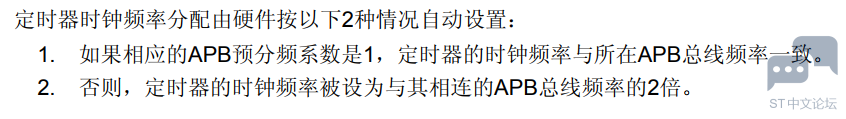

在外设中存在着比较特殊的比如定时器,如上图所示,在APB1/2分频完成后有对搭载的定时器TIMER进行了分频那么怎么确定应该是多少呢,可以在STM32参考手册中找到这样一段:

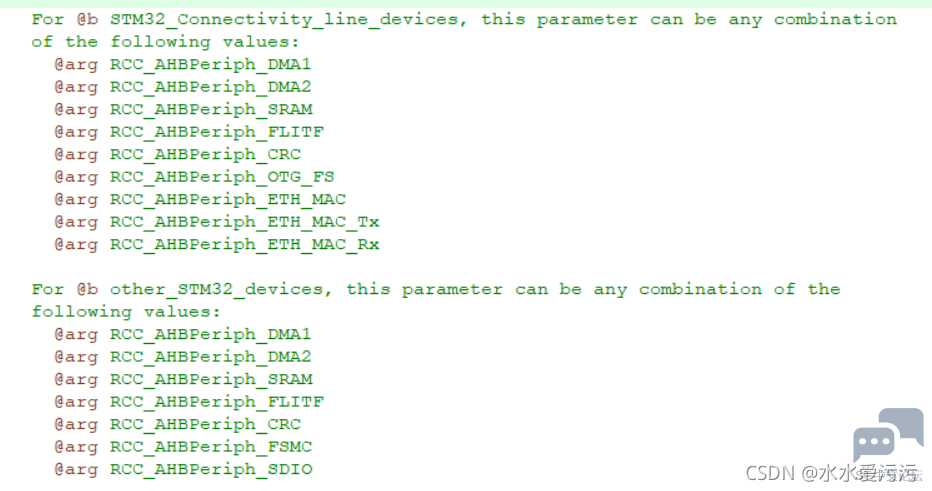

为什么需要这么多外设的时钟呢,我们都知道在操作STM32外设之前都需要打开对应的外设时钟,比如我要操作GPIOA01输出高电平,我需要先打开GPIOA的外设时钟,才能对引脚进行操作,如下图所示是STM32F103各个外设时钟搭载的外设: AHB搭载了DMA1/2、SRAM、核心存储器等都在HCLK提供的时钟频率下运行,比如想要用DMA1就需要通过打开AHB下的DMA1时钟,时钟频率就是HCLK,才能使用DMA1。

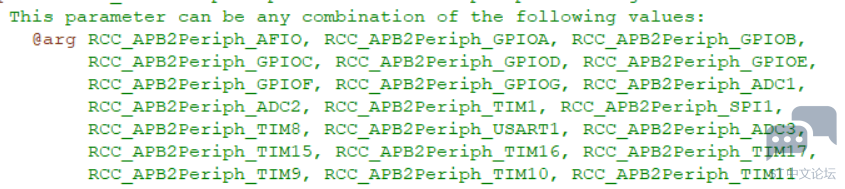

APB2搭载了例如GPIOA~G、ADC等

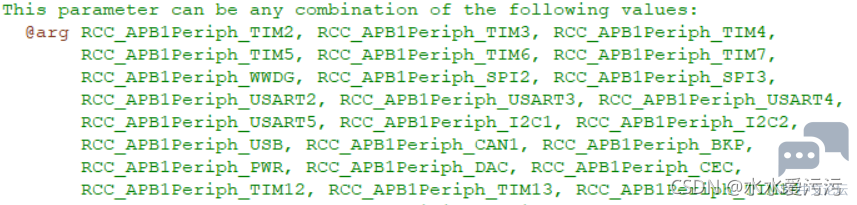

APB1搭载了通用定时器、USART、CAN等外设

1.5 时钟树小结 一条较为完整的时钟配置路线大致为:HSE–PLL–SYSCLK–AHB–HCLK–AHB1–PCLK1(/–AHB2–PCLK2),综上就是STM32配置时钟树的大部分内容,相信大家对时钟树的理解进一步加深,接下来我们讲怎么在标准库中配置我们的时钟系统。 二、程序配置(以之前新建的工程为例) 第一步打开我们的工程文件定位到startup文件夹,双击打开我们的启动文件,如图所示:

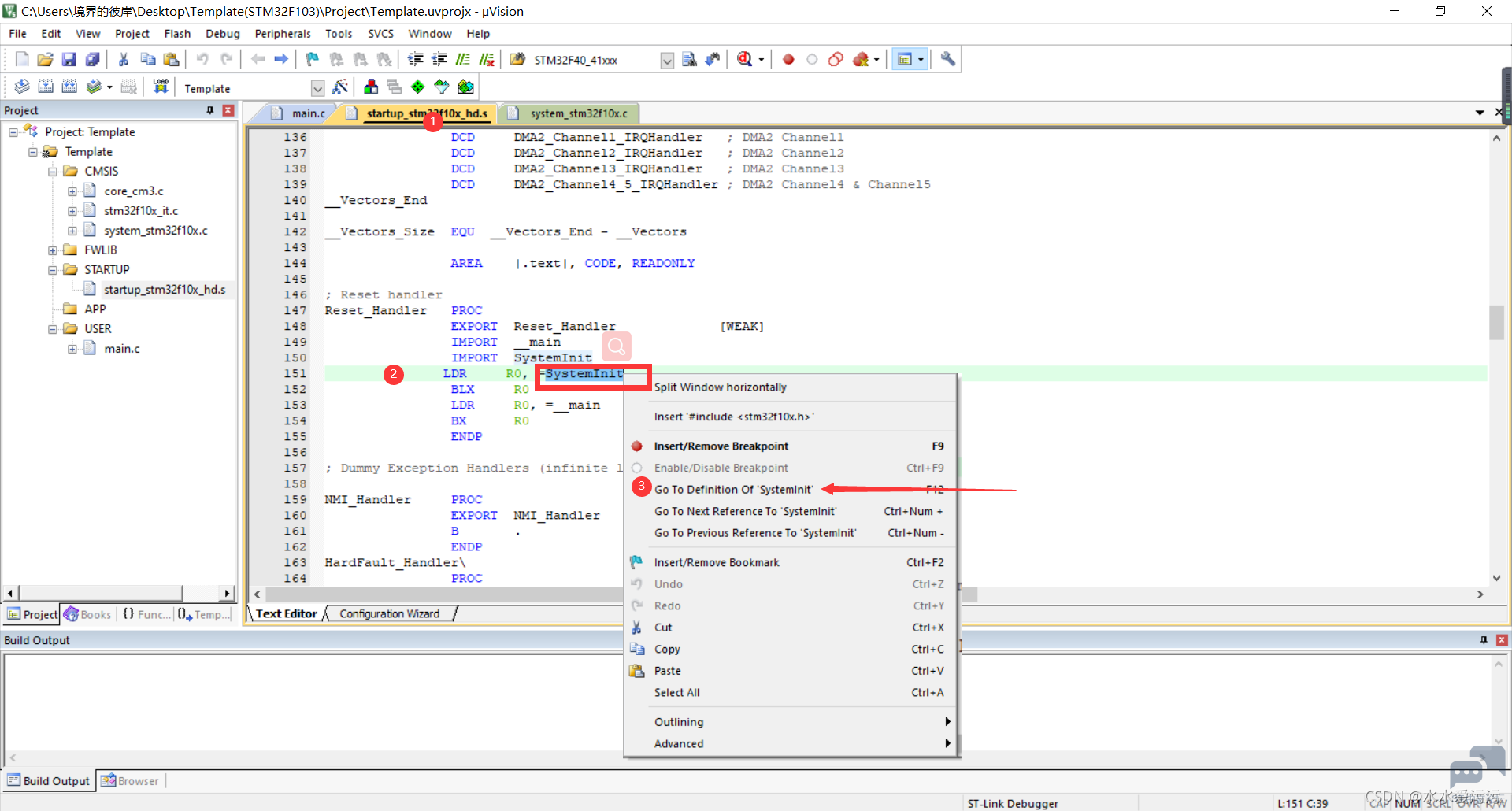

第二步我们知道STM32程序都是在启动文件里开始执行的,所以我们下拉代码找到程序运行的入口SystemInit,选中SystemInit鼠标右键单击Go To Definition…或者选中后按下快捷键F12进行跳转,如图所示:

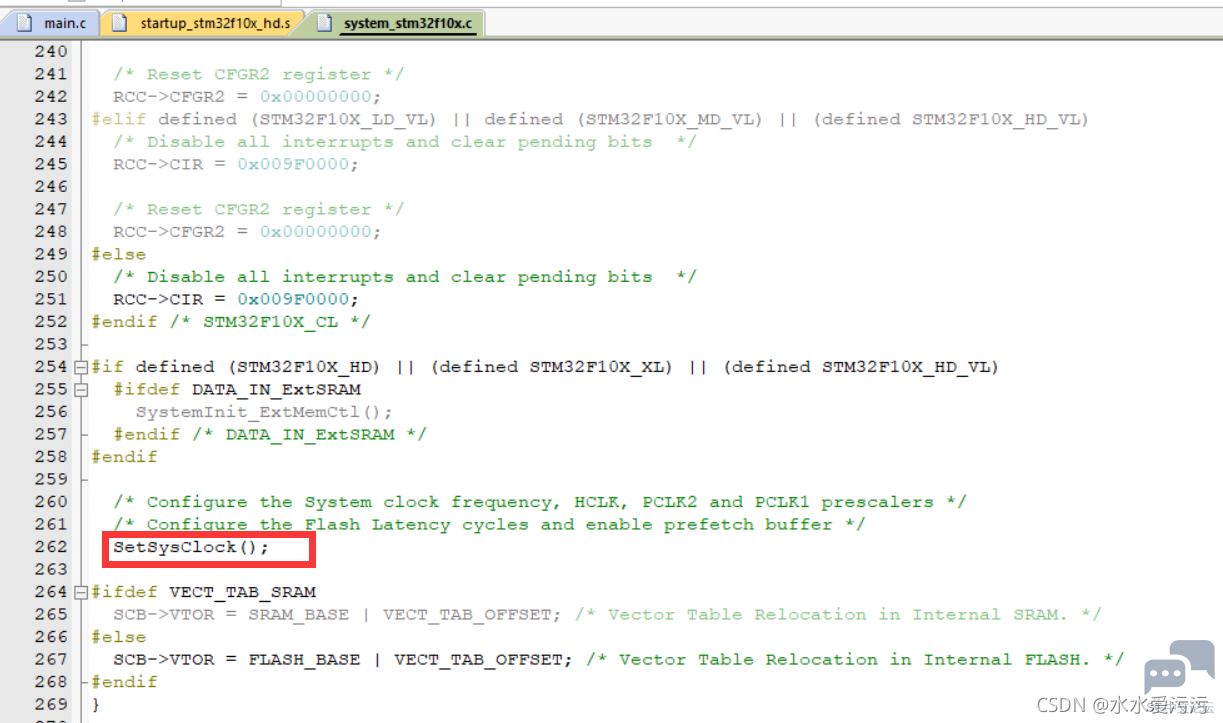

第三步 SystemInit函数刚开始是初始化了很多与时钟相关的寄存器,将RCC时钟配置重置为默认的重置状态,往下看会找到一个SetSysClock()的函数,再次跳转,找到函数主体:

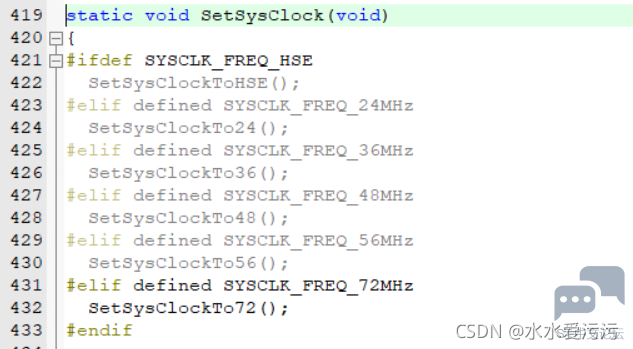

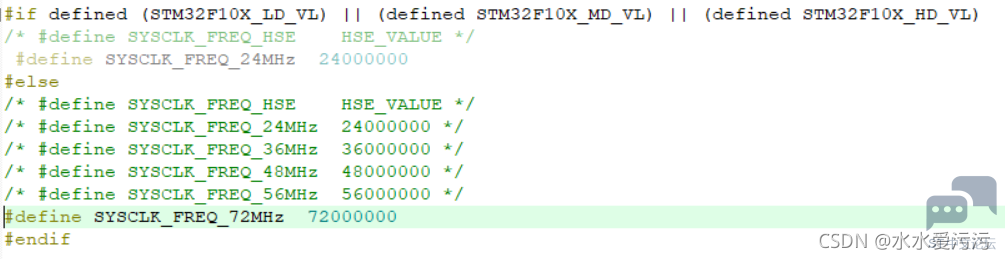

第四步跳转后可以看到这里通过判断标识符的方式将会执行SetSysClockTo72()函数,我们设置了72M的系统时钟,可以点击宏定义标识符查看,根据需要可以选择不同的时钟频率,如下两图:

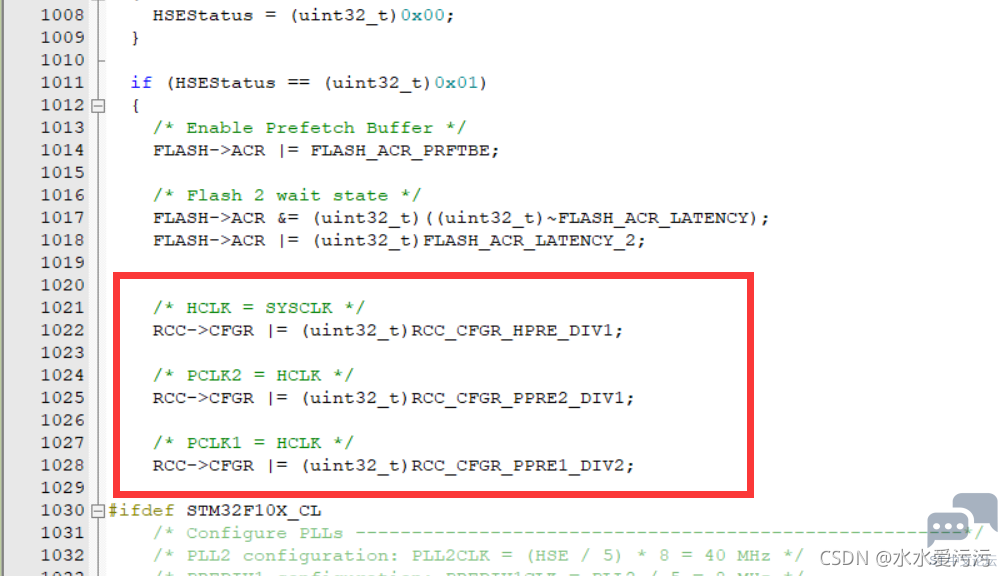

第五步再次点击跳转SetSysClockTo72()函数,可以看到,我们进入了真正的配置系统时钟的地方,该函数起到设置“系统时钟频率”为72MHz,并配置“HCLK”、“PCLK2”和PCLK1预分压器的作用。整个系统时钟配置的过程是先启动外部晶振等待稳定然后设置好AHB,APB1,APB2,PLL相关的系数再启动PLL维持稳定后完成时钟配置,可以通过官方提供的注释看到,比较关键的一段如图:

可以看到,HCLK配置为分频系数为1和SYSCLK频率相等,PCLK2分频系数也是1和HCLK频率相等,PCLK1分频系数为2是HCLK频率的二分频,但是注释却打了相等可能是注释打错了。

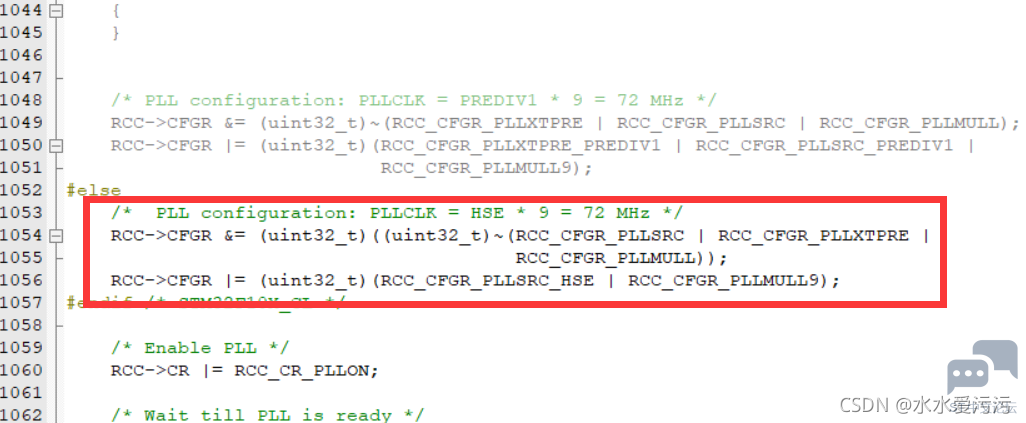

这里是PLL锁相环的配置,需要留意的是RCC_CFGR_PLLMULL9这个参数,最后HSE出来的信号会乘上9提供给我们的SYSCLK信号。 第六步到这里为止所有的分频系数参数都设置完毕,最后要等待PLL提供稳定的时钟信号,整个系统完成时钟配置,如图所示:

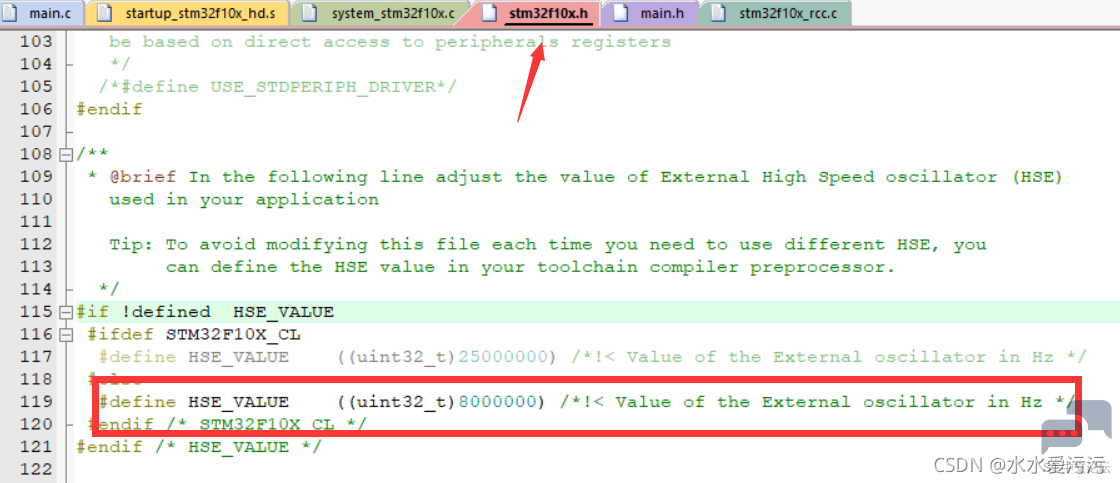

注:那我们通过程序查询比如HCLK的时钟,程序怎么知道HSE是多少呢,我们可以看到在stm32f10x.h里有一个HSE_VALUE的参数,这个参数定义的是我们使用的外部晶振的频率,这是8M,如图所示:

三、小结 这一讲我们认识并强化了对系统时钟的概念和理解,对程序的配置上有了进一步的认识,大家可以在自己研读一下设置时钟的程序,这里程序讲的比较省略了关注点在时钟配置上了,下一讲会教大家如何运用keil5的DEBUG功能查询我们设置好的时钟频率究竟对不对。 ———————————————— 版权声明:水水爱污污 |

OpenBLT移植到STM32F103战舰开发板上适用于所有STM32F103系列的Bootloader

TFT LCD 与 FSMC 的硬件连接大容量 STM32F10xxx FSMC 接口

经验分享 | 利用TIMER定时和捕获功能实现编解码演示

单片机:初学者该了解的STM32F103基础知识

STM32 LSE 不起振排查指南:五大核心原因与快速解决方案

我心中的ST中文论坛

经验分享 | 利用STM32 TIMER实现同频跟随输出示例

2025软件工具兔哥知道

STM32之继电器模块

STM32固件库分享,超全系列整理

微信公众号

微信公众号

手机版

手机版