.png) STMCU小助手

发布时间:2023-2-10 17:13

STMCU小助手

发布时间:2023-2-10 17:13

|

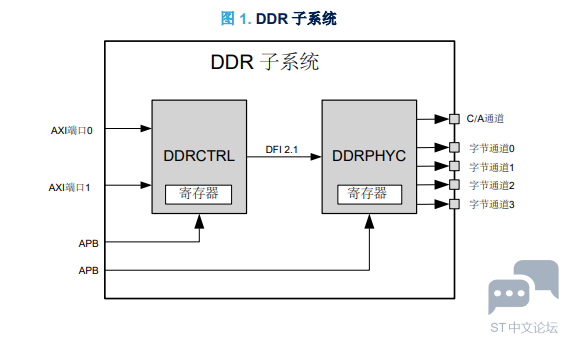

前言本文档描述在 STM32MP1 系列 MPU 上配置 DDR 子系统(DDRSS)所需的流程和步骤。# a, r: q' `2 g$ h* I" v8 V 通过设定 DDR 控制器(DDRCTRL)、PHY 接口(DDRPHYC)和 SDRAM 模式寄存器的多个参数和设置完成 DDRSS 配置。根据 DDR 类型、DDR 大小、DRAM 拓扑、运行时间频率和 SDRAM 器件数据手册参数确定这些参数。所有这些参数必须在初始化序列期间设定。: h! y$ w7 O* z6 O2 u' t STM32CubeMX DDR 测试套件使用直观的面板和菜单隐藏了与确定正确参数和初始化启动相关的复杂性(请参考[6])。为了快速设置要运行的 DDRSS,用户只需提供很少几个输入即可完成配置。可以使用一些高级用户模式和特殊功能(当它们对于应用而言十分重要时)。% l5 N. k' H% P% i 在系统启动阶段,为了优化时序裕量,支持多种 PHY 调谐。可以使用 STM32CubeMX 启动这些调谐。PHY 调谐结果可以保存并在后续冷复位时恢复。1 W9 ?- r; m' b# H9 Y 在启动阶段,用户可以运行大量测试套件。这些测试可以使用 STM32CubeMX 启动,并用于确认 DDR 配置的稳健性。( ]. j5 C+ Y1 c4 ^2 \ . l, O+ n ?$ {! v 1 概述 本文档适用于 STM32MP1 系列基于 Arm®的 MPU。8 s0 S# U* W1 O! O( B8 z 提示 Arm 是 Arm Limited(或其子公司)在美国和/或其他地区的注册商标。 + ~0 d! B$ l; w4 Q! u 2 DDR 子系统初始化和配置 DDR 子系统包括 DDRCTRL 和 DDRPHYC(参见下图)。( Q0 J, L* b5 ?. S; I. N DDRCTRL 支持在正常操作期间通过命令和刷新调度进行 DDR 命令调度。8 g* R% T2 j; n6 ^: I1 x1 V5 L DDRPHYC 是一种 DDR PHY 接口,具有连接 DDRCTL 的 DFI 接口[7]和字节通道架构,适合连接频率不超过 533MHz 的 DDR3/3L 和 LPDDR2/3。" V/ m* [1 p7 |& M DDRPHYC 完全支持具有多个 PHY 调谐选项(内置)的 DDR 初始化。DDRPYC 包含 BIST 引擎,用于支持软件驱动的调谐。

2.1 DDRSS 和 SDRAM 初始化% q( W, O9 n3 c8 h 器件根据 SDRAM 启动序列对电源、时钟和复位进行内部排序。 图 2 所示的 PHY 初始化序列由 DDRPHYC 物理实用模块(PUB)控制。这一基于 PUB 的初始化序列在DDRPHYC 从复位状态释放后启动,并根据 DDRPHYC.PIR 寄存器进行排序。 初始化序列包括以下步骤:4 n0 x: Z: Y& @( o 1. DDRCTRL 和 DDRPHYC 初始化包括内部时序模块(ITM)复位以及 DLL 复位和锁定& g8 h7 }$ H$ I, J0 u. Y 2. DDRPHYC I/O 初始校准(ZCAL),与 DLL 锁定同时启动 3. 通过模式寄存器写入和校准命令执行 SDRAM 初始化 4. 内置 DQS 门控训练(DQSTRN) 提示 • 在 SSTL 模式下为所有 SDRAM 设置 DDRPHYC I/O。 • DQS 门控训练是可选的。但是,建议在每次初始化时运行内置 DQS 门控训练。9 U u9 f; Y9 X5 u I- T5 a: t/ w0 n/ u. ^5 m" @/ | ' J2 M- A7 P0 K Y ![4BO13EBMSME)SKYY4@2~U]D.png 4BO13EBMSME)SKYY4@2~U]D.png](data/attachment/forum/202302/10/171552n65qjyjemq2u2smu.png)

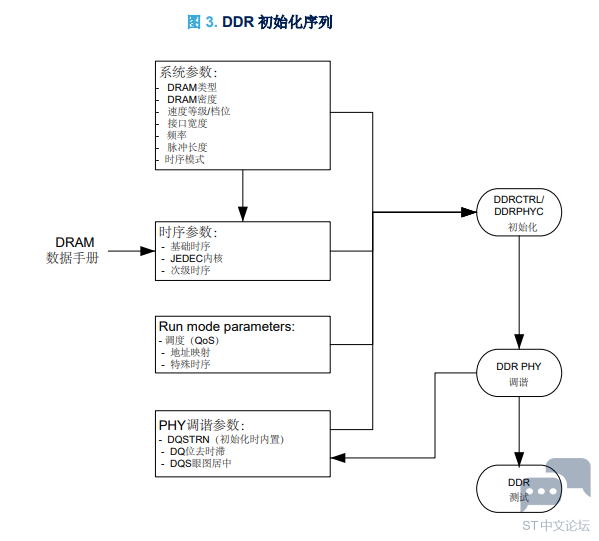

2.3DDRCTRL 配置4 _! s# X* h: B8 W" }& U 大多数 DDRCTRL 寄存器是静态的,并在 DDRCTRL 从复位状态释放和 AXI 端口使能前加载。这是在 DDR 软件驱动器的支持下实现的。3 J& P, c( d7 n+ A8 Q) B5 |) T% | 在 DDRPHYC 和 DDCTRL 完成初始化后,DDR 子系统就绪,使能 AXI 端口是最后一个步骤。 通过从 STM32CubeMX DDR 面板选择的菜单/选项提供的极少信息确定 DDRCTRL 和 DDRPHYC 寄存器的配置。然后,DDRSS 配置被保存并恢复到 DDRCTRL 和 DDRPHYC 寄存器,用于后续的复位和正常操作。9 B9 {8 n7 A6 H9 @; }" `+ i 2.3 DDR 配置 配置 DDR 所需的步骤如下:% I: y8 W( W# B& t3 ~9 X7 P/ y! y 1. 为 DDRCTRL 和 DDRPHYC 寄存器确定并设定合适值。 2. 启动 DDRCTRL 和 DDRPHYC 初始化序列。 3. 启动具有参数保存和恢复功能的 DDR 调谐(可选)。 4. 启动 DDR 测试(可选)。完整配置流程和参数如下图所示。 1 A7 y( S) a- i' p

7 B' r5 Y* [$ B$ ?( d9 {# b8 _ 2.4DDR PHY 调谐 除了使用强制 DQS 门控训练(DQSTRN)确定读脉冲期间 DQS 门控的最佳位置,DDRPHYC 还支持两种读取时序优化,即 PHY 调谐。, |& l' v |6 y9 u7 n9 m$ T) g+ l+ ?/ O 以下从 STM32CubeMX 驱动的软件例程支持 PHY 调谐,以优化读时序裕量:$ s7 e9 O1 e2 L8 L+ Y# N8 b- M( i6 e • DQS 门控训练(可在 DDR PHY 调谐期间以交互方式启动的软件) • DQ 位去时滞,以补偿 DQ 位通道读取延迟2 T) n6 A- E" g • DQS 眼图居中,用于调节 DQS/DQS#延迟以实现最佳 DQ 采样7 N9 W, o" M' z: e- c* f , O# W* z- Y& V3 s- x" { 2.5 DDR 测试 在初启阶段使用 DDR 之前, 必须运行 STM32CubeMx 建议的所有测试和级别。第 8 节 STM32CubeMX 的 DDR 测试中描述了 DDR 测试和测试流程,以及故障诊断和处理措施。DDR 子系统初启在 DDR 配置、调谐和压力测试成功后完成。保存配置参数用于正常运行模式初始化和 DDR run 模式。 % I1 u! e5 z" _, Y1 [ 完整版请查看:附件 ( V' x9 x, p! {" _ 6 l- i0 O& i" e |

基于STM32MP1和STM32MP2在嵌入式Linux平台上部署有效的安全保护机制

利用STM32MP1和STM32MP2为嵌入式Linux提供有效的安全措施:供当今决策者参考的3条宝贵经验

STM32MP1 WiFi连接

【STM32MP157】从ST官方例程中分析RPMsg-TTY/SDB核间通信的使用方法

【STM32MPU 安全启动】 TF-A BL2 TrustedBoot原理学习

《STM32MPU安全启动》学**结

《STM32MPU安全启动》学习笔记之optee 如何加载CORTEX-M核和使能校验

《STM32MPU安全启动》学习笔记之TF-A BL2校验optee和uboot的流程以及如何使能

《STM32MPU 安全启动》课程学习心得+开启一扇通往嵌入式系统安全领域深处的大门。

《STM32MPU安全启动》 课程学习心得

微信公众号

微信公众号

手机版

手机版