.png) STMCU小助手

发布时间:2023-2-21 21:18

STMCU小助手

发布时间:2023-2-21 21:18

|

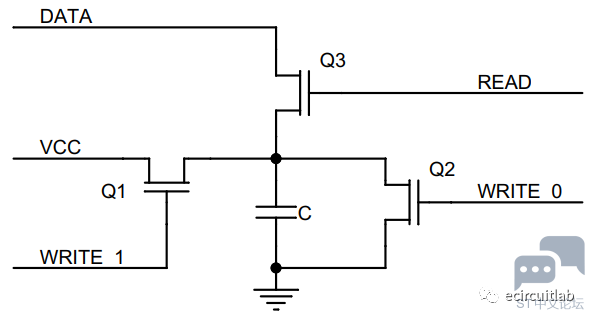

SDRAM简介 SDRAM(synchronous dynamic random-access memory)即同步动态随机存取内存。在介绍SDRAM前,我们先了解下DRAM(Dynamic random-access memory),DRAR中文译为动态随机存取内存,也叫动态随机存取器,为什么叫动态随机存取器,原因是它的实现原理跟静态存储器SRAM不一样,DRAM是在芯片里集成很多个阵列的电容,DRAM存储二进制数据0和1就是通过给这些阵充放电荷实现。一个简单的单个DRAM存储单元示例图如下图所示。

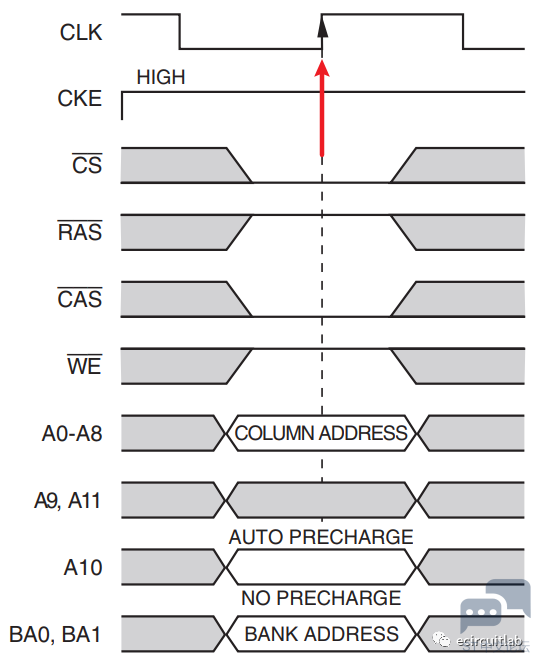

单个DRAM单元实现电容充放电原理 电容C用来存储电荷,信号WRITE 1、WRITE 0控制开关晶体管Q1和Q2给电容充电和放电,实现二进制1和0存储。信号READ控制开关晶体管打开把电容C接到数据线DATA上,芯片内部处理电路通过读取DATA线上的电压信号来判断DRAM存储单元存储的数据为二进制1还是0。 从原理上去看DRAM实现数据存取很完美,但实际芯片按照上面的原理做好电路后,开关晶体管和电容本身都会有漏电流。漏电流会导致一个特别糟糕的情况,电容存储的电荷会慢慢通过漏电流方式流失掉,当电荷流失到一定的量后,内部电路读取电容的电压去判断数据时,就不能正确判断为二进制1了,这种情况下数据是错误。这样的错误肯定是不允许发生的,解决办法是通过定时刷新方式给电容充电,保证电容存储的电荷量稳定在理想的状态。因为这样的过程是一个一直的动态过程,动态随机存取器的名称由此而来。而SDRAM是DRAM的一种操作方式,如下图所示,SDRAM读写数据时,是通过在时钟的上升沿同步获取控制、数据信号,所以叫做同步动态随机存取器。 SDRAM在时钟CLK上升沿时同步获取控制、数据信号

DRAM和SRAM优缺点: 1. SRAM读写速度快,DRAM读写速度慢。 2. SRAM耗电量低,DRAM耗电量大。 3. SRAM制造成本高,容量低,DRAM制造成本低,容量大。

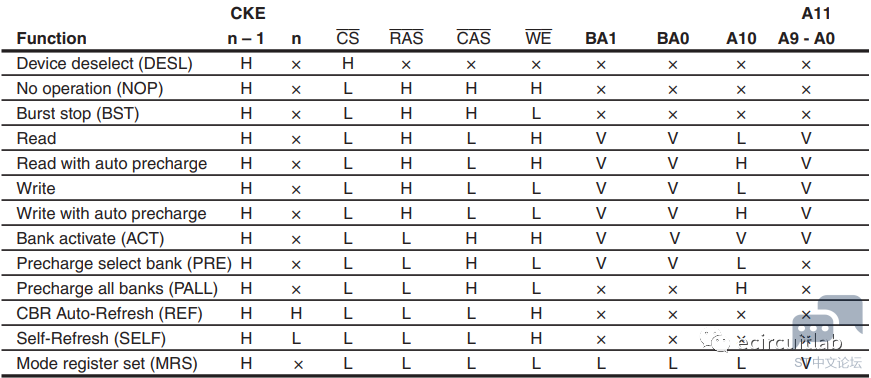

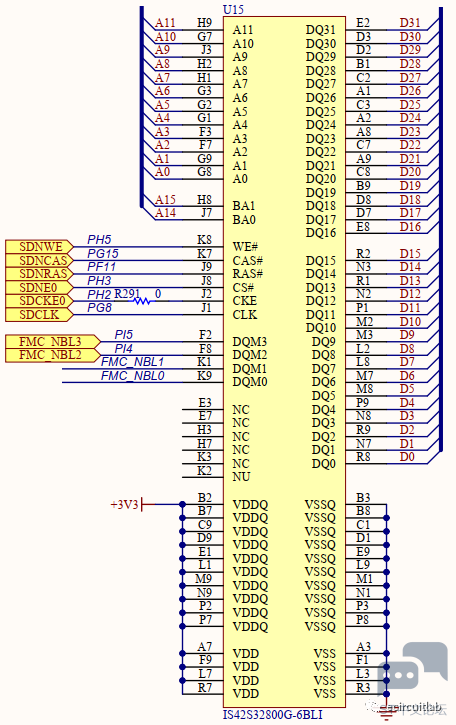

SDRAM主要信号如下(256Mb容量示例): A0-A11: 地址信号。BA0-BA1: Bank选择信号。DQM0-DQM3: 读写数据掩码控制信号。 DQ0-DQ31: 数据信号。 CKE: 时钟使能信号。 CLK: 时钟信号。 CS: 片选信号。 CAS: 列地址选通控制信号。 RAS: 行地址选通控制信号。 WE: 写使能信号。 在上述罗列的信号中,A0-A11、BA0-BA1、CKE、CS、CAS、RAS、WE的不同组合,可以构成不同的Command如下图所示。

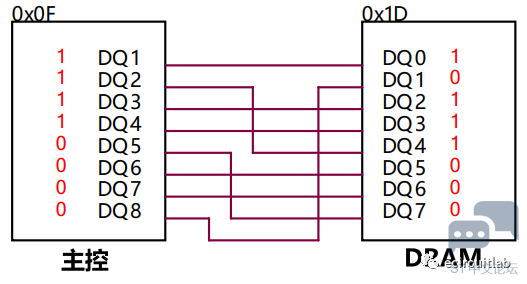

DRAM Commad真值表 这里介绍的组内数据线调换不影响数据的正确性,可能会有很多人困惑,我做了个图如下说明解释。如下图中,左侧为主控信号,右侧为DRAM。主控要写数据0x0F到DRAM中,因为数据线在DRAM端被调换了,所以实际到DRAM内的数据变为0x1D。这样看像是数据错了,但我们再看主控从DRAM读数据的情况,主控读数据时,DRAM内的0x1D顺着信号线原路返回,变成了0x0F,错错得正。所以DRAM信号线组内调线序不影响数据读写错误,但不能跨组调,不能跨组调的原因是即使有错错得正的逻辑,但是如果DQM信号没有使能对应的Byte,那就会导致数据缺失,所以必然出错。

在DRAM端做数据组内调换,不影响主控读写数据的正确性 STM32上的SDRAM电路设计 参考ST评估板MB1219的SDRAM部分电路如下,STM32使用SDRAM的目的是扩充芯片内存,由FMC接口控制,电路没什么复杂的,设计时注意了解各个信号的作用,然后参考规格书把信号一一对应连接上即可。评估板MB1219使用的主控是STM32F769NI,参考STM32F7xx规格书第86页的Table 12. FMC pin definition的SDRAM栏,有详细的信号定义。下图中的BA0和BA1接的信号为A14和A15,这里没有错,是ST工程师在设计评估板时,FMC总线上还挂了SRAM和Nor Flash,而A14和A15是SRAM和Nor Flash的,但对应SDRAM实际为BA0和BA1。

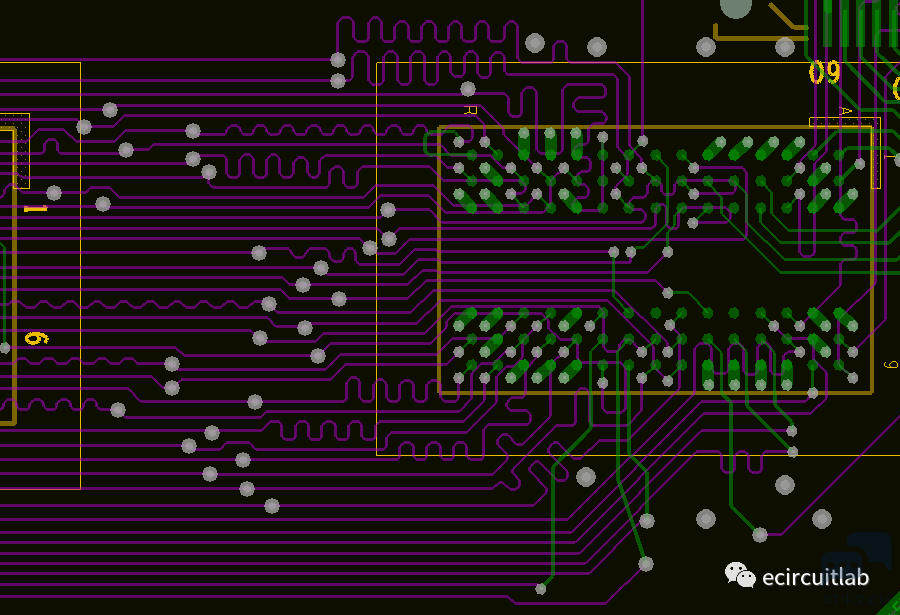

SDRAM参考设计电路 完成原理图设计,后面剩下的是大家比较关心的Layout要不要做信号线等长的问题,这个问题在网上一直是很多人热衷讨论的一个问题,各有说法。其实对于SDRAM,只要走线不会长度差得特别离谱,比如差不多十几个厘米这样的,不等长影响不会很大,但如果PCB空间资源足够的话建议按照500mil的规则做等长。如下图ST的评估板MB1219就做了等长。

条件允许,推荐SDRAM做500mil约束等长 转载自: ecircuitlab |

分享STM32资料-采用 STM32U031R8 MCU 的 STM32 Nucleo-64 开发板,官方资料,数据手册等资料

HRTIM 指南

使用 STM32 的 DWT 单元监控内存

DAC,COMP,HRTIM Fault 功能的使用

一个软件引起的 LSE 驱动不良的问题

STM32 GUI LTDC 最大像素时钟评估方法

STM32 Cordic 运算速度评估

全新OpenSTLinux 6.1版本发布

ST-LINK Utility介绍、下载、安装和使用教程

【2025·STM32峰会】GUI解决方案实训分享1-对LVGL咖啡机例程的牛刀小试以及问题排查

微信公众号

微信公众号

手机版

手机版