|

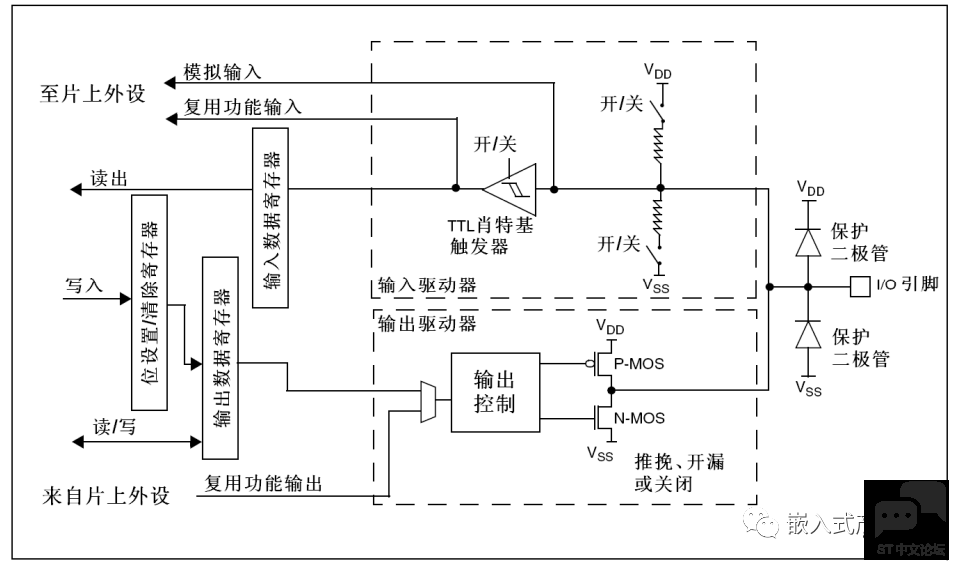

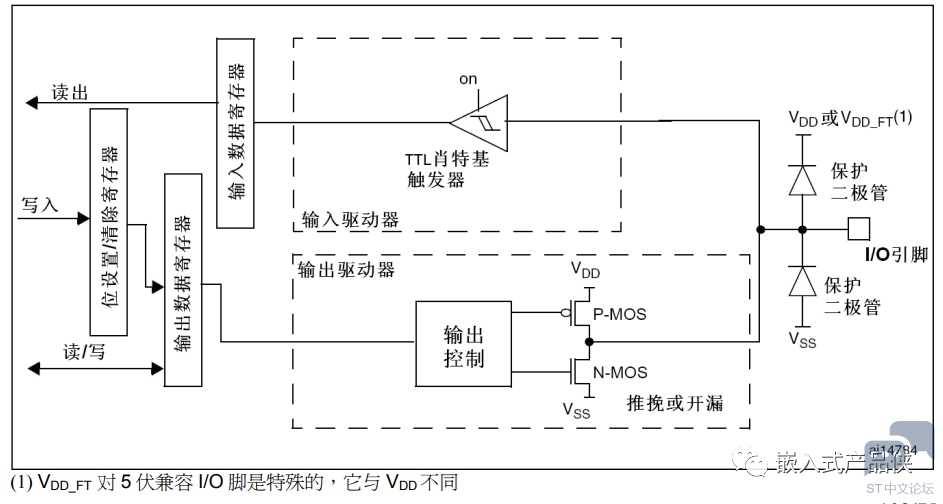

一、GPIO功能描述 每个GPIO端口有两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH) ,两个32位数据寄存器 (GPIOx_IDR和GPIOx_ODR) ,一个32位置位/复位寄存器(GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR)和一个32位锁定寄存器(GPIOx_LCKR)。GPIO端口的每个位可以由软件分别配置成多种模式。 输入浮空 输入上拉 输入下拉 模拟输入 开漏输出 推挽式输出 推挽式复用功能 开漏复用功能 每个I/O端口位可以自由编程,然而必须按照32位字访问I/O端口寄存器(不允许半字或字节访 问)。GPIOx_BSRR和GPIOx_BRR寄存器允许对任何GPIO寄存器进行读/更改的独立访问。这 样,在读和更改访问之间产生IRQ时不会发生危险。 图1 I/O端口位的基本结构图片

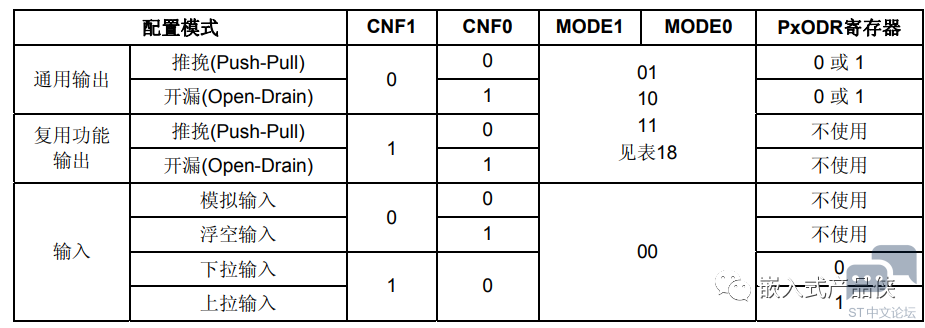

图2 端口位配置表图片

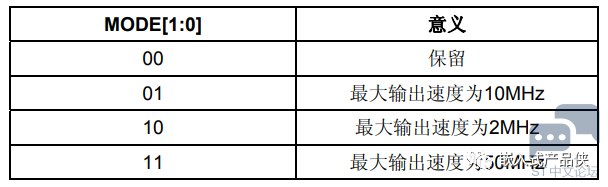

图3 输出模式位

二、通用I/O(GPIO) 复位期间和刚复位后,复用功能未开启,I/O端口被配置成浮空输入模式(CNFx[1:0]=01b, MODEx[1:0]=00b)。复位后,JTAG引脚被置于输入上拉或下拉模式: PA15:JTDI置于上拉模式 PA14:JTCK置于下拉模式 PA13:JTMS置于上拉模式 PB4:JNTRST置于上拉模式 当作为输出配置时,写到输出数据寄存器上的值(GPIOx_ODR)输出到相应的I/O引脚。可以以推挽模式或开漏模式(当输出0时,只有N-MOS被打开)使用输出驱动器。 输入数据寄存器(GPIOx_IDR)在每个APB2时钟周期捕捉I/O引脚上的数据。 所有GPIO引脚有一个内部弱上拉和弱下拉,当配置为输入时,它们可以被激活也可以被断开。 三、单独的位设置或位清除 当对GPIOx_ODR的个别位编程时,软件不需要禁止中断:在单次APB2写操作里,可以只更改 一个或多个位。 这是通过对“置位/复位寄存器”(GPIOx_BSRR,复位是 GPIOx_BRR)中想要更改的位写’1’来 实现的。没被选择的位将不被更改。 四、外部中断/唤醒线 所有端口都有外部中断能力。为了使用外部中断线,端口必须配置成输入模式。 五、复用功能(AF) 使用默认复用功能前必须对端口位配置寄存器编程。 对于复用的输入功能,端口必须配置成输入模式(浮空、上拉或下拉)且输入引脚必须由外部驱动 对于复用输出功能,端口必须配置成复用功能输出模式(推挽或开漏)。 对于双向复用功能,端口位必须配置复用功能输出模式(推挽或开漏)。这时,输入驱动器被配置成浮空输入模式。如果把端口配置成复用输出功能,则引脚和输出寄存器断开,并和片上外设的输出信号连接。如果软件把一个GPIO脚配置成复用输出功能,但是外设没有被激活,它的输出将不确定。 六、软件重新映射I/O复用功能 为了使不同器件封装的外设I/O功能的数量达到最优,可以把一些复用功能重新映射到其他一些 脚上。这可以通过软件配置相应的寄存器来完成(参考AFIO寄存器描述)。这时,复用功能就不再映射到它们的原始引脚上了。 七、GPIO 锁定机制 锁定机制允许冻结IO配置。当在一个端口位上执行了锁定(LOCK)程序,在下一次复位之前,将 不能再更改端口位的配置。 八、输入配置 当I/O端口配置为输入时:、 输出缓冲器被禁止 施密特触发输入被激活 根据输入配置(上拉,下拉或浮动)的不同,弱上拉和下拉电阻被连接 出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器 对输入数据寄存器的读访问可得到I/O状态 下图给出了I/O端口位的输入配置

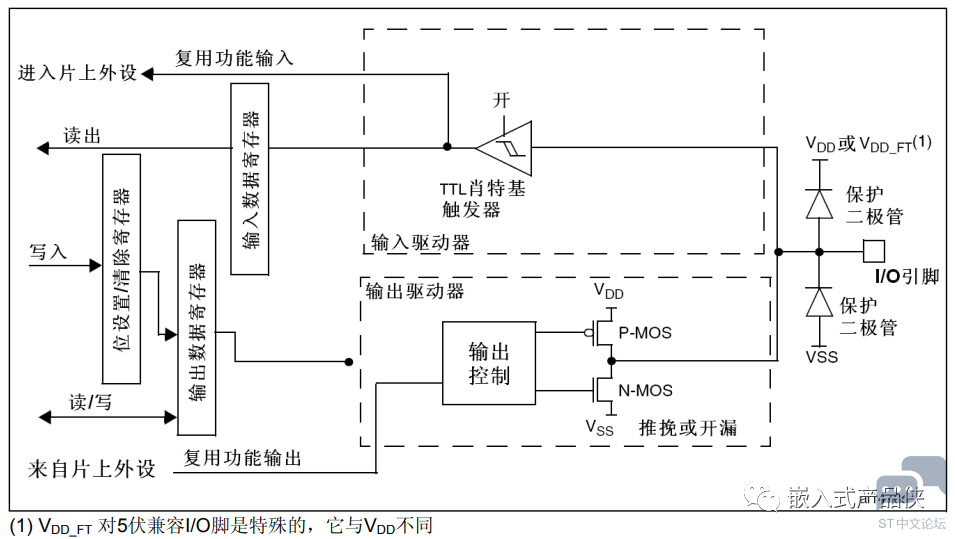

九、输出配置 当I/O端口被配置为输出时: 输出缓冲器被激活 开漏模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将端口置于高阻状态(PMOS从不被激活)。 推挽模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将激活P-MOS。 施密特触发输入被激活 弱上拉和下拉电阻被禁止 出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器 在开漏模式时,对输入数据寄存器的读访问可得到I/O状态 在推挽式模式时,对输出数据寄存器的读访问得到最后一次写的值 下图给出了I/O端口位的输出配置

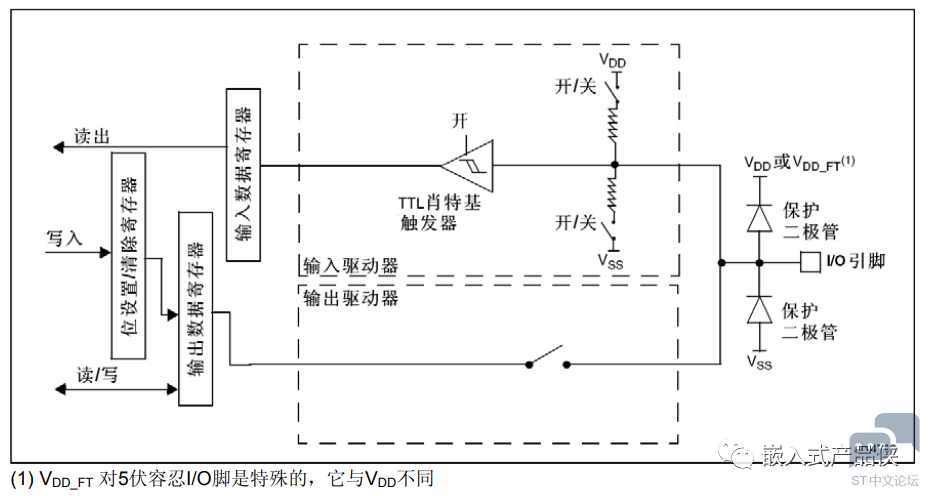

十、复用功能配置 当I/O端口被配置为复用功能时: 在开漏或推挽式配置中,输出缓冲器被打开、 内置外设的信号驱动输出缓冲器(复用功能输出) 施密特触发输入被激活 弱上拉和下拉电阻被禁止 在每个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器 开漏模式时,读输入数据寄存器时可得到I/O口状态 在推挽模式时,读输出数据寄存器时可得到最后一次写的值 下图给出了复用功能配置图片

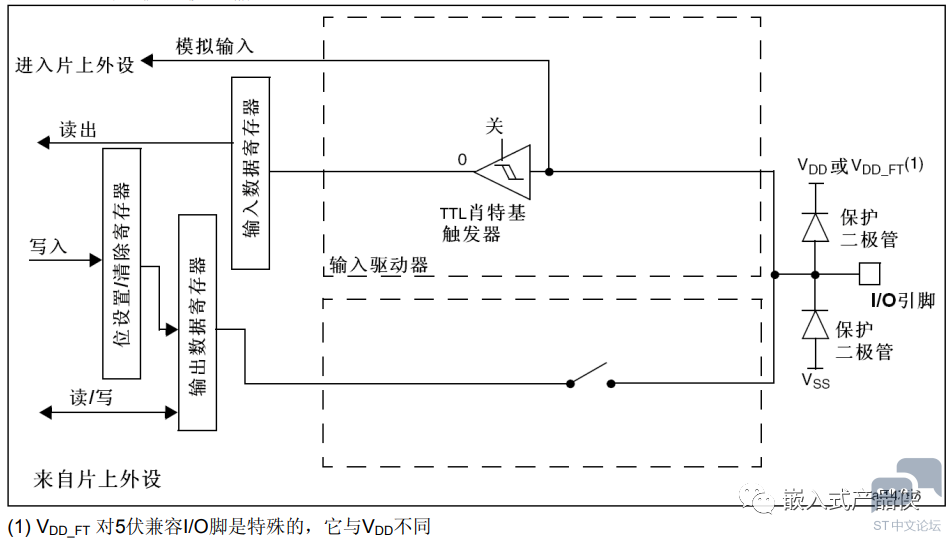

十一、模拟输入配置 当I/O端口被配置为模拟输入配置时: 输出缓冲器被禁止; 禁止施密特触发输入,实现了每个模拟I/O引脚上的零消耗。施密特触发输出值被强置 为’0’; 弱上拉和下拉电阻被禁止; 读取输入数据寄存器时数值为’0’。 下图示出了I/O端口位的高阻抗模拟输入配置: 转载自: 嵌入式产品侠 如有侵权请联系删除 |

STM32 硬核调试技巧:用 DWT 硬件监控内存读写与函数调用

巧用 Linker 自定义变量,破解 STM32 Flash 全片自检 ROM 大小配置难题

实战经验 | LAT1578 SAU对NSC分区的影响

【板卡测评】STEVAL-STWINKT1B 上电后任意工具读出 ACC/GYRO/MAG 实时数据并截图

F429I-DISC1体验报告(1)久经沙场,锋芒依旧丨TouchGFX开发F429丨国庆开发板测评活动

实战经验 | KEIL环境下printf导致程序无法执行的解决方案

经验分享 | 程序换个IDE就不运行了?

经验分享 | 常被误解的开、关总中断话题

【STM32U3评测】SPIDMA发送

【STM32U3评测】实现双通道串口通信系统

微信公众号

微信公众号

手机版

手机版