求P-NUCLEO-LRWAN3中的STM32F746ZG的网关固件bin文件

STM32 用主从定时器方式实现DSP QEP模块的QCTMR功能,异常

TIM 单脉冲输出后的电平如何设置?

stm32h7 定时器输出比较模式+dma,生成脉冲异常

STM32CubeMX配置STM32F103C8T6 RTC分频器问题

STM32G473,PA3导致定时器定时误差过大

定时器输出PWM控制电机的问题

stm32u575 gpdma burst length=1 配置其他数值不工作

STM32F769I-DISCO开发包LCD DSI示例程序如何回读LCD 驱动IC的寄存器?

COD

微信公众号

微信公众号

手机版

手机版

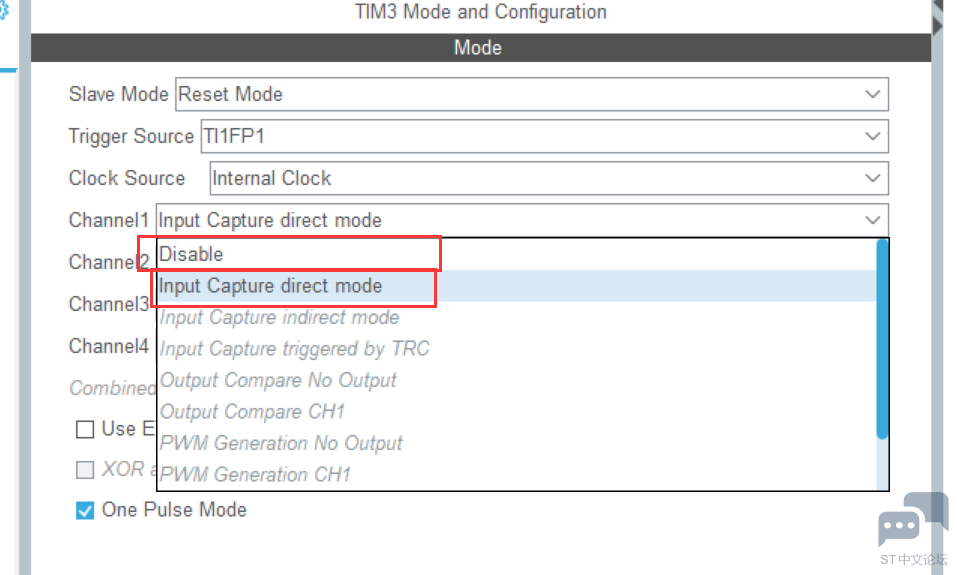

问题已经找到了,是因为使用cubemx配置timer的输入捕获时,并没有选择Input Capture direct mode。因为当时选择了Trigger Source后,在cubemx的stm32芯片引脚图上就会有对应的通道选择上,就以为不用选择模式就可以,而且当时在测试的时候,也是能够成功捕获到上升沿,就没有注意到这个问题。实际上,如果这里不选择Input Capture direct mode,对应的引脚实际上是输出,所以输出阻抗就非常低,而外部如果提供足够大的电流,即使是输出,由于内部模式是触发,依旧能够采集到信号上升沿。

其次,不同的配置会引起电流的变化,这种变化可能会导致高输出祖杭的信号变化。

是的,我现在的现象是,信号直接作用在stm32的引脚上是能够触发定时器的。但是在我的硬件电路上,输入的信号实际上经过了一个电平转换器,我用示波器检测经过电平转换器前和之后的信号,发现信号有很大的衰减。在硬件检查也没有什么太大的问题,我现在想着是在stm32端的定时器gpio引脚上,给一个上拉电阻,看能不能解决这个现象,发现并不能在输入捕获使能后有一个上拉的电平

这个是使能输入捕获前和使能输入捕获后在stm32引脚上检测到的信号,可以看到信号在使能输入捕获后有了很大的衰减。在硬件电路上是加了一个电平转换的芯片,可能是由于电平转换芯片的影响,但是这又很难解释使能输入捕获前信号是正常的。