|

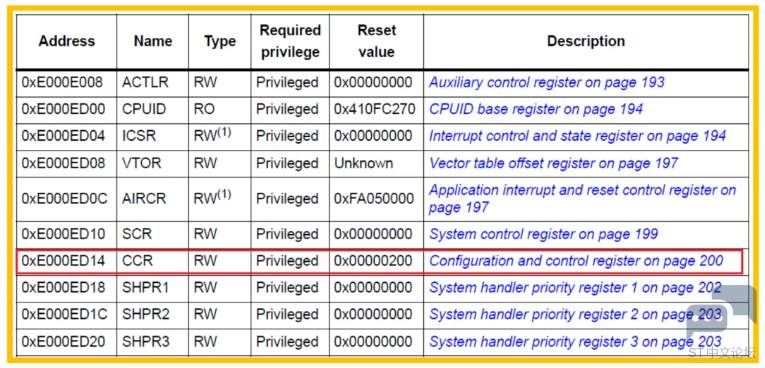

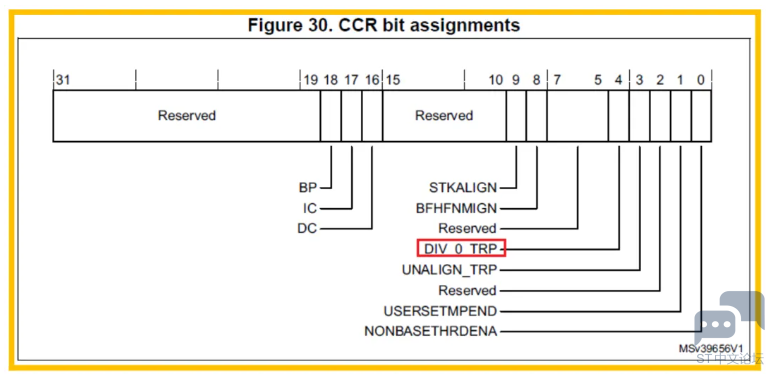

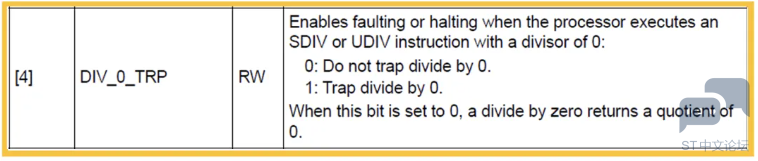

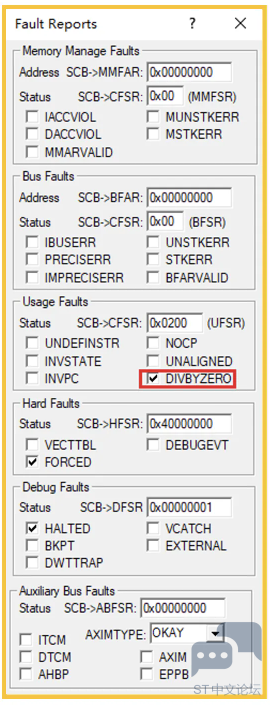

1. 前言 除0操作属于错误操作,在ARM Cortex-M平台上会有相应的报错机制。但这边会涉及到整型数的除0以及浮点数的除0,另外还会涉及错误产生后的报错机制,是中断还是错误位,本文会对这个报错机制加以说明。使用STM32H723做为测试芯片。 2. 整形数除0操作报错 默认情况下,STM32H723对整形数的除0操作,会忽略掉错误,原因在于默认情况下 SCB->CCR寄存器默认配置中这个除0操作是非捕获状态,如果想要系统报错,需要把 DIV_0_TRP这个位置1,这样,当执行除0操作的时候会进入hardfault,并且有标志位产生。

▲ 图1. SCB CCR默认地址和复位初值

▲ 图2. DIV_0_TRP位于bit4

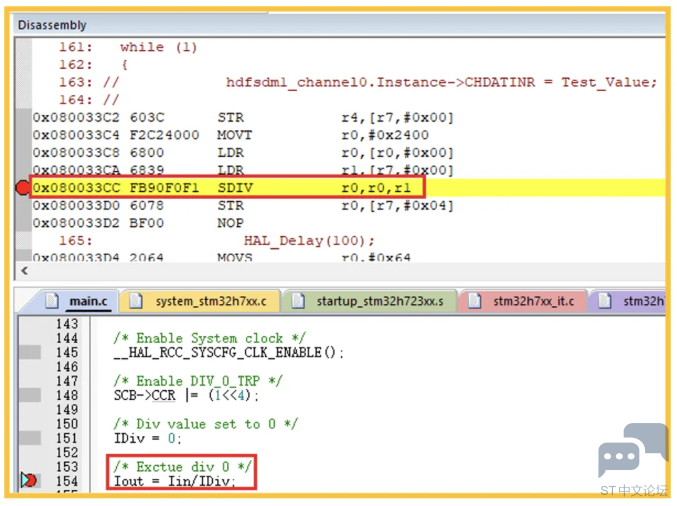

▲ 图3. DIV_0_TRP参数说明 测试执行整型数除0操作代码。

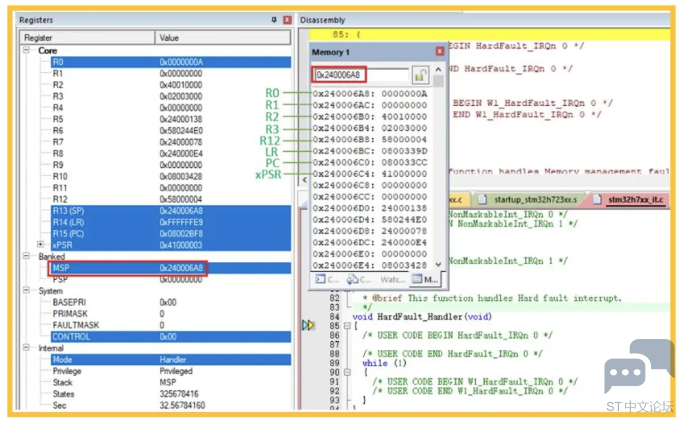

▲ 图4. Fault Report-除0错误

▲ 图5. 查看进入Hardfault的程序位置

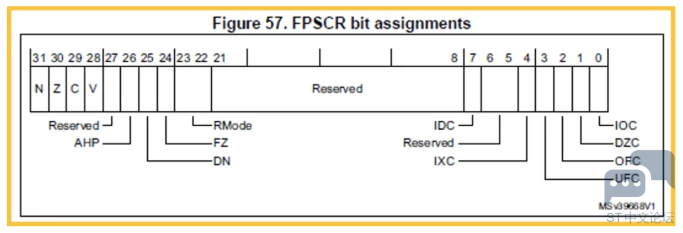

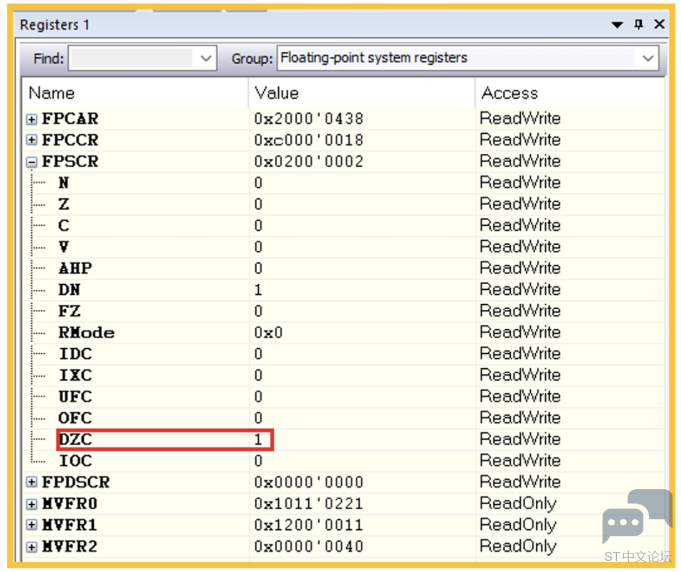

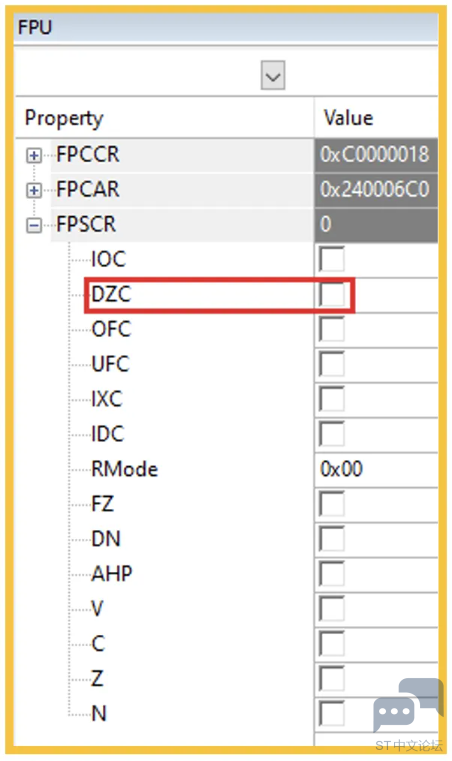

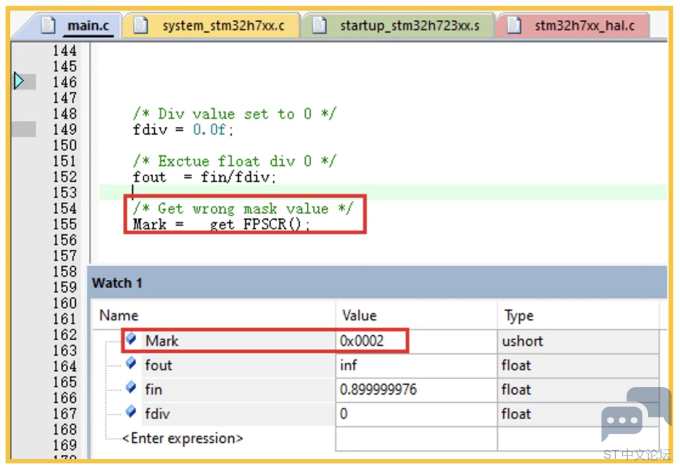

▲ 图6. 找到因为除0导致的进入Hardfault 3. 浮点数除0的报错机制 浮点数的除0操作,没有专门的Hardfault触发机制,也就不能产生中断,只能通过对FPU单元的读取进行判别,而且在调试模式下,通过IAR读取寄存器的结果是正确的,而通过Keil的读取会有错误,实际已经发生了浮点除0操作,但Keil的FPU->SCR寄存器DZC没有置位。

▲ 图7. FPSCR寄存器 执行浮点除0的测试代码:

▲ 图8. IAR的浮点除0后DZC标志位置位

▲ 图9. Keil浮点除0后DZC标志位有误 读取FPSCR寄存器,返回错误码0x02(除0操作)。

▲ 图10. 读取FPSCR 4. 结论 本文通过对除0操作的报错机制做细致说明,可以看到整型除0可以有Hardfault的中断产生,而浮点的除0只能通过标志位判别,实际使用过程中尽量避免这种错误的操作。 ▼▼▼ 点击按钮下载《Cortex-M核除0操作的报错机制话题》原文档。 LAT1423_Cortex-M核除0操作的报错机制话题_v1.0.pdf

(515.22 KB, 下载次数: 0)

LAT1423_Cortex-M核除0操作的报错机制话题_v1.0.pdf

(515.22 KB, 下载次数: 0)

|

经验分享 | LAT1422 STM32 AFCI 方案 TensorBoard 的使用介绍

STM32 LAT实战经验资料汇总分享(260205)

我中奖啦,收到了STM32开发板,足足开心了一整天啊

STM32嵌入式常见面试知识点汇总

经验分享 | STM32 HRTIM实现复杂波形的配置演示

经验分享 | STM32G0 Stop模式下LPUART唤醒演示

经验分享 | STM32G4系列是否支持位带操作

经验分享 | 一段莫名的延时输出问题

经验分享 | 发不出去的hello问题

基于编码器信号的PWM输出示例

微信公众号

微信公众号

手机版

手机版