.png) STMCU小助手

发布时间:2021-12-26 17:22

STMCU小助手

发布时间:2021-12-26 17:22

|

STM32H7的Cache与Buffer TCM和Cache的区别 …使用lwip用到了mpu,对于内存管理产生了很多的疑问,需要统一解决一下,不然用起来总有些不安。 STM32H7使用的内存不是连续的,而是被划分为多段。

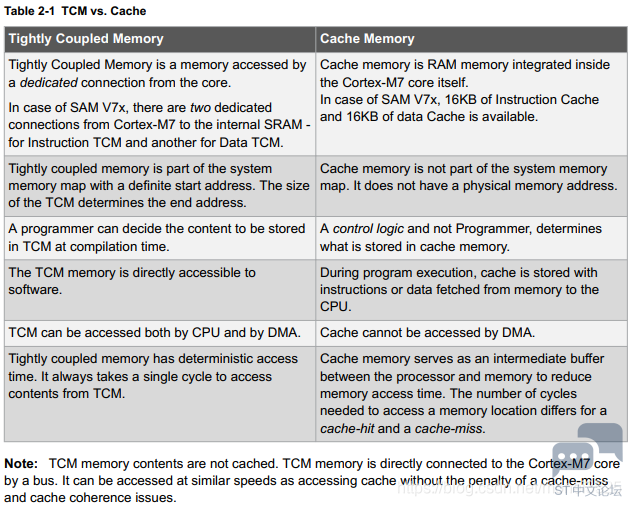

TCM内存段是和CPU同频率的,不需要也不能用Cache。用好TCM的优先级应该排在用好Cache的前面。 Cache处于核心里面,作为低速内存加速器使用,获得增益最大的是位于AXI总线上的比如内部Flash、内部SRAM、通过FMC或者QSPI控制器连接的外部sram。Cache使得低速Sram获取与高速TCM差不多的速度。使用Cache加速很有意义,不然400M的cpu变200M,相当于H7变F4,选择H7的cpu将变得没有意义。

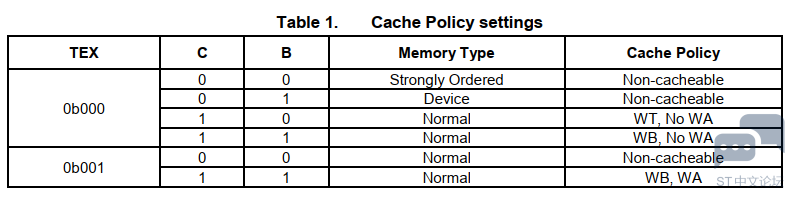

内存类型 内存类型分为Normal以及Device和Strongly-ordered, ![I5LW_ZQ_SY3W%I@][7RY56T.png I5LW_ZQ_SY3W%I@][7RY56T.png](data/attachment/forum/202112/26/172236q4gfkm3bm299xkun.png)

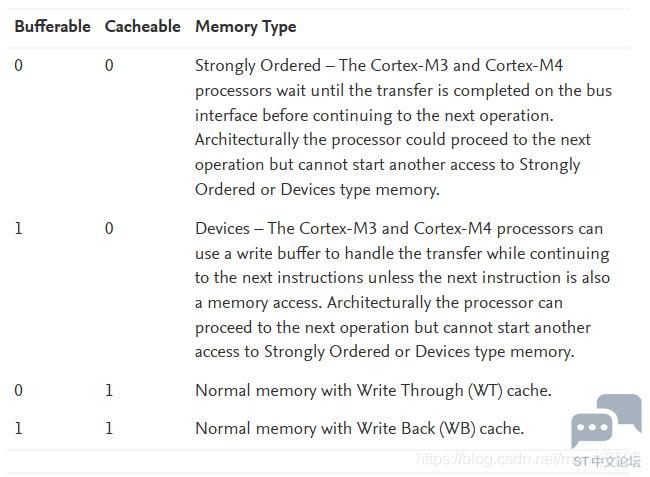

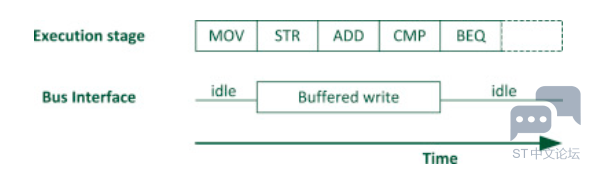

Write-buffer是什么? Device和Strongly-Ordered类型时候提到了write-buffer,它属于cpu核心,cache经常与write-buffer一起使用,使用writer-buffer的目的是将处理器和cache从较慢的对主存的写操作中脱离出来。 Write buffer可以缓存8个word的数据和4个独立的地址,可以enable或者disable使用ARM核心控制寄存器 W的bit3。同时还要受到内存管理页表的一个bit控制,所以使用Write-Buffer,MMU必须已经使能(控制寄存器的bit0)。MMU-Memory Management Unit 通常情况下的配置都是主内存允许bufferable,但是I/O 空间 unbufferable 当CPU执行一个写操作时,根据配置情况执行写入操作。

如果程序中使用DMB and DSB,处理器会等到write-buffer内指令完成,再进行后续指令操作,如果过程中发生中断,中断返回后继续write-buffer清空等待。 DMB或者DSB被称为 显式限制操作 explicit barrier。

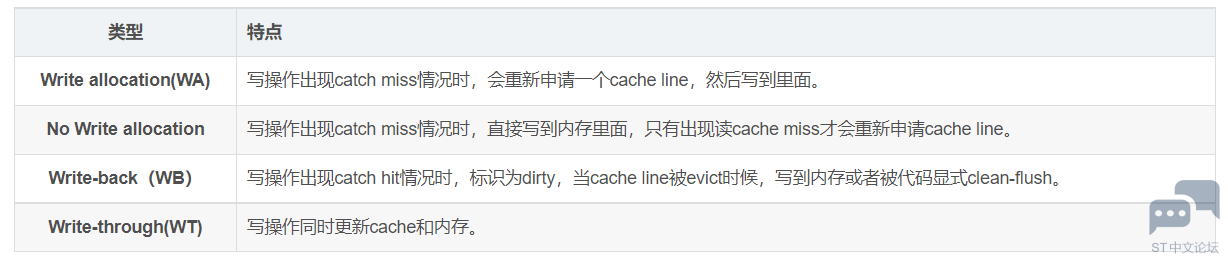

Memory Attrabute Normal模式下可以设定的几种

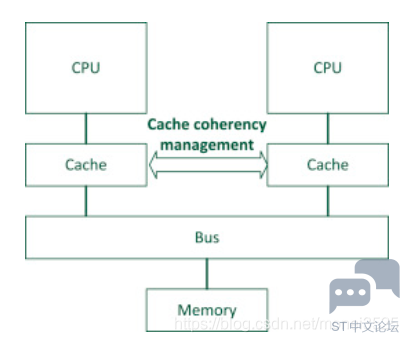

Shareable属性 共享属性设计的意义在于,多个bus master读写情况下需要cache保持同步,对于CortexM7,只有L1-Cache,如果设置了Shared相当于non-cacheable。

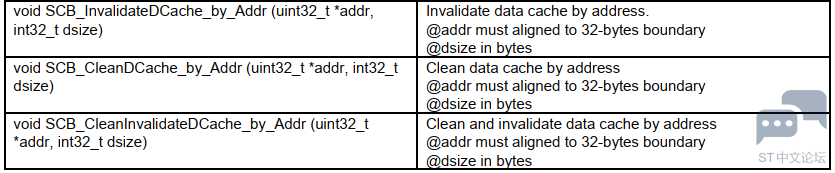

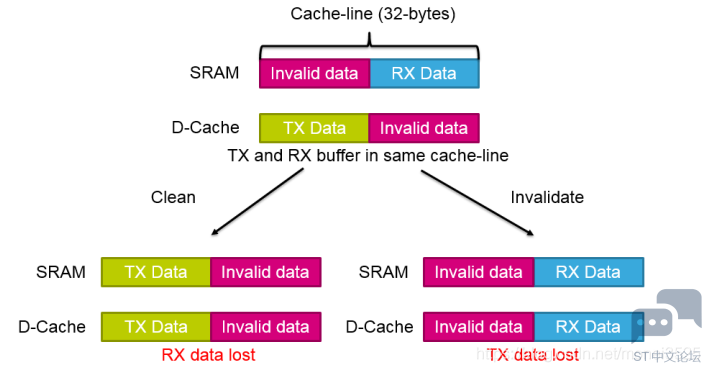

内核操作函数 内核操作函数包含以下几种,主要包含两种操作:clean和invalidate。 clean:将cache中的信息写到sram,相当于用cache信息覆盖sram; invalidate:使cache失效,相当于用sram信息覆盖cache; 二者为相反的操作。

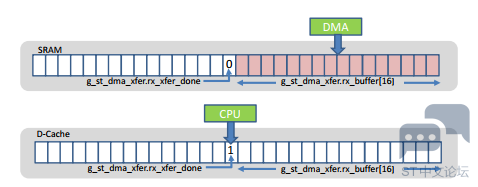

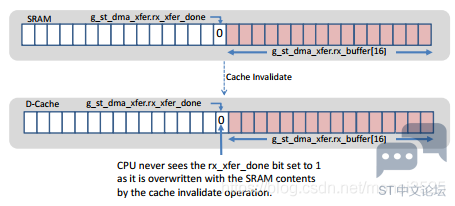

内存对齐问题 使用cache时,dma的buffer必须32byte对齐,不然可能会出现问题。比如下面的情况:

如果DMA的buffer只有16字节,DMA读取操作后,DMA控制器将接收到的数据写到了sram里面,然后进入DMA接收中断函数,cpu把成功读取的标识bool变量写为true,实际上写操作只是写在D-Cache里面,暂时没有写到sram。

如果此时cpu需要读取dma内容,需要对Dcache进行invalid操作,32个字节将一起更新,bool变量旧值0将覆盖新值1。cpu读不到中断函数写的bool变量信息。

可见: clean操作或者Invalidate操作都可能丢东西,使用上需要注意。经验是如果一段内存用来写dma外设,就不要读它,保证随时都可以clean;同样如果一段内存用来接收DMA外设传入信息,就不要用cpu写它,保证随时都可以invalidate。

|

STM32和Arduino对比,谁更耐打?

STM32 LL为什么比HAL高效?

STM32H7 SPI Underrun 特性实战指南:配置、行为与传输可靠性优化

【STM32H750-DK 车辆仪表】6.模拟温度和胎压监测

【STM32H750-DK 车辆仪表】5.油表

【STM32H750-DK 车辆仪表】4.仪表时钟

【STM32H750-DK 车辆仪表】3.车速控制UI

【STM32H750-DK 车辆仪表】2.与板卡交互

【STM32H750-DK 车辆仪表】1.灯光控制UI

STM32应用过程中与电源相关的案例分享

微信公众号

微信公众号

手机版

手机版