.png) STMCU小助手

发布时间:2021-12-24 18:00

STMCU小助手

发布时间:2021-12-24 18:00

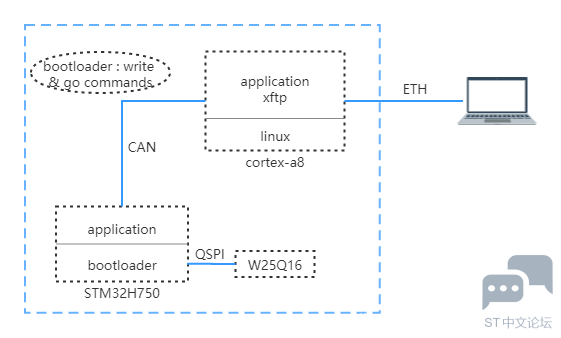

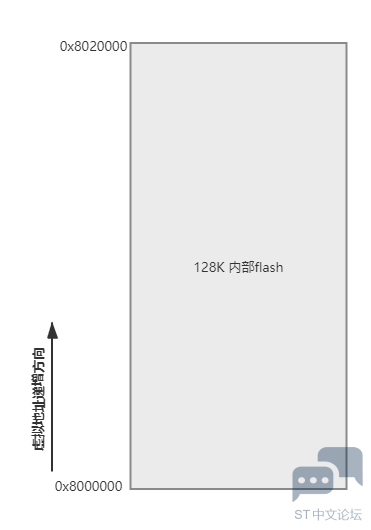

最近公司开发的一个项目使用到STM32H7系列芯片,由于该系列芯片内部flash只有128k,为了方便产品的远程升级,需要开发对应的升级协议及bootloader引导程序。由于片内flash容量不够,需要采用外挂flash的方式存储应用程序,片内flash单纯作为bootloader引导程序存储空间。为了节省成本采用单QSPI flash外挂BANK2作为应用程序外部存储。

1.STM32H7启动流程 IAR工程建立后,系统默认生成的启动文件为startup_stm32h750xx.s,默认生成工程一般在EWARM目录下

定义了一个 CSTACK 的段,然后在启动代码中先声明这个段 定义 .intvec 段,中断向量独立在一个叫 .intvec 的段当中,这个段是 4字节对齐(2^2)所以用 DATA 来首先处理向量的入口地址为 4的倍数,然后放向量表 DATA 进入DATA模式 DCD sfe(CSTACK) 通过 SFE 运算得到改段的结束地址(注意这个运算是在link的时候完成,链接文件为xxxx.icf,比如:stm32h750xx_flash.icf) 文件剩下为定义中断向量表。

THUMB 进入THUMB模式(THUMB-2指令集) 启动文件先使用PUBWEAK 指令声明Reset_Handler为弱定义 SECTION .text:CODE:NOROOT:REORDER(2) 从.text段开始 LDR R0, =SystemInit 将SystemInit指针地址赋值给R0 SystemInit 函数一般由STM32 库提供,对于STM32 HAL库,该函数一般位于system_stm32h7xx.c文件中

SystemInit 函数完成系统时钟、RAM、中断向量表地址的初始化。

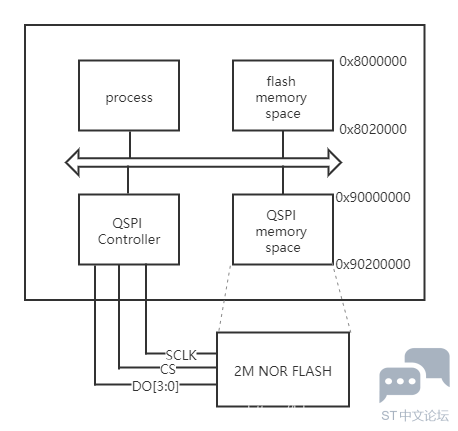

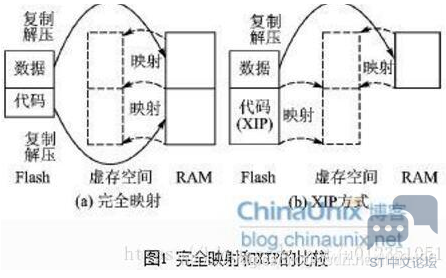

__iar_program_start 函数一般都IAR系统提供,,我们可以在IAR工程中Option进行修改 如果想具体了解__iar_program_start干了那些事情,可以参考《在main()之前,IAR都做了啥?》 启动文件主要完成如下工作,即程序执行过程: - 设置堆栈指针SP = __initial_sp。 - 设置PC指针 = Reset_Handler。 - 设置中断向量表。 - 配置系统时钟。 - 配置外部SRAM/SDRAM用于程序变量等数据存储(这是可选的)。 - 跳转到C库中的 __main ,最终会调用用户程序的main()函数。 2.XIP技术 XIP,executed in place,本地执行。操作系统采用这种系统,可以不用将内核或执行代码拷贝到内存,而直接在代码的存储空间直接运行。采用这样的技术既可以节省可用内存又可以减少加载的时间。应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。flash内执行是指nor flash 不需要初始化,可以直接在flash内执行代码。但往往只执行部分代码,比如初始化RAM.比如在arm处理器中,Nor flash就存放了引导系统启动的Bootloader,不过大小比较小(仅2M空间)。

但是,Flash的存储器访问周期要比RAM大得多,在使用XIP技 术后可能会降低程序的运行速度,不过由于CPU的指令预取机制以及Cache机制,实际使用起来并不会明显降低应用程序的运行速度。

而右边的图,是针对Nor Flash的,这个很明显,CPU可以像读内存一样,直接跟Nor flash交互,即可以直接从Nor Flash中取指令,然后交给译码模块和执行模块进行执行,可以说,相比较Nand flash,Nor flash的操作对于CPU来说,简直就像是面对面一样。 进一步, 为什么Nor Flash可以实现XIP,而Nand flash就不行呢? 有一个概念:嵌入式系统中代码的执行方式: (1)完全映射:嵌入式系统程序运行时,将所有代码从非易失存储器(Flash、ROM等)复制到RAM中运行。 (2)按需分页:只复制部分代码到RAM中,这种方法对RAM中的页进行导入/导出管理,如果访问位于虚存中但不在物理RAM中会产生页错位,这时才将代码和数据映射到RAM中。 (3)XIP:在系统启动时,不将代码复制到RAM,而是直接在非易失性存储位置执行,RAM中只存放需要不断变化的数据部分,如下图

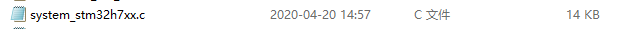

如果非易失性存储器(Flash)的读取速度与RAM相近,则XIP可以节省复制和解压的时间,Nor flash和rom的读取速度比较看(约100ns),比较适合XIP,而Nand flash的读取操作是基于扇区的,速度相对很慢(us级),因此不适合实现XIP系统,不过Nand flash的写速度比Nor的快,更适合做存储和下载系统。 解释二: 两种芯片的结构不同 NOR flash之所以可以片内执行,就是因为他符合CPU去指令译码执行的要求。CPU送一个地址出来,Nor flash就能给出一个数据让CPU执行,中间不需要额外的处理操作。 NAND flash不一样是因为nand flash有地址,数据,命令共用IO口的问题,cpu把地址发出来之后,并不能直接得到数据,还需要控制线的操作才能完成。就是他没有专用的SRAM接口。 解释三: 芯片内执行主要是是看芯片可不可以线性存储代码(假如硬件支持芯片接口),只要能保证芯片的存储空间是线性的(也就是无坏块),都可以片上执行,在读取Flash时候,容易出现“位翻转(bitconvert),在Flash的位翻转(一个bit位发生翻转)现象上,NAND的出现几率要比NorFlash大得多。这个问题在Flash存储关键文件时是致命的,所以在使用NandFlash时建议同时使用EDC/ECC等校验算法。 ” 但是,如果能保证不出错,也还是可以进行XIP,可以在其上执行代码的: “所谓XIP,就是CODE是在FLASH上直接运行. NANDFLASH只是不适合做XIP,但并不是不能做XIP“ 要一段CODE能够正确的运行,要保证它的CODE是连续的,正确的. 由于一些电气特性的原因,NOR FLASH能够做到这一点,不存在坏道或坏块,所以能够做XIP. 而对于NAND FLASH, 它只保证它的BLOCK 0是好的,其他的块并不保证,虽然出错的几率比较低,但还是有出错的可能,所以CODE可能无法连续正确地执行. 但只要你有额外的保障措施,比如说在执行CODE之前去做一次ECC校验,来确保CODE是连续正确的.那你也可以做XIP. 有人这么做了,而且也证明是成功的 由于芯片外挂的是W25Q16 为NOR flash,支持XIP,并且STM32H7系列芯片QSPI FLASH支持内存映射模式。STM32H7芯片可以将W25Q16芯片内的应用程序映射到地址0x90000000,虚拟为芯片内部内存进行执行。由于产品为了节省成本没有采用QSPI 双flash模式,执行效率会再降低一点。经过测试从bootloader跳转到应用程序,起来需要经过约2.6s左右。具体中断执行效率还需进行进一步测试。 QSPI执行速度对比图

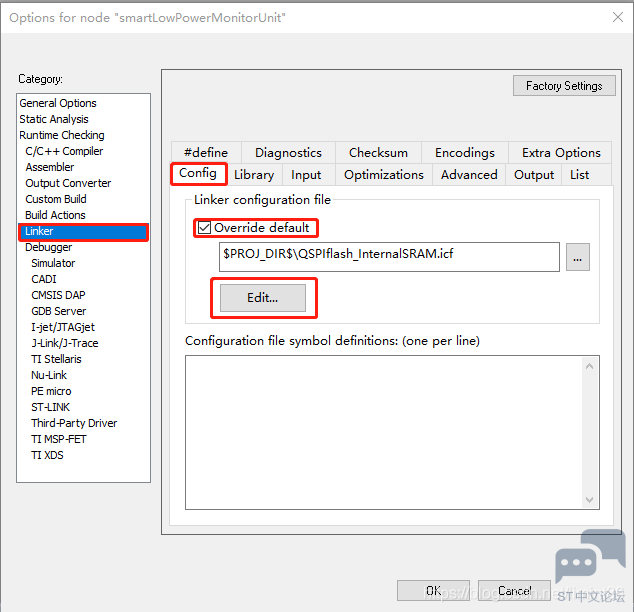

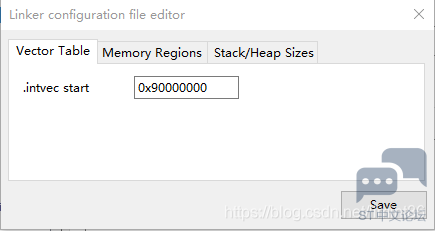

3.启动文件修改 对于bootloader程序,程序再芯片内部128k flash中执行,程序默认启动执行地址为0x8000000,无需修改IAR 的link链接配置文件。 对于应用程序,需将IAR 的link链接配置文件****.icf文件中的__ICFEDIT_intvec_start__ 地址,__ICFEDIT_region_ROM_start__地址,__ICFEDIT_region_ROM_end__地址进行修改,具体可以通过IAR options->Linker->Config,里面进行修改

修改完成后,查看IAR配置后的icf文件,具体内容如下

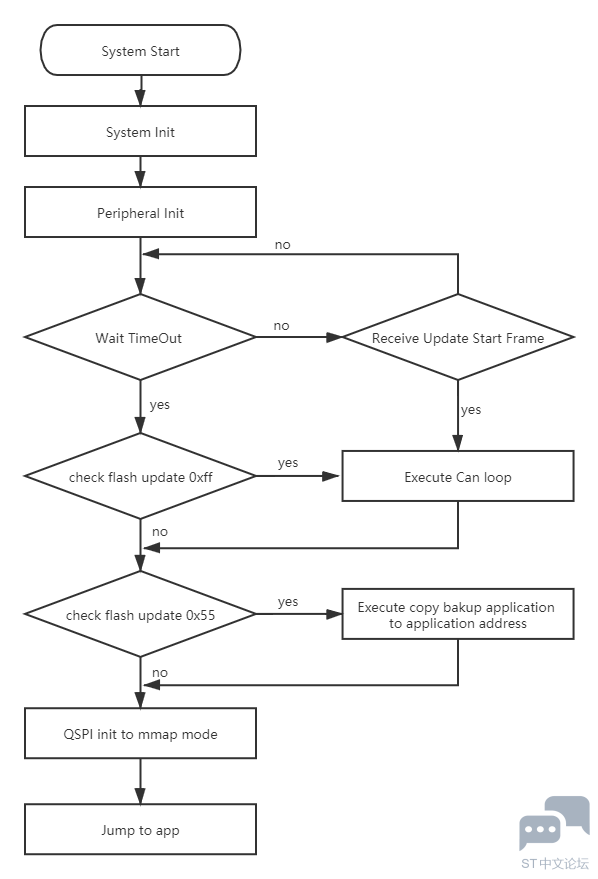

4.bootloader程序与应用程序设计 对于bootloader而言,主要的任务有一下点: 1、接受和处理上位机下发的更新程序,并将其写入到外部flash备份区 2、对更新到外部备份区的程序拷贝到应用区 3、初始化QSPI为内存映射模式,引导程序启动,跳转到应用程序

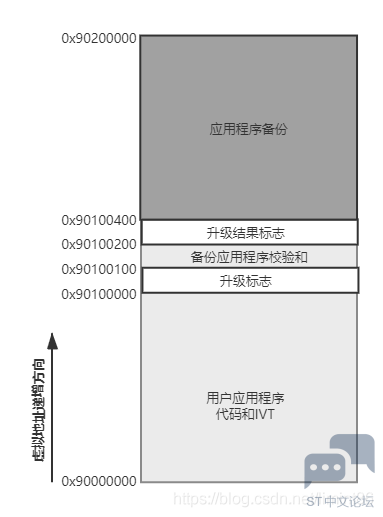

我们将STM32H7整个内部128k flash分配为bootloader程序存储区。装置上电,首先从内部flash 地址0x8000000进行启动,具体执行流程如下图所示:

|

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版