.png) STMCU小助手

发布时间:2021-12-31 18:00

STMCU小助手

发布时间:2021-12-31 18:00

|

一、CAN FD协议介绍 1、CAN-FD特性 (1)兼容经典CAN,可以遵循ISO 11898-1做数据收发。 (2)提升错误检测,支持高达CRC 21位的校验和。 (3)消息优先级。 (4)保证延迟时间。 (5)配置灵活性。 (6)具有时间同步的组播接收。 (7)系统范围内的数据一致性,每条消息最多64个字节。 (8)多主机。 (9)错误检测和信号。 (10)区分节点的临时错误和永久性故障以及自动关闭缺陷节点。 2、CAN-FD格式:

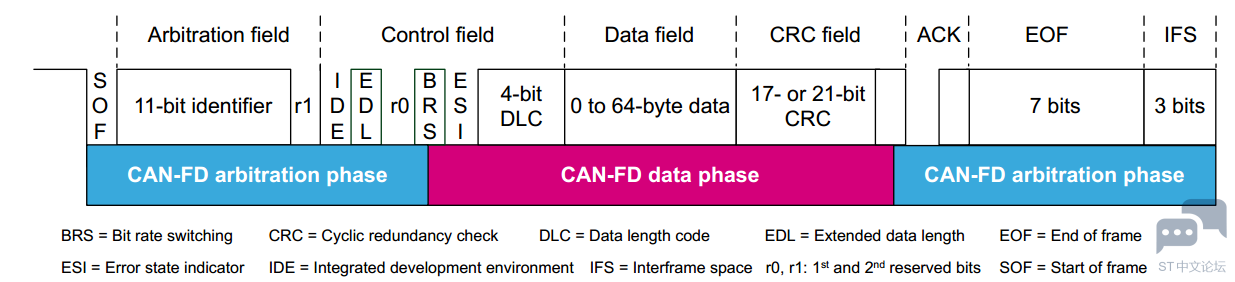

第一个仲裁阶段(The first arbitration phase)是一条消息,其中包含: (1)帧开始(SOF)。 (2)ID号和其他位,指示消息的目的(提供或请求数据),以及速度和格式配置(CAN或CAN-FD)。 数据传输阶段(The data transmission phase)包括: (1)数据长度代码(DLC),指示消息包含多少数据字节。 (2)用户希望发送的数据。 (3)检查循环冗余序列(CRC)。 (4)显性位。 第二个仲裁阶段(The second arbitration phase)包含: (1)总线上其他节点发送的确认(ACK)的接收器(如果至少有一个接收器成功收到消息) (2)帧尾(EOF),在IFS期间不传输任何消息:目标是将当前帧与下一帧分开。 注意:对于29bit标识符帧,当添加18bit标识到第1个仲裁阶段的IDE bit之后与标准CAN FD是类似的。 二、CAN-FD相比CAN2.0的提升 CAN-FD的开发可以满足需要更高带宽的通信网络需求。每帧最多具有64个字节的CAN-FD以及将比特率提高到最大的可能性,使数据阶段要快8倍,在第二个仲裁阶段要恢复到正常的比特率。通过以下方式确保数据传输的完整性: (1)17级多项式对最大16字节的有效载荷进行CRC。 (2)21级多项式对16到64字节之间的有效载荷进行校验。 标准帧和CAN FD的区别:

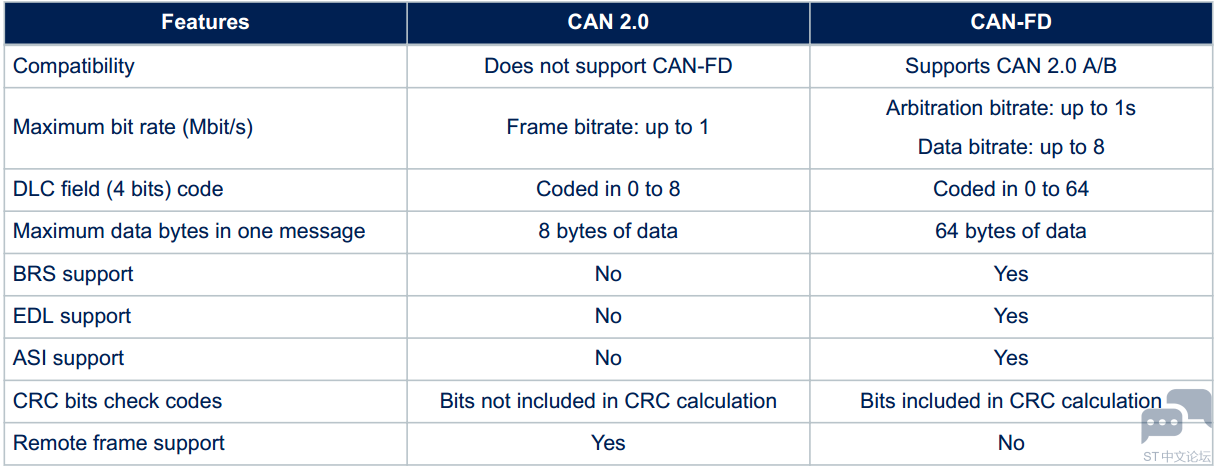

标识符后,CAN 2.0和CAN-FD具有不同的作用: (1)CAN 2.0发送RTR位以精确确定帧类型:数据帧(RTR为主要)或远程帧(RTR)是隐性的)。 (2)由于CAN-FD仅支持数据帧,因此始终发送占优势的RRS(保留)。 IDE位保持在相同位置,并以相同的动作来区分基本格式(11位标识符)。请注意,在扩展格式的情况下,IDE位以显性或隐性方式传输(29位标识符)。 与CAN 2.0相比,在CAN-FD帧中,在控制字段中添加了三个新位: (1)扩展数据长度(EDL)位:隐性表示帧为CAN-FD,否则该位为显性(称为R0)在CAN 2.0帧中。 (2)比特率切换(BRS):指示是否启用两个比特率(例如,当数据阶段位以不同的比特率传输到仲裁阶段)。 (3)错误状态指示器(ESI):指示节点处于错误活动模式还是错误被动模式。 控制字段的最后一部分是数据长度代码(DLC),它具有相同的位置和相同的长度(4位),用于CAN 2.0和CAN-FD。 DLC功能在CAN-FD和CAN 2.0中相同,但CAN-FD有很小变化(下表中的详细信息)。 CAN-FD扩展帧允许单个消息中发送64个数据字节,而CAN 2.0有效负载数据最多可以发送8个字节。

通过增加有效载荷数据的数据字段来改善网络带宽,因为需要更少的包处理。 同时,通过为CRC添加更多位来增强消息完整性: (1)如果有效载荷数据最多为16个字节,则CRC以17位编码。 (2)如果有效载荷数据大于20(16)个字节,则CRC以21位编码。 另外,为了确保CAN-FD帧的鲁棒性,填充位机制支持CRC字段。下表总结了CAN-FD和CAN 2.0之间的主要区别。 提供的主要功能与CAN 2.0相比,CAN‑FD的改进之处在于数据有效负载的增加和速度的提高由CAN-FD中可用的BRS,EDL和ESI位来确保。

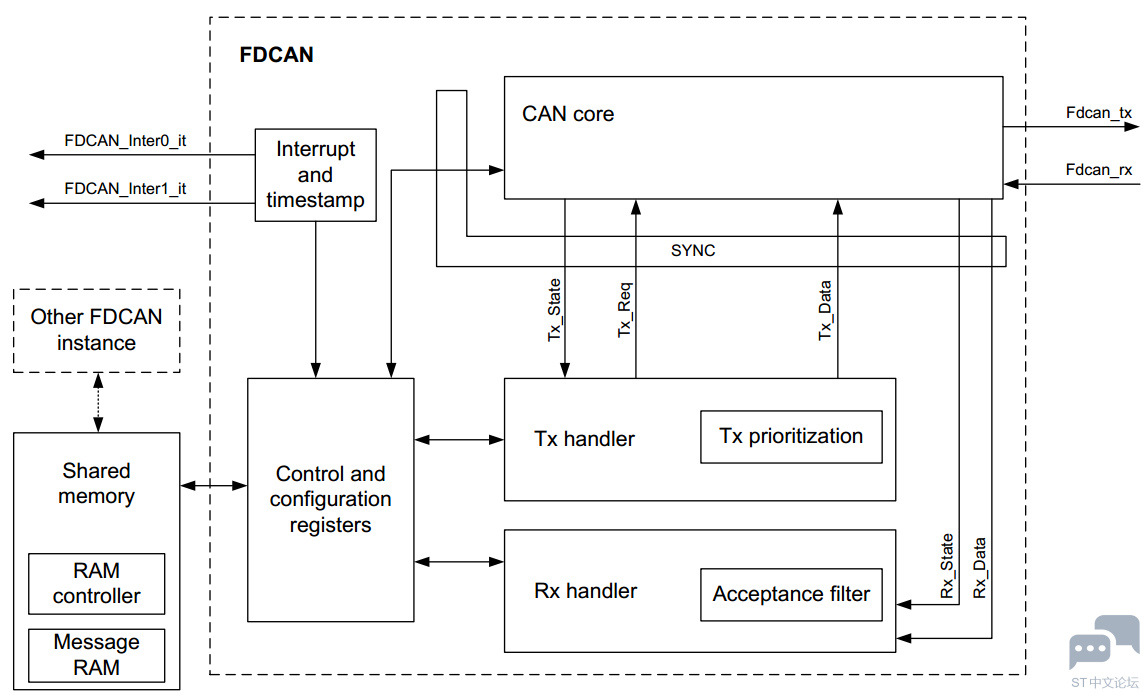

三、CAN FD协议介绍 STM32H7的CAN FD符合ISO 11898-12015标准。 STM32器件上的FDCAN的功能如下所示: (1)符合CAN协议2.0版A,B和ISO 11898-1:2015,-4。 (2)可访问的10 KB RAM内存,最多可分配2560个字。 (3)改进了接收过滤。 (4)两个可配置的接收FIFO。 (5)多达64个专用接收缓冲区。 (6)接收高优先级消息时的单独信令。 (7)多达32个专用发送缓冲区。 (8)可配置的发送FIFO和发送队列。 (9)可配置的发送事件FIFO。 (10)时钟校准单元。 (11)收发器延迟补偿。 下图说明了FDCAN框图。

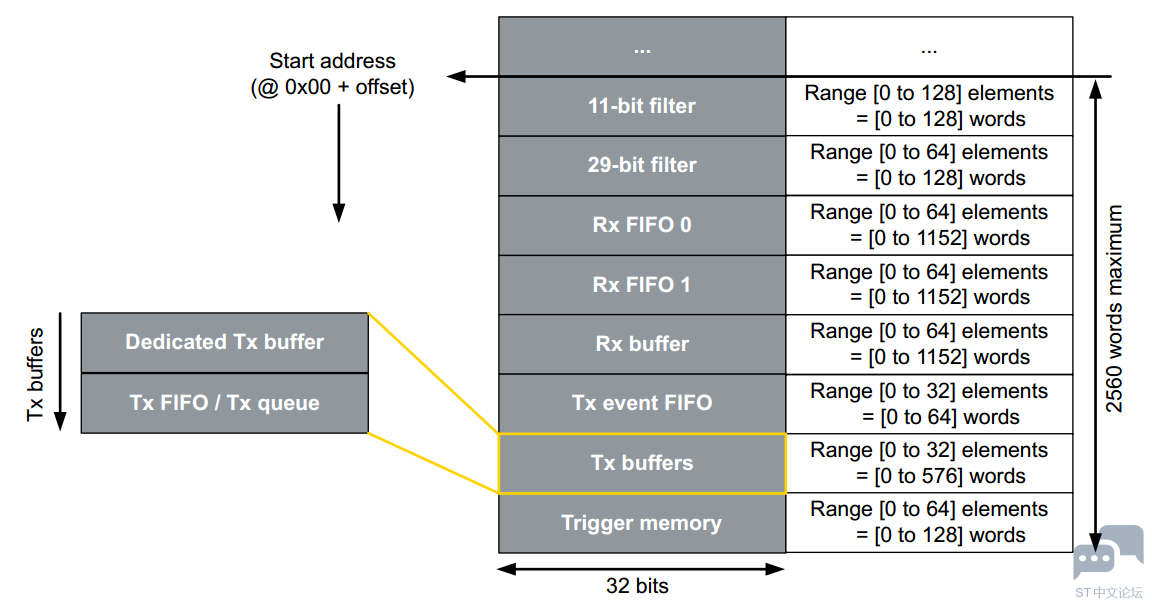

通过这个框图要了解到以下信息: (1)CANFD1和CANFD2共用一个RAM空间 (2)每个CANFD都有自己的内核 (3)CAN内核实现协议控制和收发移位寄存器 (4)Tx handler控制消息从CAN消息RAM到CAN内核 (5)Rx handler控制CAN内核到CAN消息RAM 四、RAM管理 必须配置每条消息的字节数,以确定每条消息所需的内存大小。 CAN-FD上有效负载的增加可以更有效的将内存都利用起来,并允许更多消息要存储在分配的存储空间中。 总的专用RAM大小是2560个32bit数据。 (1)过滤区(11bit过滤和29bit过滤) (2)接收区(Rx FIFO 0,Rx FIFO 1和Rx Buffer) (3)发送区(Tx event FIFO,Tx Buffers) (4)触发空间(Trigger memory)

FDCAN外设的所有部分都可以由用户配置。 所有部分的所有元素之和必须不能超过CAN消息RAM的总大小。 该RAM通过以下方式提高了灵活性和性能:从而有可能消除未使用的部分,并为其他部分扩展足够的内存。在CAN消息中以动态且连续的方式分配每个部分(按照上图顺序); 但是为了避免超出RAM的风险并且出于可靠性的原因,没有将特定的开始和结束地址分配给每个部分。 FDCAN外设可以配置三种传输机制:Tx buffer ,Tx queue 和 Tx FIFO并可以通过Rx buffer 和 Rx FIFO 接收。 它们配置有起始地址偏移量和要存储的存储元素。 起始地址是在配置中预定义的(0到2560),用户必须确保每个内存空间中的元素数量不会导致它们重叠。 注:消息的接收和发送意味着在RAM级别存储“元素”。 这个“元素”仅包含标识符,DLC,控制位(ESI,XTD,RTR,BRS,FDF),数据字段和特定的发送/接收位字段进行控制。 CAN消息的其余位会自动由硬件处理而不保存在RAM中 。 用于控制接收的特定位字段是滤波器索引,可接受的不匹配帧和Rx时间戳。用于传输的特定位字段是消息标记(message marker)和event FIFO控制位。无论Tx buffer, Tx FIFO, Tx queue 或 Rx buffer 中的每个元素分配的32bit的数量是多少,要计算保留: (1)标头信息(两个保留的32bit),用于分配标识符,DLC字段,控制位和特定的发送/接收位字段。 (2)数据(足够的32bit数据个数)以包含每个数据字段的字节数。 下面的公式确定为每个元素分配的32bit的数量: 元素大小(以字为单位)=标头信息(2个字)+数据(数据字段/ 4) 其中数据字段是每条消息的数据字节数 如果数据字段的范围是0到8,则每个元素为数据分配2个字。下表详细介绍了必要的“元素”大小,具体取决于数据字段范围

有效使用CAN消息RAM的示例。 这个例子假设配置了FDCAN外设的应用程序: (1)发送带有专用Tx buffer的32条消息(每个消息在数据字段中包含8个字节)。 (2)具有128个11位过滤器,用于接收消息。 (3)接收64条消息,其中每个消息在专用Rx buffers的数据字段中包含64个字节。 (4)接收64条消息,其中每个消息在Rx FIFO 0的数据字段中包含64个字节。

在此示例中,RAM中的分配按以下顺序进行: (1)在ID-11位部分分配128个字。 (2)保留1152个字用于接收Rx FIFO 0部分中的元素。 (3)保留1152个字,用于接收Rx缓冲区中的元素。 (4)为发送缓冲区中发送的元素保留128个字。 由于采用了动态分配,并且不对未使用的段进行任何分配,因此整个内存大小有效利用了RAM:在此应用程序中分配了所有2560个字。 注意:配置后,分配的地址范围初始化为零 大多数STM32设备支持一个以上的FDCAN外设来满足所有应用程序要求。在这种情况下,重要的是要说RAM是在不同外设之间共享的。 用户可以划分各种外设上的RAM(每个外设的大小通过指示其起始偏移地址来选择)。下图显示了使用多个FDCAN实例的CAN消息RAM的示例。 这该示例假定用户将CAN消息RAM分为两个外设:第一个外设的大小为第二个外设的两倍。

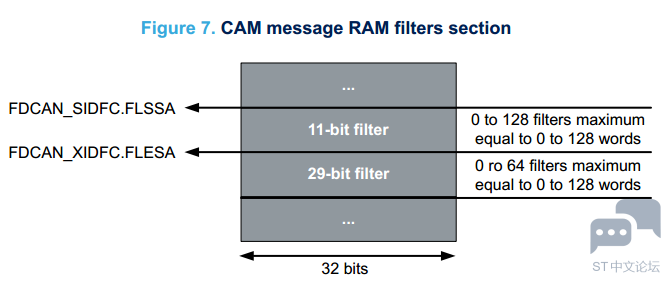

五、RAM过滤区 FDCAN外设可以配置两套验收滤波器:一套用于标准标识符,一种是扩展标识符,用于存储或拒绝接收到的消息。128个过滤元素可以配置用来配置128个11bit标准ID和64个过滤元素可以用来配置64个29bit扩展ID。11位过滤器部分的起始地址通过FDCAN_SIDFC寄存器中的FLSSA [13:0]位进行配置,并且通过FDCAN_XIDFC寄存器中的FLESA [13:0]配置29位滤波器部分。下图显示了CAN消息RAM的一部分,其中包含过滤器元件的数量及其开始位置地址。

可以将这些过滤器分配给Rx FIFO 0/1或专用的Rx buffers。 FDCAN执行接受过滤,它总是从过滤器元素#0开始,然后遍历过滤器列表以找到匹配项元素。验收过滤在第一个匹配元素处停止,而随后的过滤元素不在针对此消息进行了检索。因此,配置过滤器元素的顺序对过滤性能有很重要的影响。用户选择启用或禁用每个过滤器元素,并可以配置每个元素以接受或拒绝过滤。每个过滤器元素可以配置为: (1)范围过滤器(Range filter):该过滤器匹配标识符在两个ID定义的范围内的所有消息。 (2)专用ID的过滤器(Filter for dedicated IDs):可以将过滤器配置为匹配一个或两个特定的标识符。 (3)经典位屏蔽过滤器(Classic bit mask filter):通过对接收到的标识符的位进行屏蔽来匹配标识符组。第一个ID配置为消息ID过滤器,第二个ID为过滤器屏蔽。过滤器屏蔽的每个零位屏蔽已配置的ID过滤器的相应位位置。 注:如果所有位均等于1,则仅当接收到的消息ID和消息ID过滤器相同时,才会发生匹配。 如果所有掩码位均等于0,所有消息ID均匹配。 高优先级消息 当收到高优先级消息时,FDCAN可以通知用户。 此通知可用于监视传入的高优先级消息的状态并启用对这些元素的快速访问。FDCAN在消息过滤器的帮助下检测到高优先级消息。 过滤器元素提供以下内容与高优先级邮件相关的设置: (1)设置优先级并在过滤器匹配的情况下存储在FIFO 0/1中:如果此消息过滤器匹配,则FDCAN通知高优先级消息到达的信息,并将元素存储在Rx FIFO 0/1中。 (2)如果过滤器匹配,则设置优先级:如果此消息过滤器匹配,则FDCAN会通知有关高优先级的信息消息到达,但不存储元素。 接收过滤流程图:

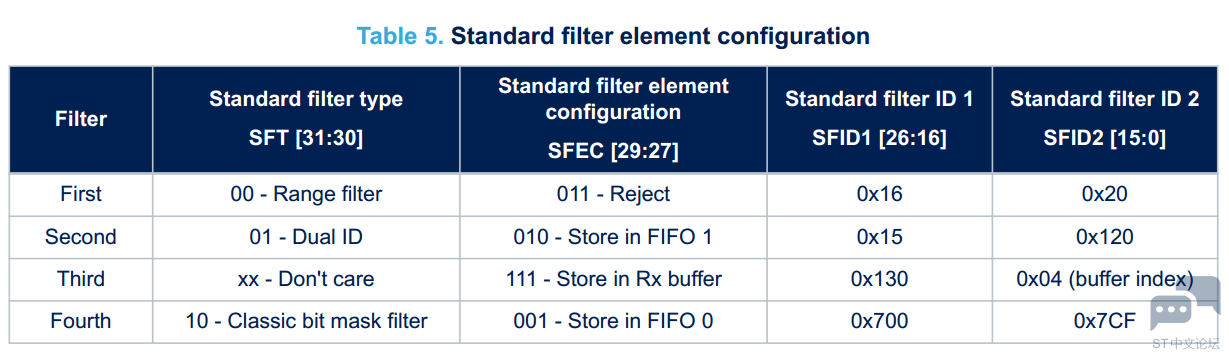

举例说明: 为了说明可以使用的不同类型的过滤器以及每种类型的结果,我们假设用户想要配置FDCAN: (1)拒绝所有标识符在[0x16到0x20]范围内的消息 (2)接受所有标识符等于0x15或0x120的消息,并将它们存储在FIFO 1中 (3)接受标识符等于0x130的消息并将其存储在Rx缓冲区索引4中 (4)接受具有与以下内容相对应的标识符的消息: –bit[10..6] = 0b111 00 –bit[5..4] = 不管,任意值 –bit[3..0] = 0b00000 在这种情况下,必须将过滤器配置为经典位屏蔽过滤器,因为可接受的标识符对应于0b11100XX0000(其中x可以是0或1中的任何值)。 可接受的标识符是: – 0b111 0000 0000(0x700) – 0b111 0001 0000(0x710) – 0b111 0010 0000(0x720) – 0b111 0011 0000(0x730) 基本过滤器ID可以是0x700、0x710、0x720、0x730中的任何值。 屏蔽过滤器ID等于0b111 1100 1111(0x7CF)。下表介绍了标准11位消息ID过滤器的不同配置,如上面的例子。 每个标准过滤器元素包含: (1)SFT位(标准过滤器类型) (2)SFEC位(标准过滤器元素配置)。 (3)SFID1位(标准过滤器ID1) (4)SFID2位(标准过滤器ID2)

第一个过滤器配置为拒绝ID为[0x16 ... 0x20]范围内的消息。 第二个过滤器配置为将ID等于双ID 0x15或0x120的消息存储在Rx FIFO 1中。 第三过滤器被配置为将ID等于0x130的消息存储在Rx缓冲区索引4中。 注意:如果将SFEC配置为“存储到"Rx buffer”,则将忽略SFT的配置。 验收过滤器停在第一次匹配。 因此,筛选器的顺序很重要。本示例以与用户配置扩展过滤器相同的方式配置标准过滤器(请参阅产品数据表以了解更多详细信息)。FDCAN的众多过滤器可能性允许在硬件中进行复杂的消息过滤,这使得软件过滤冗余并节省CPU资源。 六、接收区 Rx FIFO 0和Rx FIFO 1 可以在CAN消息RAM中配置两个Rx FIFO。 每个Rx FIFO部分最多可存储64个元素。每个元素存储在一个Rx FIFO元素中。可以通过FDCAN_RXESC寄存器分别为每个Rx FIFO配置Rx FIFO元素的大小。 Rx FIFO元素大小定义了可以存储一个接收元素的数据字段字节数。 一个大小Rx FIFO元素由前面RAM管理中指定的公式定义。 标头信息包含标识符,DLC字段,控制位和位字段(过滤器索引,可接受的不匹配帧,Rx时间戳)。通过FDCAN_RXESC寄存器中的F1DS [2:0]字段配置元素大小后,Rx FIFO 1的元素个数和起始地址必须分别通过FDCAN_RXF1C寄存器中的F1S [6:0]和F1SA [13:0]进行配置。下图显示了CAN消息RAM上的Rx FIFO部分,其中包含可以支持和每个部分的开始地址。

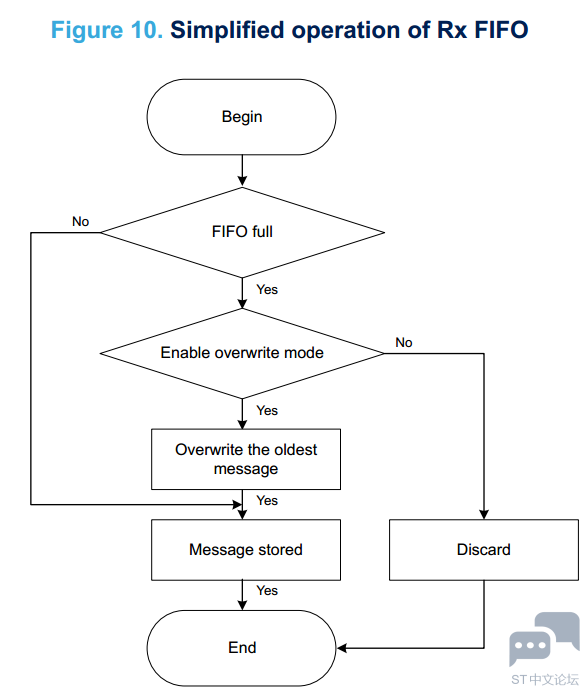

Rx FIFO的起始地址是第一个Rx FIFO元素的第一个字的地址。收到的元素通过匹配过滤的数据将根据匹配的过滤器元素存储在适当的Rx FIFO中。如果Rx FIFO已满,则可以根据两种不同模式来处理新到达的元素: (1)阻塞模式:这是Rx FIFO的默认操作模式,没有其他元素写入RxFIFO,直到至少一个元素已被读出。 (2)覆盖模式:Rx FIFO中接受的新元素将覆盖Rx FIFO中最旧(最先接收的数据)的元素并且FIFO的put和get索引加1。 要从Rx FIFO读取元素,CPU必须执行以下步骤: (1)读取寄存器FDCAN_RXF1S以了解Rx FIFO的状态。 (2)按照以下公式计算RAM中最旧的元素的地址: Oldest element address = CAN_message_RAM_base_address + FDCAN_RXF1C.F1SA (start address) + FDCAN_RXF1S.F1GI (get Index) x Rx FIFO_element_size. (3)从计算出的地址中读取元素。 CPU从Rx FIFO读取一个元素或一系列元素后,它必须确认读取。确认后,FDCAN可以将相应的Rx FIFO缓冲区重新用于新元素。为了确认一个或多个元素,则CPU必须将从Rx FIFO读取的最后一个元素的缓冲区索引写入FDCAN_RXF1A寄存器。结果,FDCAN更新了FIFO填充级别和get索引。 RX FIFO流程:

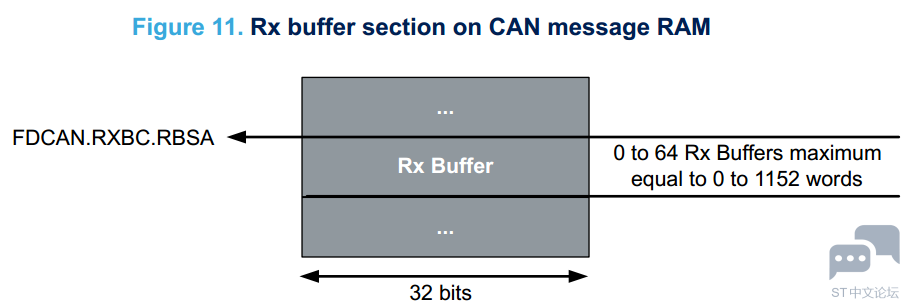

Rx FIFO 0和Rx FIFO 1具有相同的寄存器,它们的名称有意义,方法是更改每次的FIFO数量。 专用的Rx buffer FDCAN支持多达64个专用Rx buffers。 每个专用的Rx buffers可以存储一个元素。专用Rx buffers的大小可以通过FDCAN_RXESC寄存器进行配置。 Rx buffers大小定义可以存储多少个接收元素的数据字段字节。 专用Rx buffers的大小由前面RAM组织中描述的公式定义。 通过FDCAN_RXESC寄存器中的RBDS [2:0]字段配置元素大小后,启动必须通过FDCAN_RXBC寄存器中的RBSA [13:0]字段配置地址。下图显示了CAN消息RAM上的Rx buffers部分,其中有可以支持的最大数量的Rx buffers元素和起始地址。

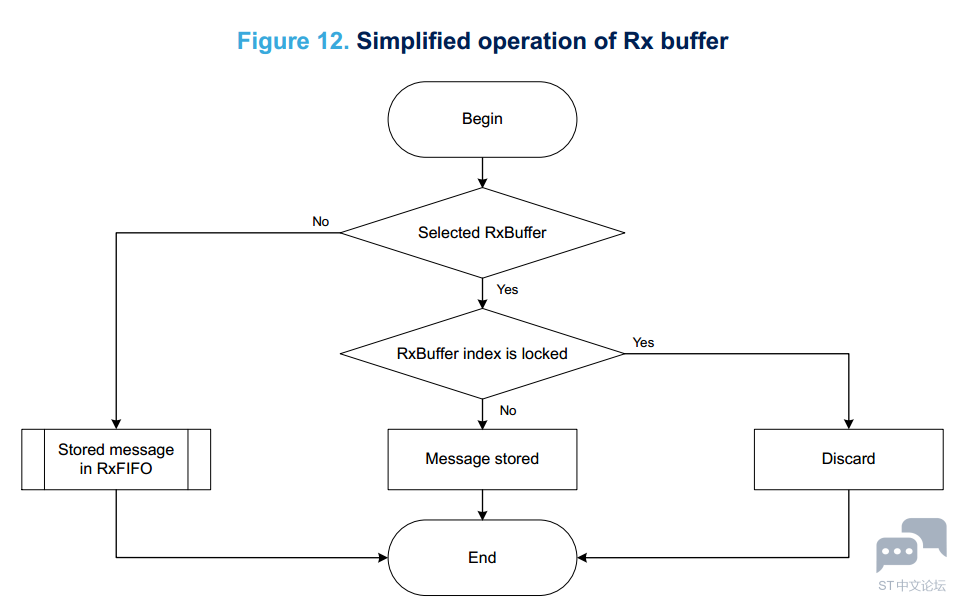

当将元素存储在专用Rx缓冲区中时,FDCAN通过FDCAN_IR寄存器的DRX位设置中断标志以及新数据标志FDCAN_NDAT1或FDCAN_NDAT2寄存器中的相应位。当FDCAN_NDAT1 / 2中的位置1时,相应的Rx缓冲区将被锁定(不会被新元素覆盖),并且相应的过滤器不匹配。 读取元素后,CPU必须将相应的位复位FDCAN_NDAT1 / 2,以解锁相应的Rx缓冲区。 要从专用Rx缓冲区读取元素,CPU必须执行以下步骤: (1)检查FDCAN_NDAT1 / 2中的位,以了解是否有新元素到达专用Rx缓冲区。 (2)计算CAN消息RAM中元素的地址,如以下公式所示: Reference Rx buffer address = CAN_message_RAM_base_address + FDCAN_RXBC.RBSA (startaddress) + dedicated Rx buffer index x Rx_Buffer_element_size. (3)从计算出的地址中读取消息。 过滤器元素可以引用Rx缓冲区索引(0到63)作为接收元素的目的地。如果相应的过滤器匹配,则FDCAN仅执行对引用的Rx缓冲区位置的写操作。 换一种说法,FDCAN不会写入未引用的Rx缓冲区位置。 举例 :Rx缓冲区编号与Rx缓冲区索引的相关配置示例 为了配置过滤器元素以引用Rx缓冲区索引60,必须至少配置61个Rx缓冲区。注意:用户必须选择最佳配置,以避免浪费RAM。下图显示了简化Rx缓冲区操作的流程图

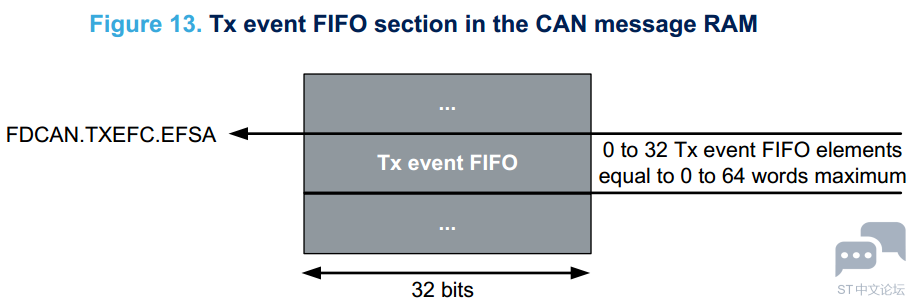

Rx FIFO和专用Rx buffer的不同 如前面所述,FDCAN具有两种机制:专用Rx buffer或Rx FIFO 0/1可以将配置为存储接收到的元素。下表描述了专用Rx缓冲区和Rx FIFO之间的差异。 七、发送区 Tx event FIFO section 通过使用Tx event FIFO,CPU获得有关已发送元素的以下信息: (1)元素传输的顺序. (2)每个元素传输帧的本地时间。 FDCAN提供发送event FIFO。 该Tx event FIFO的使用是可选的。 FDCAN在CAN总线上传输了一个元素成功后,它可以将消息ID和时间戳存储在Tx event FIFO中元素。 Tx event FIFO元素是一种数据结构,用于存储已传输消息。 Tx可以通过FDCAN_TXEFC寄存器配置事件FIFO(Tx事件FIFO配置)。 FIFO可以存储最多32个元素。下图显示了存储Tx事件FIFO元素的CAN消息RAM的示例EFSA [13:0]字段包含起始地址。

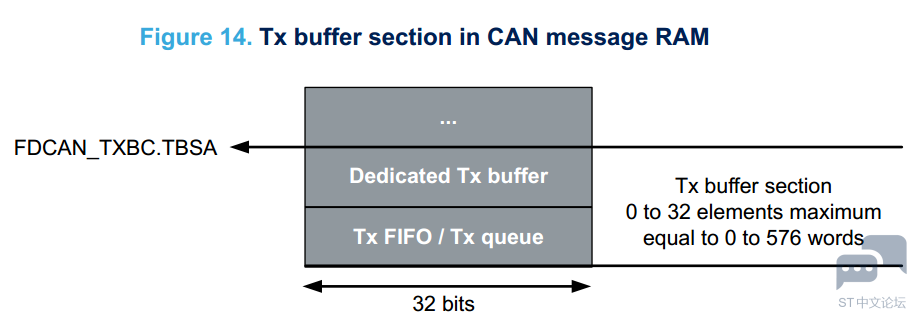

CAN消息RAM中的Tx事件FIFO元素的地址由以下公式确定: Tx event FIFO element address = CAN_message_RAM_base_address + FDCAN_TXEFC.EFSA (startaddress) + FDCAN_TXEFS.EFGI (get index) x Tx_event_FIFO_element_size 为了将 Tx event链接到Tx event FIFO元素,将来自已发送Tx buffer的消息标记复制到Tx event FIFO 元素。 仅当Tx buffer元素中的EFC位(存储Tx事件)等于1时,事件才存储在Tx event FIFO中。当Tx event FIFO已满时,不会再有其他元素写入Tx event FIFO,直到至少有一个元素被写入为止。读出后,Tx event FIFO获取索引增加。如果在Tx event FIFO已满时发生Tx event,则这事件被丢弃。为避免Tx event FIFO溢出,可以使用Tx event FIFO水印。CPU从Tx event FIFO读取一个元素或元素序列后,CPU必须确认阅读。因此,它会通过FDCAN_TXEFA寄存器EFAI [4:0]字段写入从Tx event FIFO读取的最后一个元素的索引。 Tx buffer section 为了使外设传输元素,该元素在定义的存储空间内,并且传输开始。 传输的元素存储在Tx buffer中,用户可以选择使用的机制:专用的Tx buffer或Tx queue或Tx FIFO。FDCAN最多支持32个元素。 每个元素存储标识符,DLC,控制位(ESI,XTD,RTR,BRS,FDF),数据字段,位字段消息标记和事件FIFO控制位,仅一条消息。 在RAM上的分配按以下顺序进行:如果应用程序使用了专用的Tx buffer,则它们在Tx FIFO和Tx queue.之前分配。 用户只能在同一队列中选择Tx queue或Tx FIFO应用程序:FDCAN不支持它们的组合。 如下图所示,Tx buffer的起始地址是通过FDCAN_TXBC寄存器的TBSA [13:0]字段配置

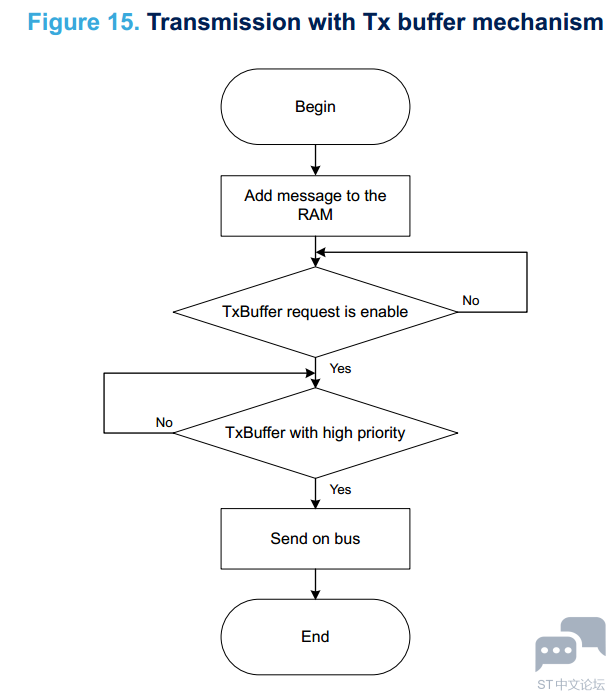

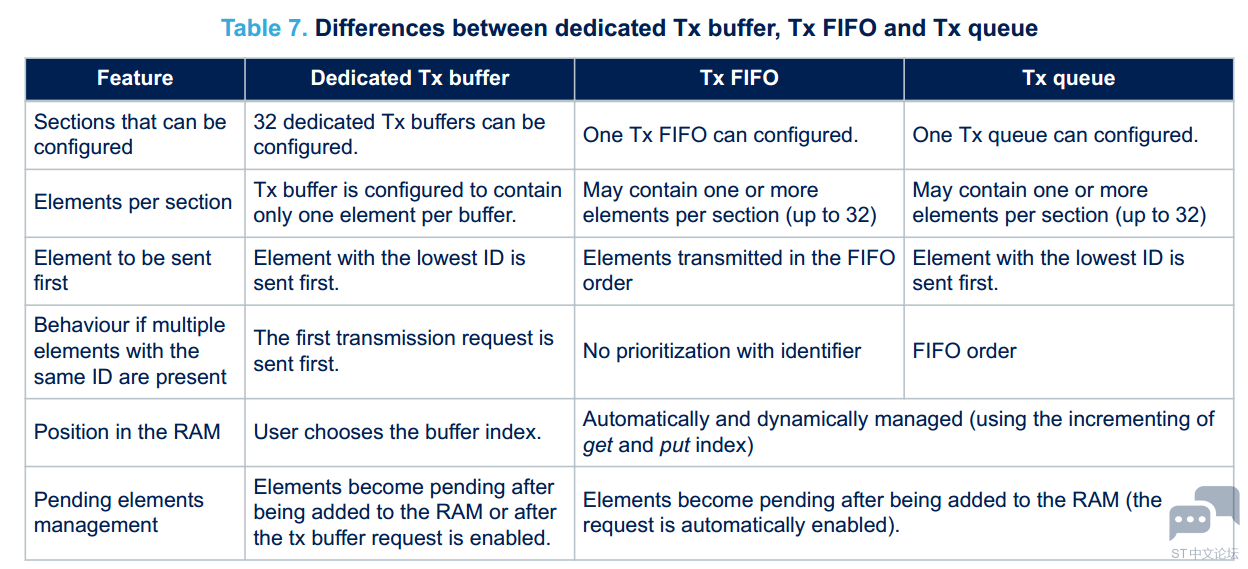

如前一节所述,RAM中的分配是以动态且连续的方式进行的,因此,如果用户未配置Dedicated Tx buffer。 Tx buffer部分仅包含配置的Tx queue 或 Tx FIFO,并将其存储在起始段地址中。 Dedicated Tx buffers 专用Tx buffer的数量是通过FDCAN_TXBC寄存器中的NTDB [5:0]字段配置的。每个专用Tx buffer配置有特定的标识符,以仅存储一个元素。 传输是通过FDCAN_TXBAR寄存器的添加请求。 所请求的消息在外部进行仲裁的CAN总线上,并根据最低标识符(最高优先级)发送出去。专用Tx buffer的内存要求取决于Tx buffer元素的大小。Tx buffer元素大小定义了属于Tx buffer的数据字节数。使用以下公式计算CAN消息RAM中专用Tx缓冲区的地址: Dedicated Tx buffer address = CAN_message_RAM_base_address + FDCAN_TXBC[TBSA] (start address)+ Tx_buffer_index x Tx_buffer_element_size Tx buffer操作机制

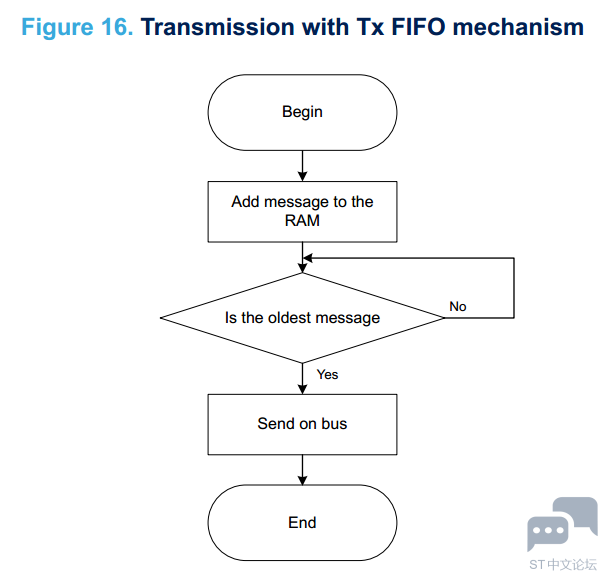

如果多个专用Tx buffer配置了相同的ID,则具有第一个传输请求的Tx buffer首先发送。 Tx FIFO 通过将0写入FDCAN_TXBC中的TFQM位来配置Tx FIFO操作。元素存储在通过get索引中FDCAN_TXFQS的TFG1 [4:0]字段,从get索引引用的元素开始发送Tx FIFO。每次发送后,get索引都会循环递增,直到Tx FIFO缓冲区为空。Tx FIFO可以按照已将元素写入Tx FIFO的顺序传输元素。传输与各个标识符的优先级无关,因为FIFO首先发送出去。 FDCAN通过FDCAN_TXFQS中的TFFL [5:0]字段计算Tx FIFO缓冲区的空闲级别,作为get和put索引之间的差值(get和set索引之间有两种机制递增每个事务以指示下一个事务RAM上要读取或写入元素的缓冲区位置)。该值指示可用(空闲)Tx FIFO的数量元素。 必须从放置索引引用的Tx缓冲区开始,将新的发送元素通过FDCAN_TXFQS中的TFAQPI [4:0]字段指示写入Tx FIFO。CAN消息RAM中的下一个空闲Tx FIFO缓冲区的地址是使用以下公式计算的: Next free Tx FIFO buffer address = CAN_message_RAM_base_address + FDCAN_TXBC.TBSA (startaddress) + FDCAN_TXFQS.TFQPI (put Index) x Tx_FIFO_element_size Tx FIFO机制

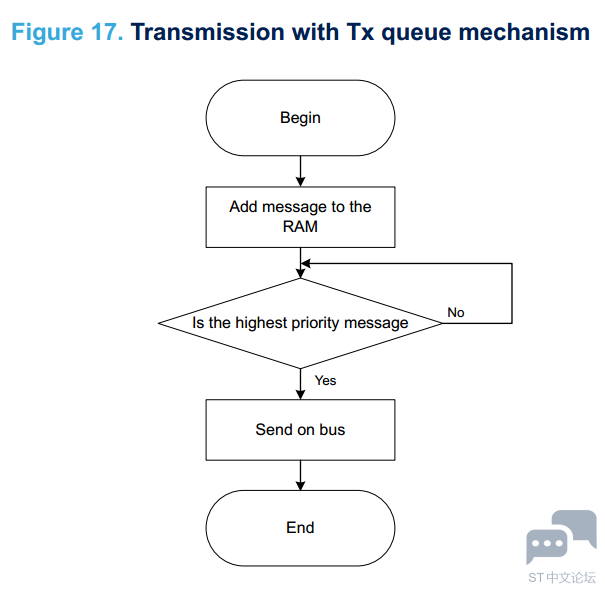

Tx queue 通过将1写入FDCAN_TXBC中的TFQM位来配置Tx队列操作。 Tx中存储的元素从具有最低标识符(最高优先级)的Tx队列缓冲区开始传输队列。与专用Tx缓冲区相比,RAM上的位置是自动动态管理的,因此消息标识符不固定为预定义的Tx缓冲区索引。 新消息必须写入到放置索引引用的Tx队列缓冲区中。周期性添加请求将put索引递增到下一个空闲Tx队列缓冲区。FDCAN_TXFQS中的TFQF位设置为1表示Tx队列已满。在至少一个以下元素之前,不得将其他元素写入Tx队列中。发送请求的元素或取消挂起的传输请求。Tx队列缓冲区的内存要求取决于属于Tx队列的数据字节数元素。CAN消息RAM中下一个可用的空闲Tx队列缓冲区的地址可以通过以下方式计算: Next free Tx queue buffer address = CAN_message_RAM_base_address + FDCAN_TXBC.TBSA (startaddress) + FDCAN_TXFQS.TFQPI (put index) x Tx_Buffer_element_size Tx queue机制

dedicated Tx buffer, Tx FIFO and Tx queue的区别

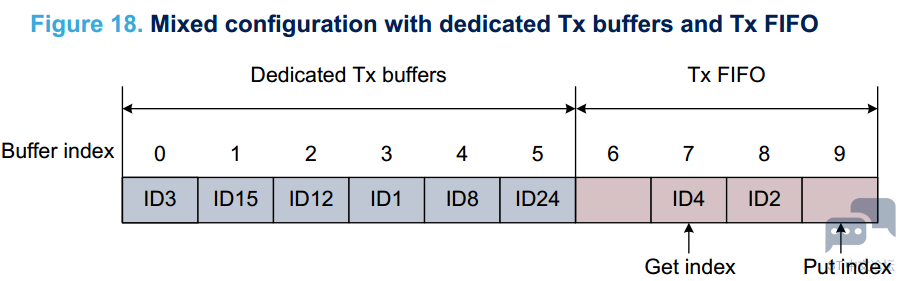

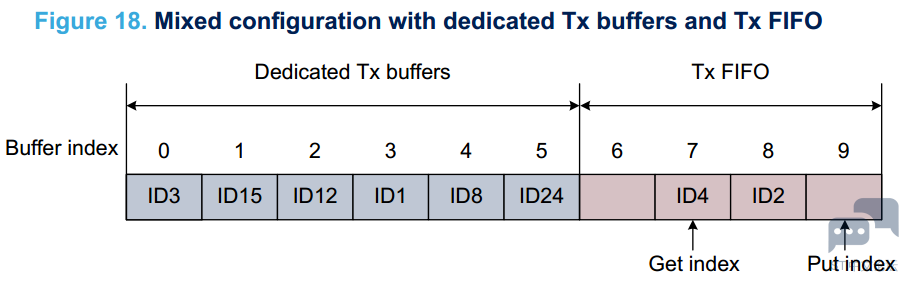

灵活的传输配置 高效的FDCAN支持混合配置,以实现更大的传输灵活性并采取最佳措施,每种机制都有好处。 支持的混合配置是专用的Tx缓冲区+ Tx FIFO以及专用的Tx缓冲区+ Tx队列。 dedicated Tx buffers and Tx FIFO混合配置 可以使用混合配置来配置CAN消息RAM的Tx缓冲区部分,其中CAN消息RAM中的Tx缓冲区部分可细分为一组专用Tx缓冲区和一个Tx FIFO。专用Tx缓冲区的数量是通过FDCAN_TXBC中的NDTB [5:0]配置的。 Tx缓冲区的数量通过FDCAN_TXBC中的TFQS [5:0]配置分配给Tx FIFO的地址。 Tx处理程序使用activated transmission request 和the oldest pending扫描所有专用Tx缓冲区get索引引用的Tx FIFO缓冲区。 具有最低标识符的缓冲区将获得最高优先级,并且是接下来传送。下图说明了使用混合专用Tx缓冲区和Tx FIFO的用例

在此示例中,元素按以下顺序发送(假设所有专用Tx缓冲区请求已启用): 1. Tx buffer 3 (identifier = 1: it is the highest priority between all other dedicated Tx buffers and it has a higher priority than the oldest pending Tx FIFO: Tx buffer 7) 2. Tx buffer 0 (identifier = 3: it is the highest priority between all other dedicated Tx buffers and it has higher priority than the oldest pending Tx FIFO: Tx buffer 7) 3. Tx buffer 7 (because it is the oldest pending Tx FIFO with identifier =4 and has higher priority between all dedicated Tx buffers) 4. Tx buffer 8 (because it is the oldest pending Tx FIFO with identifier =2 and has the highest priority between all dedicated Tx buffers) 5. Tx buffer 4 (identifier = 8: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 6. Tx buffer 2 (identifier = 12: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 7. Tx buffer 1 (identifier = 15: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 8. Tx buffer 5 (because it is the only pending dedicated Tx buffer) dedicated Tx buffers and Tx queue混合配置 可以使用混合配置来配置CAN消息RAM的Tx buffer,其中CAN消息RAM中的“ Tx缓冲区”部分可细分为一组专用Tx buffer和一个Tx queue。通过FDCAN_TXBC中的NDTB [5:0]配置专用Tx buffer的数量和Tx queue的数量缓冲区是通过FDCAN_TXBC中的TFQS [5:0]配置的。Tx处理程序扫描具有激活的传输请求的所有专用Tx缓冲区和Tx队列缓冲区。标识符最低的缓冲区获得最高优先级,然后发送。下图说明了使用混合专用Tx缓冲区和Tx队列的用例。

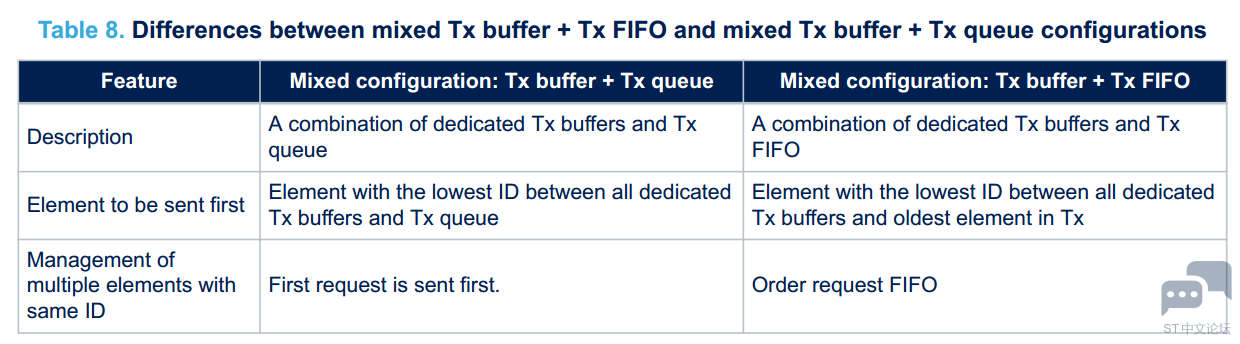

在此示例中,元素按以下顺序发送(假设所有专用Tx缓冲区请求已启用): 1. Tx buffer 3 (identifier = 1: it is the highest priority between all other dedicated Tx buffers and it has a higher priority than the oldest pending Tx FIFO: Tx buffer 7) 2. Tx buffer 0 (identifier = 3: it is the highest priority between all other dedicated Tx buffers and it has higher priority than the oldest pending Tx FIFO: Tx buffer 7) 3. Tx buffer 7 (because it is the oldest pending Tx FIFO with identifier =4 and has higher priority between all dedicated Tx buffers) 4. Tx buffer 8 (because it is the oldest pending Tx FIFO with identifier =2 and has the highest priority between all dedicated Tx buffers) 5. Tx buffer 4 (identifier = 8: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 6. Tx buffer 2 (identifier = 12: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 7. Tx buffer 1 (identifier = 15: it has the highest priority between all other dedicated Tx buffers and the Tx FIFO is empty) 8. Tx buffer 5 (because it is the only pending dedicated Tx buffer) 不支持带有Tx FIFO和Tx队列的混合配置。 dedicated buffer + Tx FIFO 和 Tx buffer + Tx queue的区别如下:

在Tx FIFO + Tx队列中,元素在“添加到RAM”操作之后立即变为挂起状态。 八、测试模式 在FDCAN的操作模式下,除了正常操作外,还有几种测试模式可用。 那里测试模式只能用于生产测试或自测以及校准单元。必须将FDCAN_CCCR中的TEST位设置为1,以允许对FDCAN测试寄存器和存储器的写访问。测试模式和功能的配置。FDCAN以下列模式之一工作: (1)限制操作模式Restricted-operation mode (2)总线监控模式Bus-monitoring mode (3)外部环回模式External loop-back mode (4)内部环回模式Internal loop-back mode (1)限制操作模式Restricted-operation mode 在受限操作模式下,FDCAN能够: --接收数据帧 --接收远程帧 --确认有效帧 该模式不支持: --数据帧发送 --远程帧发送 --活动错误帧或过载帧发送 通过FDCAN_CCCR中的ASM位将FDCAN设置为受限操作模式。当Tx handler 无法从CAN读取消息RAM准时或时钟校准激活时,将自动进入受限操作模式。在这种模式下,应用程序测试不同的比特率,并在应用程序收到有效的帧之后退出受限操作模式。下图说明了在受限操作模式下FDCAN_TX和FDCAN_RX引脚的连接

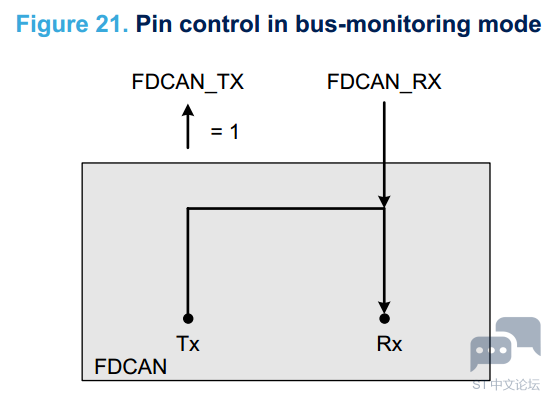

注:只要FDCAN处于受限操作模式,FDCAN_TX引脚就处于隐性状态。 显性位被传输,以此确认接收到有效帧。 (2)总线监控模式Bus-monitoring mode 为了分析总线上的通信量而又不受主要位传输的影响,用户可以设置FDCAN_CCCR中的MON位,可以在总线监视模式下使用FDCAN。在总线监视模式下,FDCAN能够: --接收有效的数据帧 --接收有效的远程帧 该模式不支持: --传输开始 --确认有效帧(与受限操作模式不同) 在总线监视模式下,FDCAN仅在总线上发送隐性位。 下图显示了总线监视模式下FDCAN_TX和FDCAN_RX引脚的连接。

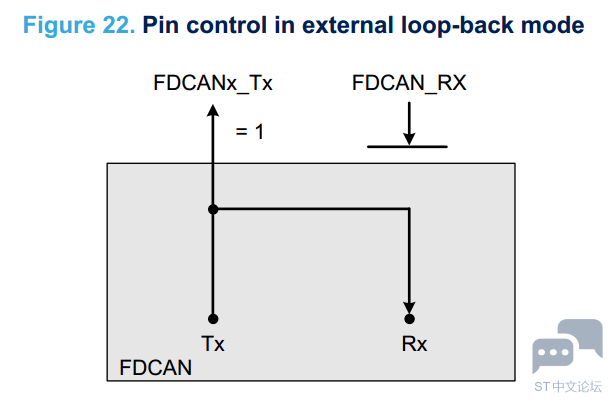

(3)外部环回模式External loop-back mode 提供此模式用于硬件自检。 用户可以通过以下方式将FDCAN设置为外部环回模式:将1写入FDCAN_TEST中的LBCK位,并将0写入FDCAN_CCCR中的MON位。 FDCAN对待自己的发送的消息作为已接收的消息,如果它们通过Rx FIFO中的接受过滤,则将其存储。为了独立于外部信号,FDCAN忽略确认错误(隐性位在确认插槽中采样)。 FDCAN实现内部TX和RX连接。 下图显示了外部环回模式下的FDCAN_TX和FDCAN_RX引脚的连接。

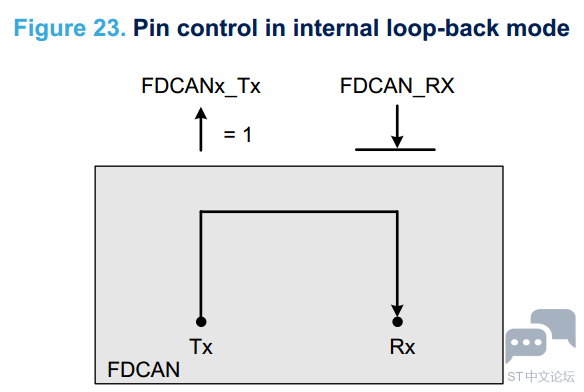

(4)内部环回模式Internal loop-back mode 提供此模式用于硬件自检。 用户可以通过以下方式将FDCAN设置为内部环回模式:向FDCAN_TEST中的LBCK位写入1,并向FDCAN_CCCR中的MON位写入1。可以测试FDCAN,而不会影响连接到FDCAN_TX和FDCAN_RX的正在运行的CAN系统针脚。 FDCAN_RX引脚与FDCAN断开连接,并且FDCAN_TX引脚保持隐性。 下图显示了内部环回模式下FDCAN_TX和FDCAN_RX引脚的连接

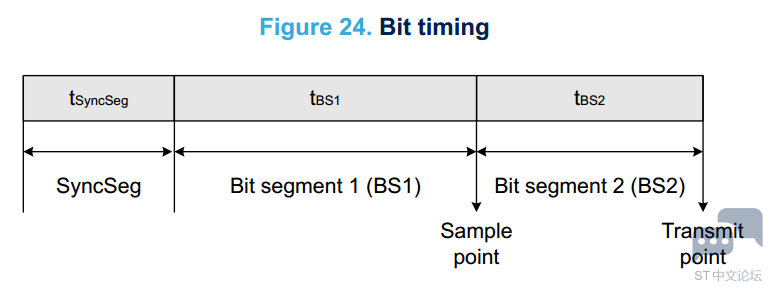

收发器延迟补偿 在采样点,所有发送器都检查先前发送的位是否被正确采样。 这需要一种机制来检查问题并检测其他节点错误帧。 由于发射器看到了自己的发送位由收发器环路延迟而延迟,此延迟为TSEG1设置了下限,如图所示。下图(采样点之前的时间段),这也是数据比特率的上限。 这是引入收发器延迟补偿机制(TDC)的原因。

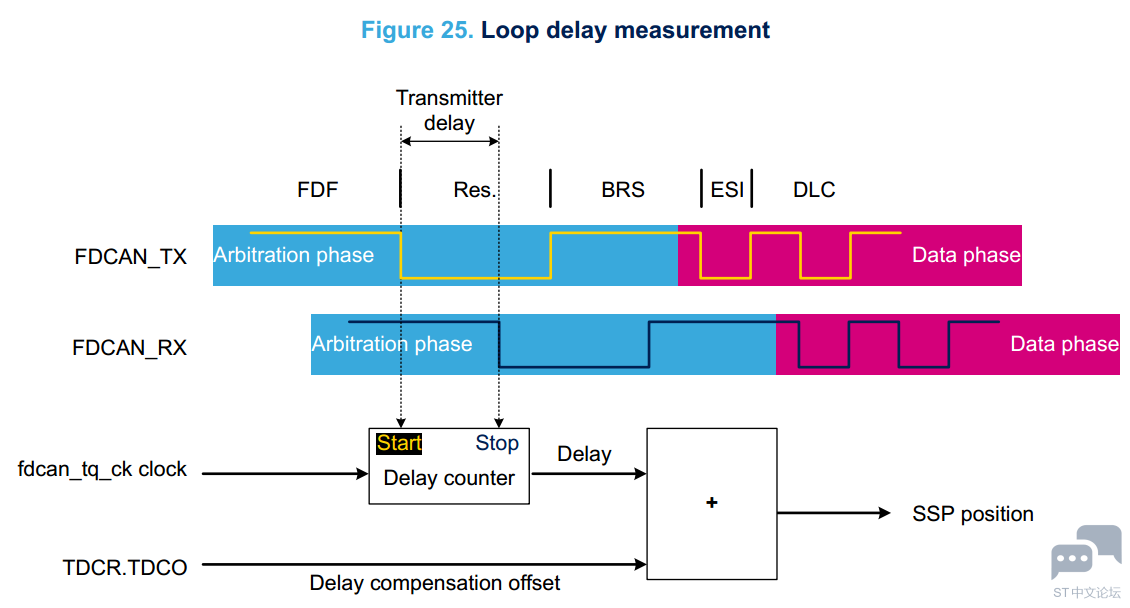

为了在检查误码时补偿此环路延迟,定义了一个辅助采样点(SSP)。而不是在采样点完成,而是在SSP中检查传输的位。 该检查的结果是直到达下一个采样点为止。 为数据阶段中发送的每个位生成一个SSP。 收发器不对称和总线振铃必须考虑SSP位置,但是没有时钟容限,因为收发器会监视自己的位置位流。 通过将1写入FDCAN_DBTP中的TDC位来启用收发器延迟补偿。 测量在数据阶段开始之前(在信号的下降沿之前)在每个发送的FDCAN帧内开始FDF逐位解析。 当在示波器的“接收”输入引脚FDCAN_RX看到该边沿时,测量将停止。 此测量的分辨率为1 mtq(最小时间量) 下图显示了环路延迟的测量

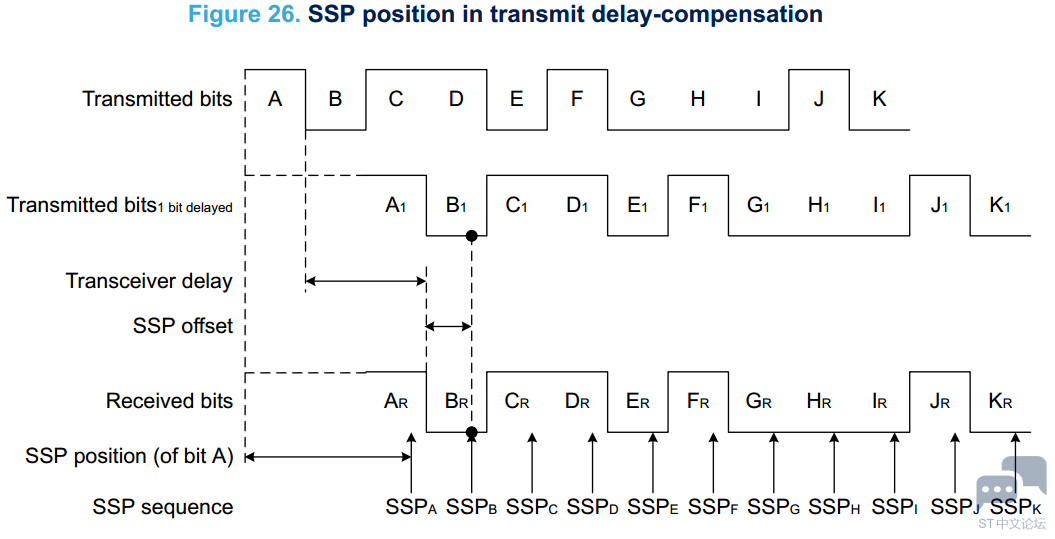

注1:在仲裁阶段,始终禁用延迟补偿。SSP位置定义为从FDCAN_TX引脚到FDCAN_RX引脚测得的延迟之和,加上通过FDCAN_TDCR中的TDCO [6:0]字段配置的发送器延迟补偿偏移。 注2:发送器延迟补偿偏移量用于调整SSP在接收位内部的位置。存储已发送位的值,直到达到其SSP,然后将其与实际接收到的位进行比较,如下图所示,该值表示发送的比特序列A到K和接收的比特序列AR到KR,以及从SSPA到SSPK的一系列SSP。 通过比较SSBR来检查接收到的比特BR与延迟位B1。 SSPB的位置在发送的比特B开始之后的特定时间。特定时间是测得的收发器延迟与配置的SSP偏移之和。

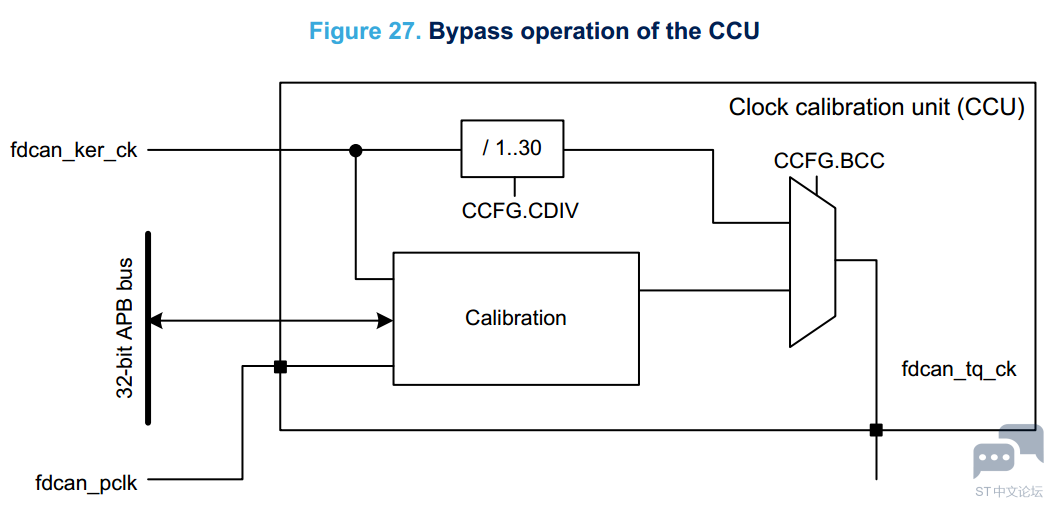

根据博世(Bosch)文档确定,必须考虑以下边界条件FDCAN中实现的发射机延迟补偿: ----从FDCAN_Tx到FDCAN_Rx测得的延迟与已组态的发送器延迟之和在数据阶段,补偿偏移量必须小于六位时间。 ----从FDCAN_Tx到FDCAN_Rx测得的延迟与已组态的发送器延迟之和补偿偏移不得超过127 mtq。 注3:如果总和超过127 mtq,则最大值(127 mtq)用于发射机延迟补偿。数据阶段在CRC分隔符的采样点结束,该采样点停止检查SSP处的接收位。本文档的下一部分将说明时钟校准单元,并对其功能和操作进行说明。 九、FDCAN时钟校准 FDCAN支持时钟校准单元(CCU)功能。 该功能允许用户校准FDCAN,FDCAN发送器(主机)接收器(设备)。 例如,当FDCAN设备与主机的最新比特率。此功能允许用户在总线中添加新实例,并且比特率的存在是未知的。 也是在FDCAN接收器没有精确石英的情况下很有用(可能导致准时错误) CCU介绍: 时钟校准单元是通过FDCAN_CCU_CCFG寄存器初始化的,只有当两个FDCAN_CCCR中的CCE和INIT位设置为1。仅当FDCAN在CAN 2.0模式下运行时,才可以使用CCU。当FDCAN_CCU_CCFG中的BCC = 1时,时钟校准被绕过。 下图显示了旁路操作。

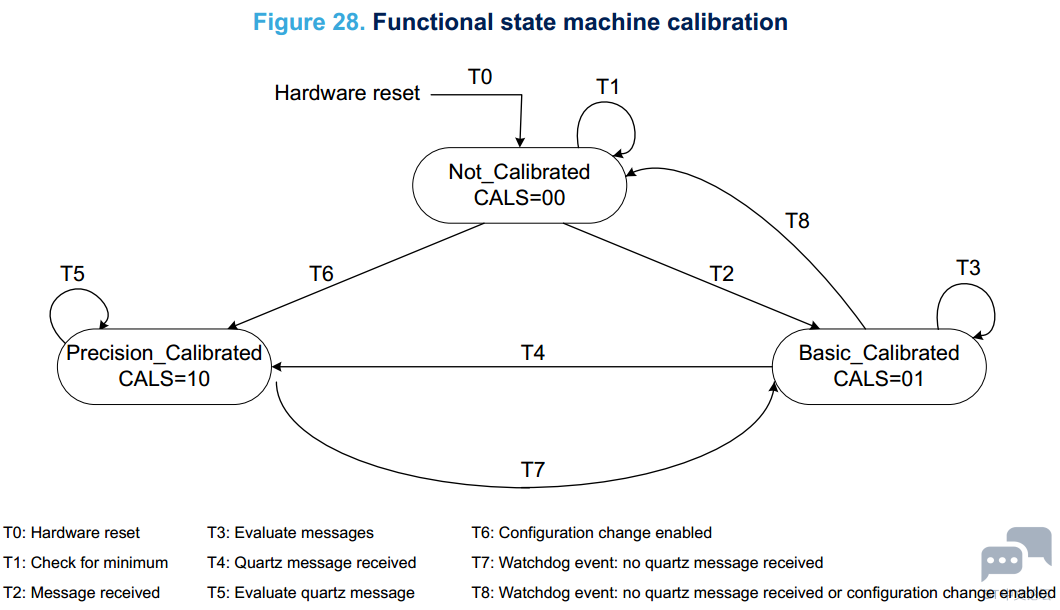

CCU操作条件:仅当FDCAN比特率在125 Kbit / s和1 Mbit / s之间时,CCU才能运行 CCU功能说明:通过适配时钟分频器,可以通过CAN消息对fdcan_tq_ck(时间量子时钟)进行校准,它从fdcan_ker_ck时钟生成CAN协议时间量tq。 校准状态机:功能状态机的校准如下图所示。

基础校准: 测量了从隐性到显性的两个连续下降沿之间的最小距离。 这该措施假设两个CAN位时间以PLL时钟周期计。 每当新的时钟分频器通过FDCAN_CCU_CCFG中的CDIV [3:0]字段找到边缘之间的较小距离来更新一次测量。 当CAN协议控制器检测到有效的CAN消息时,便完成了校准 精确校准: 校准状态机通过计算以下内容来测量CAN帧内较长位序列的长度:fdcan_ker_ck周期数。该位序列的长度可以通过在FDCAN_CCU_CCFG中CFL位配置为32位或64位。精度校准基于新的时钟分频器值,该值由较长位序列的测量。校准框通过FDCAN验收过滤检测。过滤器元素和Rx缓冲区必须为在FDCAN中配置以识别和存储校准消息。如果fdcan_ker_clk校准是通过软件完成的(请从CALS [1:0]字段中评估校准状态FDCAN_CCU_CSTAT),必须将FDCAN设置为受限操作模式,直到校准完成Precision_Calibrated状态(无帧,无错误或过载标志传输,无错误计数)。 注意:收到校准消息后,必须重新设置Rx缓冲区新数据标志以启用发信号通知。校准消息的数据字段必须至少为1010二进制序列,以确保设备节点可以进入Basic_Calibrated状态,并且主机节点消息得到确认。只能在由稳定的石英时钟控制的主机节点发送的有效CAN帧上执行精确校准。精密校准必须在预定义的最大间隔内重复进行,并由校准看门狗监督。 校准看门狗: 校准看门狗是一个递减计数器,它以Not_Calibrated状态开始,并监视接收到的信号消息。当处于Basic_Calibrated状态时,校准监视程序随每个收到的消息重新启动。 注意:如果在校准看门狗递减计数到零之前未收到任何消息,则FSM校准保持不变处于Not_Calibrated状态。 计数器被重新加载,并且基本校准重新开始。进入Precision_Calibrated状态时,将重新启动校准看门狗。 在这种状态下,校准看门狗监视收到的石英消息。 注意:如果FDCAN直到校准看门狗都没有收到来自石英控制节点的消息,当计数降至零时,FSM校准将转换回“ Basic_Calibrated”状态。 校准例子: 本示例介绍了一个用例,用于通过FDCAN主机(发送器)校准FDCAN设备(接收器)。 这以下流程图说明了校准前通过FDCAN设备的步骤

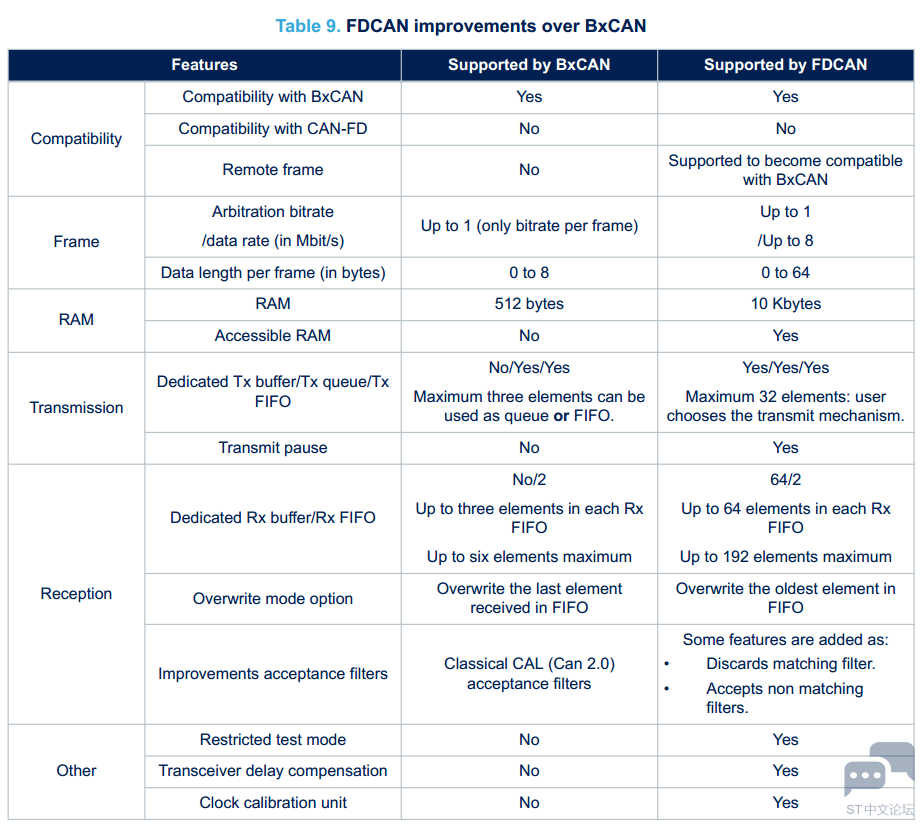

校准成功通过后,FDCAN设备准备好进行接收和发送带有新FDCAN主机比特率的消息。 十、FDCAN相比标准bxCAN的提升 下表可帮助用户简化将STM32设备中的CAN 2.0协议升级到CAN-FD协议的过程。该表还指定了FDCAN的改进。与传统的BxCAN(基本扩展CAN)相比,FDCAN具有许多优势,包括更快的数据传输速度。速率和数据字节数的扩展,减少了帧开销。 总线负载也可以减少。 传输和接收中消息数量的增加要求RAM存储器的改进

鉴于BxCAN的兼容性,BxCAN开发人员可以轻松地迁移到FDCAN,因为FDCAN可以无需对整个系统设计进行修订即可实施。 FDCAN包含所有BxCAN功能,并满足新应用程序的要求。 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版