.png) STMCU小助手

发布时间:2022-1-22 10:45

STMCU小助手

发布时间:2022-1-22 10:45

|

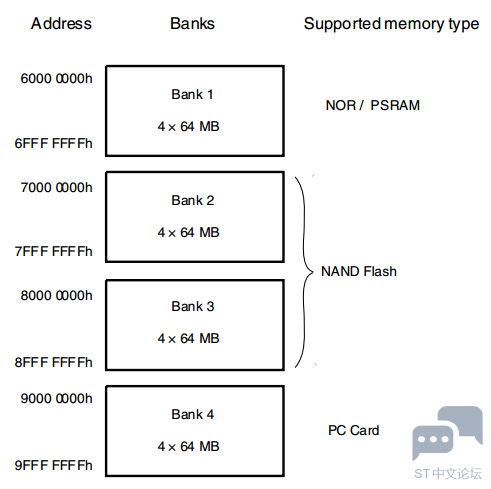

这两天调试STM32F103外扩SRAM,将调试过程中遇到的问题记录下,SRAM的规格是256K*16的异步SRAM,地址总线为18,数据线宽度为16. 在调试过程中遇到一些小问题,希望读者能少走些弯路。 先看一下FSMC内存映射图: 由图可知,stm32的FSMC模块分为四个bank,每个bank的大小事64M。

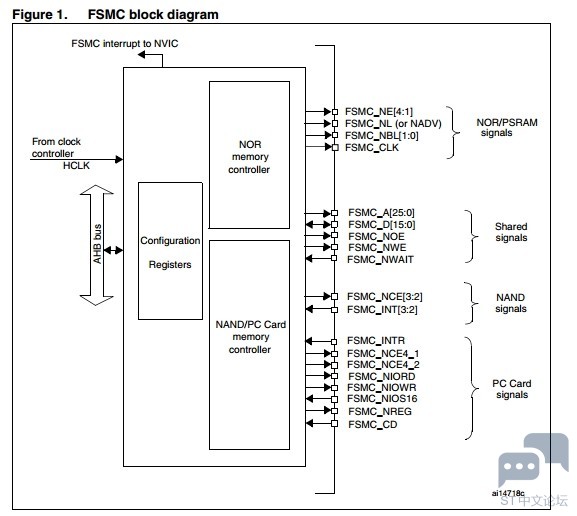

下面这张图是FSMC各个块的信号分配图。

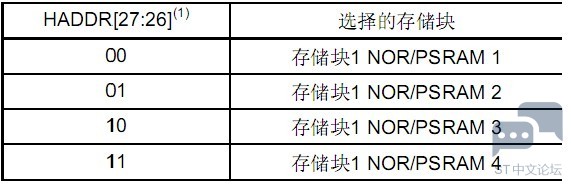

由上图可知,bank1 NOR/PSRAM可以分为4个子块,由FSMC_NE[4:1]来选择使能哪个子块。 例如:每小块NOR/PSRAM的64M地址范围如下: 第一块:6000 0000h--63ff ffffh 第二块:6400 0000h--67ff ffffh 第二块:6800 0000h--6bff ffffh 第三块:6c00 0000h--6fff ffffh 我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下图所示:

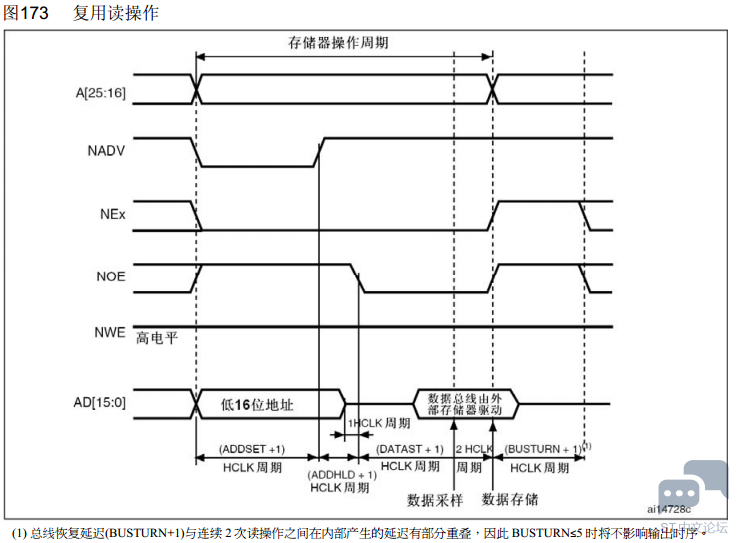

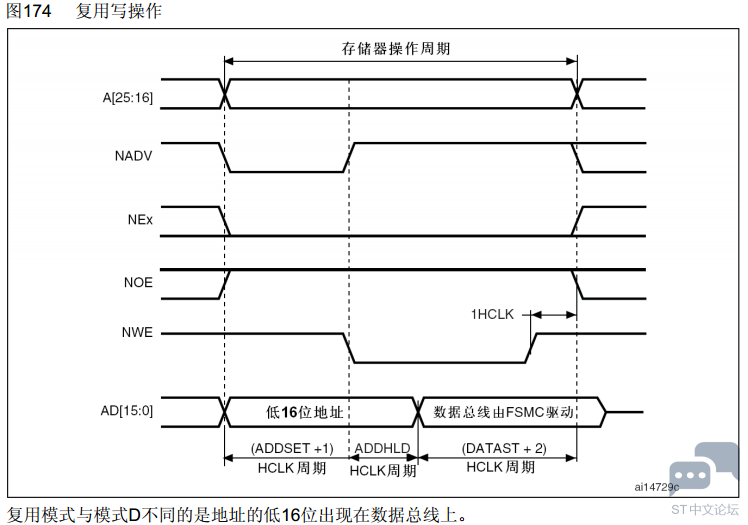

这里我使用的是100脚的stm32,只有NE1引脚可用,也就是说只能用Bank1的存储块1,即FSMC_Bank1_NORSRAM1。 我用的STM32是100脚的,地址和数据总线是复用的,那么需要用到锁存器来区分地址和数据,而锁存信号是NADV输出的,注意看图173和图174的NADV信号在输出地址时是低电平,输出数据时是高电平,所以锁存器要选择一个高电平锁存或者加个反向器。 在配置STM32的FSMC的寄存器时要注意下面两句话:

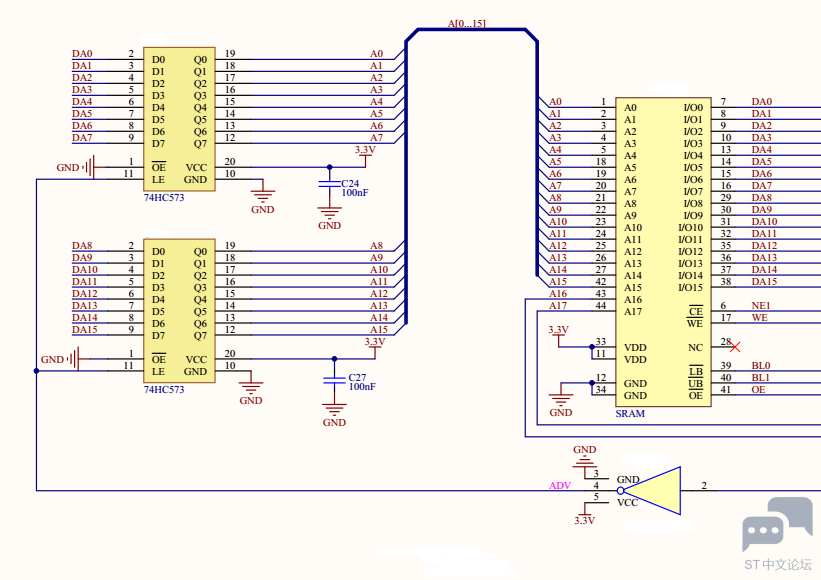

SRAM参考原理图如下图:

stm32的FSMC功能用到的复用IO口比较多,配置时需要细点心:

外部SRAM的访问: 在访问SRAM时纠结了许久,最后终于弄明白了。网上看了很多资料,有说在访问时要先将地址偏移,有说直接访问就行。最后经过测试发现访问片外SRAM时跟访问内部RAM一样,直接访问就可以了,FSMC都帮我们做好了。 当访问字节数据时:*((u8*)(BANK1_SRAM_BASE+offset))。1.读取SRAM数据时,将offset设为0x00,用示波器测试SRAM的A0地址信号是低,当offset为0x01时,用示波器测试SRAM的A0地址信号也是低,当offset为0x02和0x03时SRAM的A0地址信号是高,这说明当字节访问时地址确实是偏移了1位,原因是SRAM是16位器件(SRAM的1个地址存储16位数据),一次可以访问2个字节的数据,这个时候FSMC将根据offset值判断,访问的是高8位还是低8位,即如果offset的最低位是0则访问的是16位数据的低8位,如果offset的最低位是1则访问的是16位数据的高8位。2. 向SRAM写数据时,道理也是一样的,只是写的时候通过BL[1:0]两个管脚控制写高字节还是低字节。 当访问半字数据时:*((u16*)(BANK1_SRAM_BASE+offset))。1.读取SRAM数据时,这个时候要注意了,FSMC在访问的时候要看offset的值是不是半字对齐的。如果offset是0x00,则直接访问的是SRAM的0x00地址处的16位数据,当offset是0x01时,FSMC是分两次访问的,第一次是访问SRAM的0x00地址的高字节,第二次是访问SRAM的0x01地址处的低字节(SRAM的1个地址存储16位数据),通过用示波器测量SRAM的A0地址信号得到,信号是先低在高的一个脉冲,验证了前面的说法。2. 向SRAM写数据时,道理也是一样的,只是写的时候通过BL[1:0]两个管脚控制写高字节还是低字节。 当访问字数据时:访问字时,FSMC分为2个半字访问。 总结:外部SRAM就跟片内SRAM一样用就行了。 |

STM32G0 系列 I2C 通信异常典型案例分析与解决方案总结

经验分享 | LAT1490 两个STM32G0 I2C 通信异常的案例分析

经验分享 | STM32G0 I2C bootloader Go 命令后调试连接失败:DBG_SWEN 位复位修复

经验分享 | STM32G0B1 待机模式意外唤醒深度解析:RTC 结构体未初始化的隐形坑

经验分享 | STM32G0B1 待机模式意外唤醒深度解析:RTC 结构体未初始化的隐形坑

如何在STM32和Arduino上实现卷积神经网络

STM32与51单片机差异一文速览

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

【STM32入门学习路径指南】(四步走)

微信公众号

微信公众号

手机版

手机版