.png) STMCU小助手

发布时间:2022-2-24 19:41

STMCU小助手

发布时间:2022-2-24 19:41

|

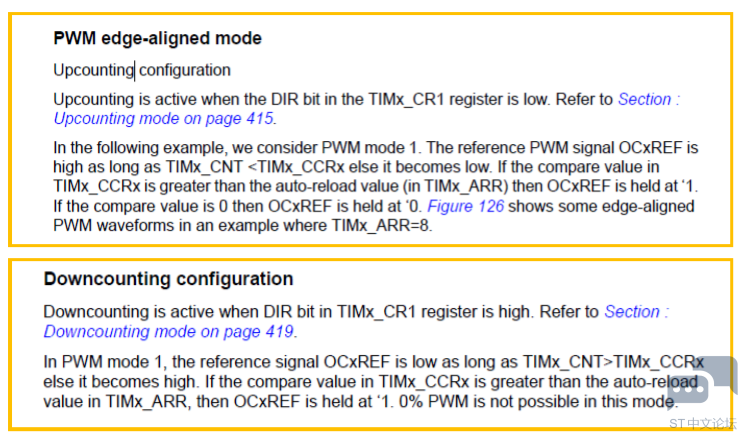

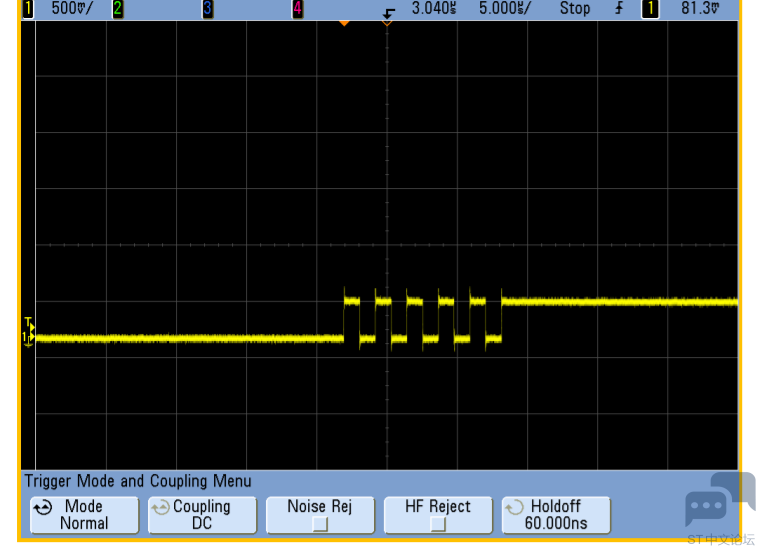

STM32L053 的 PWM 模式下,CounterMode,OC Mode 与OCPolarity 的关系。 一. 前言 研究下 CounterMode,OC Mode 与 OCPolarity 的排列组合的关系 二.排列组合 这里的测试条件有: CounterMode:TIM_COUNTERMODE_UP,TIM_COUNTERMODE_DOWN; OC Mode: TIM_OCMODE_PWM1, TIM_OCMODE_PWM2; OCPolarity: TIM_OCPOLARITY_HIGH, TIM_OCPOLARITY_LOW; 所有的源代码程序都是基于,DMA 控制 STM32L053 的 PWM 脉冲个数的例程。只是更改不同的排列组合,看看有什么差别。 2.1 测试 1/CounterMode = TIM_COUNTERMODE_UP; OCMode = TIM_OCMODE_PWM1; OCPolarity = TIM_OCPOLARITY_HIGH; 显示出来的波形如下图: ![IER9@0M%]MHNY@953(7MR}H.png IER9@0M%]MHNY@953(7MR}H.png](data/attachment/forum/202202/24/194232krwnjbo0d6rjdsfo.png)

测量一下前端比较宽的电平: ![10GPF(TJ}E37H[@86TV]EKP.png 10GPF(TJ}E37H[@86TV]EKP.png](data/attachment/forum/202202/24/194231iu227m7022ltzio2.png)

发现前端的高电平与后面几个脉冲的高电平的持续时间不一样。 2/CounterMode = TIM_COUNTERMODE_UP; OCMode = TIM_OCMODE_PWM1; OCPolarity = TIM_OCPOLARITY_LOW; 显示的波形如下图: ![T~SIRZ`L257LUU]MFW@OG~T.png T~SIRZ`L257LUU]MFW@OG~T.png](data/attachment/forum/202202/24/194232nks9480zqu94u8vf.png)

上面的波形符合自己最初的设想,脉冲个数可控制的 PWM。 比较上面测试的 1/和 2/的波形,发现,第一个脉冲宽度不一样,脉冲结束后的电平也不一样。 而参数的设定只是 OCPolarity = TIM_OCPOLARITY_LOW;与 OCPolarity =TIM_OCPOLARITY_HIGH;的区别。 为什么会有这样的区别呢? 同样的道理,可以测试下只改变 CounterMode = TIM_COUNTERMODE_UP(DOWN);或者只改变OCMode = TIM_OCMODE_PWM1(PWM2);会发现仍然存在上述一样的差别。 2.2 分析原因 这种现象可以总结为这几个参数的搭配有一定的要求, 我这试下来貌似不是能随意搭配使用的。 究其原因进一步分析,在参阅了数据手册之后发现:

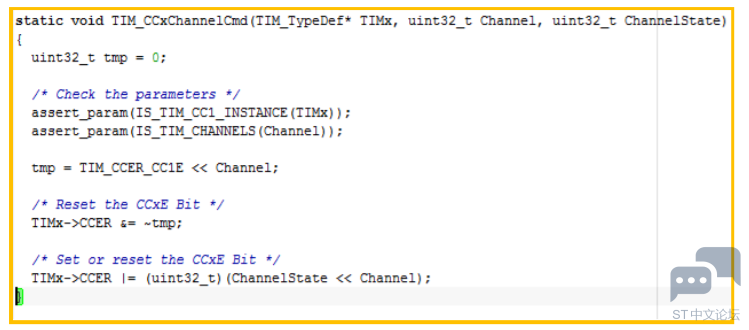

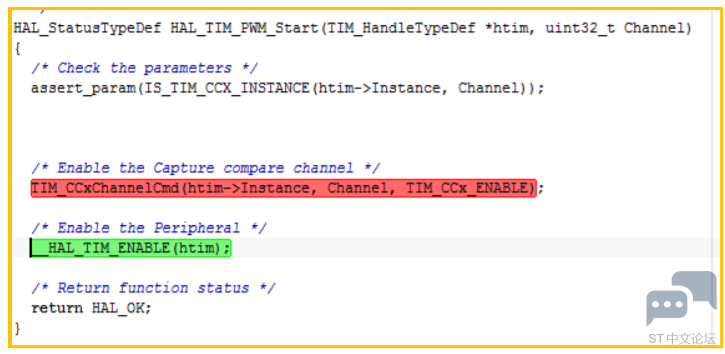

具体原因分析,电平为什么会多一个宽度?执行什么语句之后电平发生了跳变? 程序加上示波器单步运行,发现函数在执行完成这段函数后,电平发生了跳变。

调用上面函数的是下面的函数指令,也就是说在电平跳变之后,定时器才 (__HAL_TIM_ENABLE);才产生 PWM 波形,造成了一定指令的延误。换句话,定时器的使能与否,并不影响内部电平的比较输出。

跳变的电平变化如下图: ![4G@M]QOYAK34OO866{@`GVY.png 4G@M]QOYAK34OO866{@`GVY.png](data/attachment/forum/202202/24/194231u7vzstcfa151yyao.png)

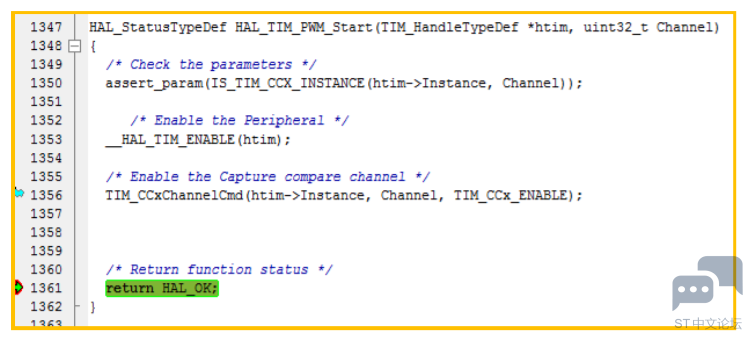

其实,这个现象的原因在其他 MCU 系列中也会出现的。因为电平的比较输出理论上不可能同时与定时器使能同时打开。 如果先把定时器 Enable,然后再使能捕获通道呢?程序修改如下图:

运行后的波形如下图:第一个波形的脉宽有所改善,但是脉冲的个数确是只有 5 个,而程序的设定需要的是 6 个,还是不能彻底解决问题。

所以,综合比较下来,最后一个电平为高或者为底,是根据捕获通道的比较电平决定的。而第一个脉冲的宽度是由定时器的使能和捕获通道的使能的先后顺序决定的。需要选择适合的参数去匹配自己的设计需求。 |

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

2024意法半导体工业峰会:赋能智能电源和智能工业,构筑可持续未来

ST推出灵活、面向未来的智能电表通信解决方案,助力能源转型

微信公众号

微信公众号

手机版

手机版