.png) STMCU小助手

发布时间:2022-3-23 14:00

STMCU小助手

发布时间:2022-3-23 14:00

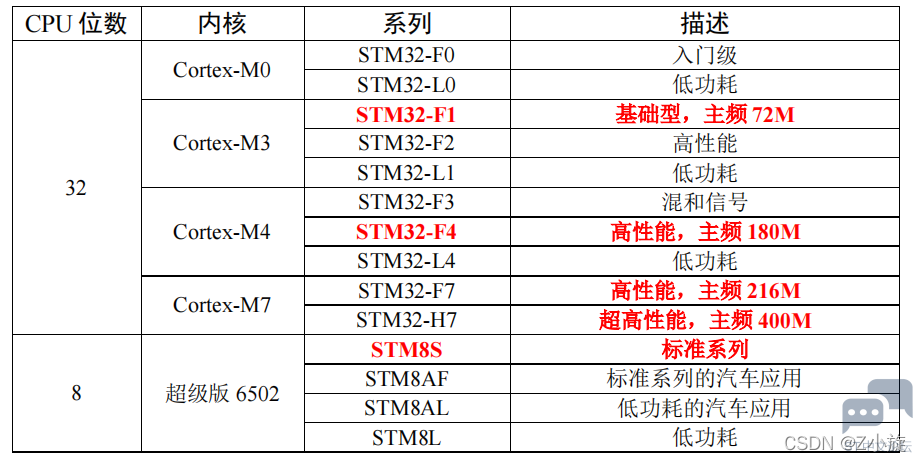

F1 代表了基础型,基于Cortex-M3 内核,主频为 72MHZ,F4 代表了高性能,基于 Cortex-M4 内核,主频 180M,F7 代表了高性能,基于 Cortex-M7 内核,主频 216M。H7 代表了超高性能,基于 Cortex-M7 内核,主频400M

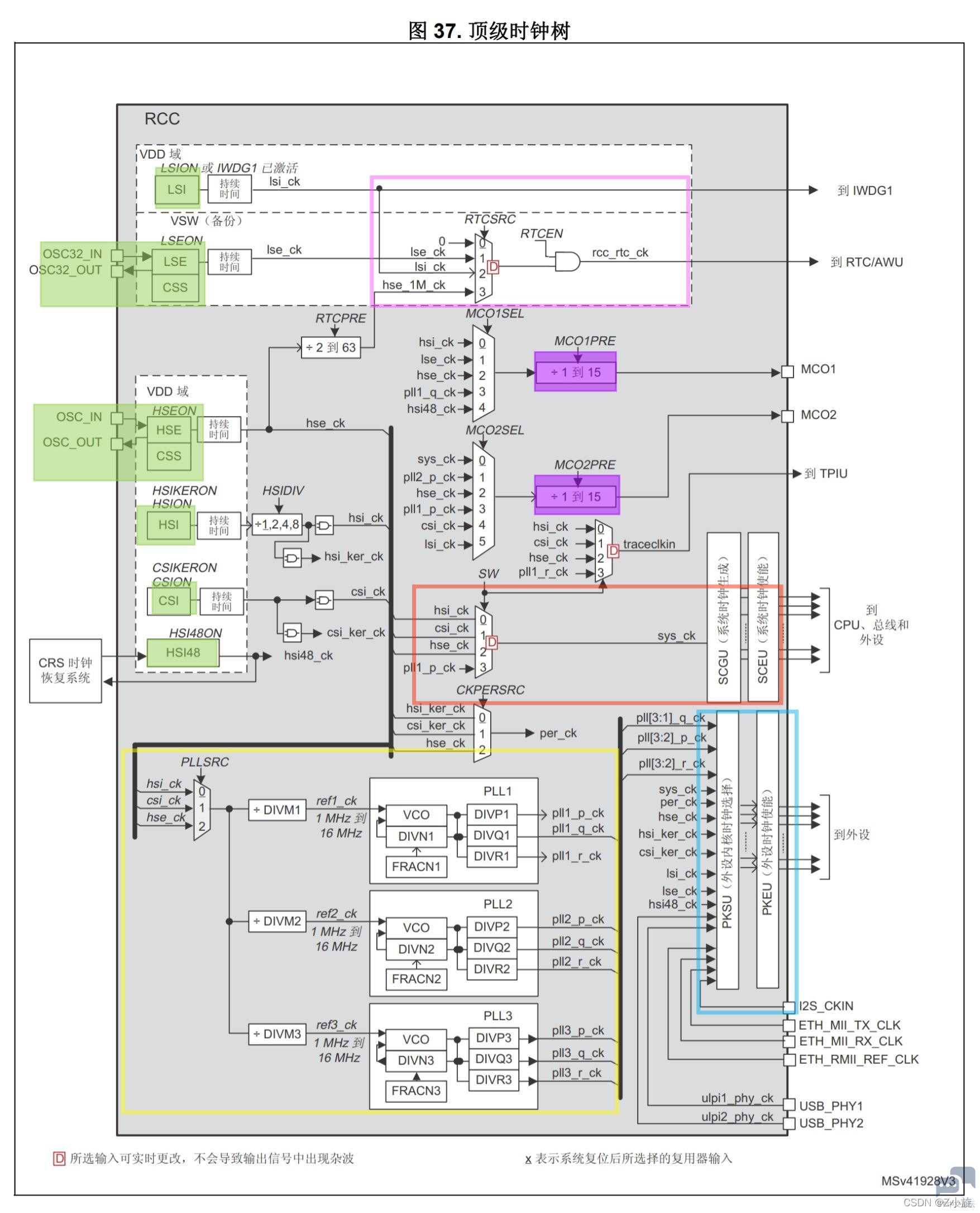

我们今天说的就STM32H7超高性能系列的这个MCU 如果您是初学者的话,建议先看下这篇,会对时钟树有一个基本的认识 首先我们来看下H7的时钟树,乍一看很大,比F1多了太多东西,那我们仔细看,发现也还是很多,别担心,那么接下来我将带你了解下整体的时钟树原理以及各个模块的分析。

因为整体框图太大,所以我们把他分成几部分来分析,首先看下外部输入的时钟源: 外部时钟源 STM32H7共有6个外部时钟源,分别是: HSI(高速内部振荡器)时钟:~ 8 MHz、16 MHz、32 MHz 或 64 MHz HSE(高速外部振荡器)时钟:4 MHz 到 48 MHz LSE(低速外部振荡器)时钟:32 kHz LSI(低速内部振荡器)时钟:~ 32 kHz CSI(低功耗内部振荡器)时钟:~ 4 MHz HSI48 (高速 48 MHz 内部振荡器)时钟:~48 MHz LSI LSI 属于 STM32H7 内部低速时钟源,频率约为 32Khz。 LSI 可作为低功耗时钟源保持运行,供独立看门狗 (IWDG) 和 RTC时钟/自动唤醒单元 (AWU) 使用 LSE LSE 则是外部低速时钟源,常用为 32.768Khz(使用 32.768Khz 晶振或陶瓷谐振器生成) 可作为实时时钟 (RTC) 的时钟源来提供时 钟/日历或其他定时功能,具有功耗低且精度高的优点 HSE HSE 是外部高速时钟,正常我们都用HSE来作为系统时钟输入,常用25Mhz的外部晶振。 系统进入停止或待机模式时,HSE 会自动由硬件禁止 HSE 时钟可被驱动到 MCO1 和 MCO2 输出,以及用作其他应用组件的时钟源 HSI HSI 是内部高速时钟,频率为 64Mhz; 可直接用作系统时钟、外设时钟或 PLL 输入 可使用 HSIDIV预 分频器来选择 8 MHz、16 MHz、32 MHz 或 64 MHz 的 HSI 输出频率 CSI CSI 是低功耗内部时钟,频率为 4Mhz; 可直接用作系统时钟、外设时钟或 PLL 输入 CSI的频率极低,即使经过频率校准后,CSI 频率也不如外部晶振或陶瓷谐振器的频率精度高,其优点就是功耗低。 CSS (Clock security system) 时钟安全系统,也就是监控系统,H7的HSE和LSE两个外部时钟源带有安全监控,一旦使能后,如果 HSE 或LSE启动失败,系统时钟将切换到 HSI。如果使能了中断的话,将进入不可屏蔽中断 NMI。 HSI48 HSI48 是内部高精度时钟源,频率为 48Mhz; 其提供的 48 MHz 时钟可直接用作某些外设的内核时钟 主要用于通过特殊时钟恢复系统 (CRS) 电路为 USB 外设的时钟源使用 好的,通过上述的介绍,你应该明白了H7的几大时钟源,那么这些时钟源后续要被用在哪里,我们再来分析 IWDG, RTC,AWU 上半部紫罗兰色框的部分,就是独立看门狗 (IWDG) 和 RTC时钟/自动唤醒单元 (AWU) 独立看门狗 (IWDG)只能由LSI 提供 RTC和AWU可以由LSE LSE 和 HSE的1M分频来作为时钟源 锁相环PLL PLL(Phase Locked Loop): 为锁相回路或锁相环。总体上起到晶振频率倍频的作用,为系统高速率运行提高必要条件。 VCO(voltage-controlled oscillator):压控振荡器,是PLL 里的一个构成部件

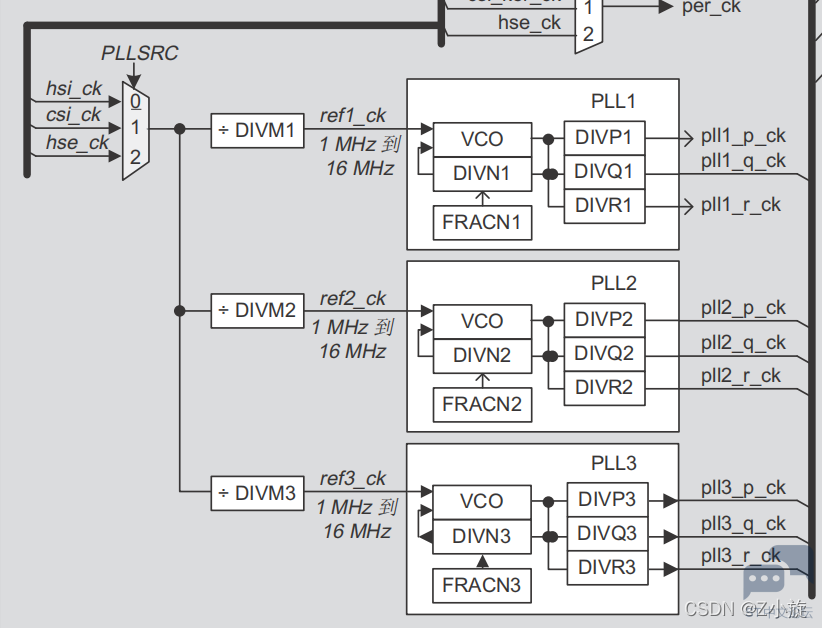

STM32H7一共有三个PLL锁相环: 一个主 PLL (PLL1),通常用于为 CPU 和某些外设提供时钟。 两个专用 PLL(PLL2 和 PLL3),用于为外设生成内核时钟。 PLL的输入时钟源为refx_ck,并且为 PLL 提供的参考时钟的频率 (refx_ck) 必须介于 1 MHz 到 16 MHz 范围内 其中HSI CSI HSE三个时钟源可以作为输入,然后经过PLL时钟源选择器PLLSRC,该选择器主要选择使用哪一个振荡器作为时钟源,再经过DIVMx分频得到1 MHz 到 16 MHz 的时钟频率,我们一般选择 PLL 时钟源来自 hse_ck,一般为 25Mhz DIVMx  LLx时钟源预分频器,用于对PLLSRC选择的时钟源进行分频,取值范围是:2~63 LLx时钟源预分频器,用于对PLLSRC选择的时钟源进行分频,取值范围是:2~63PLL1 PLL1 锁相环,该 PLL 主要用到两路输出:pll1_p_ck 和 pll1_q_ck,其中:pll1_p_ck一般用于 sys_ck 系统时钟的时钟源,最终作为 CPU、SysTick、AXI、AHB1~4 和 APB1~4 等的时钟源;而 pll1_q_ck 则可以通过 PKSU 选择作为部分外设的内核时钟(perx_ker_ck),如 FMC、QSPI、SDMMC1/2 等,至于图中的 pll1_r_ck,并没有用到。 DIVN1 是主 PLL1 vco 的倍频系数,其取值范围是:4~512; DIVP1 是 PLL1 的 P 分 频,用于得到 pll1_p_ck 的频率,其取值范围是:2、4、6…128(必须是偶数); DIVQ1 是 PLL1的 Q 分频,其取值范围是:1~128; DIVR1 则没有用到; FRACN1 是分数倍频系数,它和 DIVN1一起组成 PLL1 的倍频系数,但是我们一般并不需要用到分数倍频 这里以 pll1_p_ck为例,简单介绍下 PLL 输出频率的计算公式(时钟 PLL 输入频率为 hse_ck): ![LGN42T%T]VE`XLKBFZCO($B.png LGN42T%T]VE`XLKBFZCO($B.png](data/attachment/forum/202203/21/143348cj506n0rrn35vjm6.png)

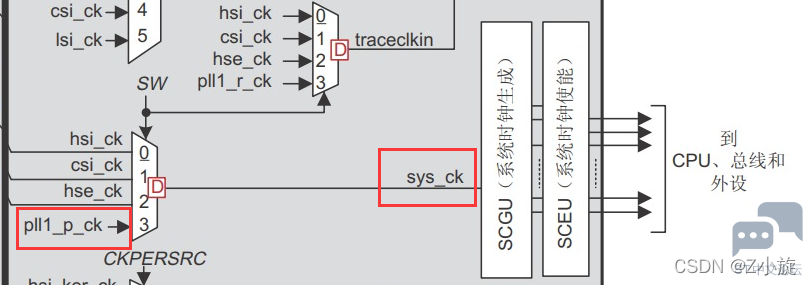

假设外部晶振为 25Mhz,我们需要得到 400Mhz 的 pll1_p_ck 频率来作为系统时钟,则可以设置:DIVM1=5,DIVN1=160,DIVP1=2 即可 PLL2和PLL3跟PLL1类似,这里我们不再赘述。 系统时钟 系统复位后,会自动将 HSI 选作系统时钟,并且所有 PLL 均将关闭。 ,也就是每次系统复位,都会用HSI作为系统时钟,当系统稳定后,可以配置好 PLL1 ,将系统时钟可以切换为 plll1_q_ck(400Mhz),以得到最高性能 当时钟源用于系统时钟时,软件无法关闭所选时钟源,也就是系统时钟软件无法禁止

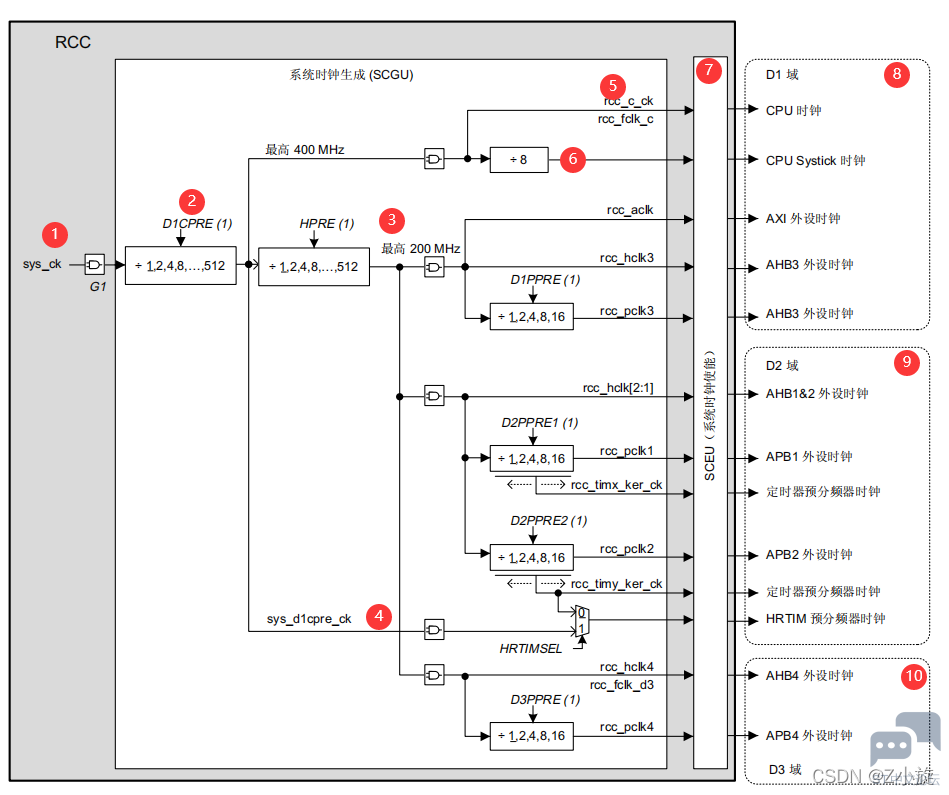

SCGU(System Clock Generation Unit,系统时钟生成单元),用于将 sys_ck 分成各种 时钟频率,比如:CPU 频率、SysTick、AXI、AHB1~4 和 APB1~4 等。 SCEU(System Clock Eable Unit,系统时钟使能单元),用于使能各个外设、总线等的时钟,是一个时钟开关。 下面我们来对系统时钟的生成做一个详细的介绍:

上图主要列出了 STM32H743 系统时钟的生成原理,包括 CPU 时钟、SysTick 时钟、AXI时钟、AHB1~4 和 APB1~4 等,这些时钟对整个系统运行来说非常重要,图中,D1、D2 和 D3 域是 ST 为了支持动态能效管理,所设计的 3 个独立的电源域,每个域都能独立开启/关闭。系统时钟由 SCGU 产生,然后经过 SCEU 做开关,最终输出到各个时钟域(D1、D2 和 D3),从而能够控制和访问各类外设,保证系统的正常运行。 SCGU 输入时钟(sys_ck),该时钟我们一般选择来自 pll1_p_ck,频率为 400Mhz DICPRE:sys_d1cpre_ck 时钟的分频系数,取值范围为 1~512,通过 RCC_ D1CFGR 寄存器的D1CPRE[3:0]位设置,我们一般设置为 1 分频,以得到最高的 sys_d1cpre_ck 频率,400Mhz 经过HPRE分频后给AXI时钟等外设使用,注意这里最高频率为200Mhz,也就是大部分外设的最高频率为200Mhz,所以sys_ck为400Mhz时,HPRE最少为2分频。 给HRTIM做时钟使用,频率可达400Mhz CPU 时钟(rcc_c_ck、rcc_fclk_c),CPU 时钟是直接来自 sys_d1cpre_ck,没有分频器,频率为 400Mhz SysTick 时钟分频器(固定 8 分频),这个在图中是有错误的,实际上这个分频器是没有的(硬件 bug),因此 SysTick 的时钟频率,直接来自 sys_d1cpre_ck,频率为 400Mhz系统时钟 使能单元(SCEU),它能够对 D1、D2 和 D3 域内的所有外设时钟进行开/关控制,所以在使用外设的时候,必须设置 SCEU,使能其时钟,否则外设无法使用,也就是配置各个外设时钟的使能ENR D1 域,是高性能域,主要为CPU时钟和AXI外设,AHB3外设 D2 域,通信接口域,主要进行数据通信工作,减轻 CPU 的负担。此域包括:AHB1、AHB2、APB1 和 APB2 等时钟部分。 D3 域,数据批处理域,此域包括 AHB4 和 APB4 等时钟部分 MOC1/MOC2 两个时钟输出 (MCO) 引脚可供使用,分别为 MCO1 和 MCO2。可以为每个输出选择一个时钟源。 GPIO 端口必须在复用功能模式下使用MCO。 MCO 输出提供的时钟频率不能超出最大引脚速度 MCO1 可以在 PA8 引脚输出 MCO2 可以在 PC9 引脚输出 PKSU/PKEU SCEU :用于控制外设的访问时钟(访问寄存器) PKEU: 用于控制外设的内核时钟(生成控制时序,如波特率等) 并不是所有的外设都需要用到 PKEU,因为有些外设并不需要生成时序,没有所谓的外设内核时钟,比如 DMA、OPAMP 等,这些外设只需要在SCEU 进行使能即可 下图是详细的外设时钟使能框图

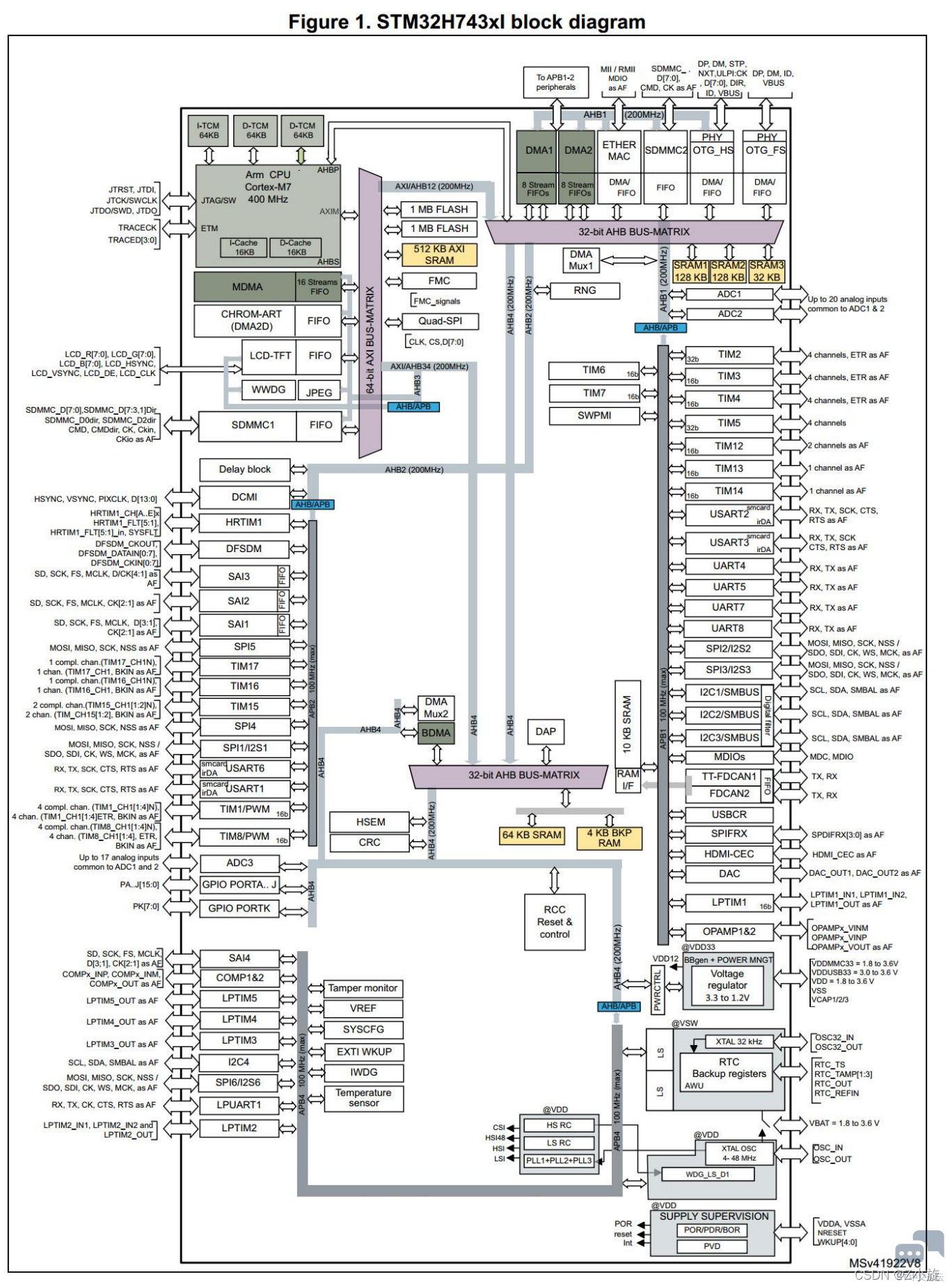

上半部分的SCGU跟SCEU已经讲过,这里我们只说下下半部分: 外设内核时钟选择单元(PKSU,即:Peripheral Kernel clock Selection Unit),用于选择某个外设的内核时钟来源,具体的选择关系。 外设内核时钟使能单元(PKEU,即:Peripheral Kernel clock Enable Unit),此部分将PKSU处选择的外设内核时钟进行使能/禁止操作,最终控制是否输出内核时钟(rcc_perx_ker_ck)给外设。 内核控制逻辑(Kernel Control Logic),用于控制 PKEU 是否输出内核时钟给外设,它有很多控制信号,其中我们常用的是 PERxEN,通过这个位的设置就可以控制具体外设内核时钟的开/关。 外设内核时钟(rcc_perx_ker_ck),该时钟用于驱动外设产生时序,如波特率、时钟脉冲等。大部分外设都需要用到 rcc_perx_ker_ck,比如串口、SPI、IIC、FMC、SAI、LTDC 和CAN 等。 这里推荐一张STM32H7 的数据手册里面非常棒的框图(在数据手册里面检索 Figure 1 就可以找到),可以对H7的整体架构有一个直观的了解,可以看到每个外设所挂的总线,和各个总线的最大时钟频率。 AHB (Advanced High-performance Bus) 高级高性能总线 APB (Advanced Peripheral Bus) 高级外围总线 AXI (Advanced eXtensible Interface) 高级可拓展接口 AHB主要是针对高效率、高频宽及快速系统模块所设计的总线,它可以连接如微处理器、芯片上或芯片外的内存模块和DMA等高效率模块。 APB主要用在低速且低功率的外围,可针对外围设备作功率消耗及复杂接口的最佳化。APB在AHB和低带宽的外围设备之间提供了通信的桥梁,所以APB是AHB或ASB的二级拓展总线。 AXI:高速度、高带宽,管道化互联,单向通道,只需要首地址,读写并行,支持乱序,支持非对齐操作,有效支持初始延迟较高的外设,连线非常多。 这些内容加起来就定义出一套为了高性能SoC而设计的片上通信的标准。

比如你可以看到SYSCLK(Hz) = 400MHz (CPU Clock) 也就知道上述CPU框图初的错误 可以看到CPU外挂了一个 64bit的 AXI BUS 还有一个32bit的 AHB BUS FLASH FMC QSPI 这些都是在AXI总线上的 常用的 TIM UART SPI IIC挂在AHB总线上 64位的AXI总线又分出了一个32位的 AHB4 等等 右下角的是时钟的框图,可以看到RTC时钟 看门狗时钟 可以看到HSE的时钟是4-48Mhz 然后给APB4总线外挂 经过三个PLL锁相环 再做外部输出 ![]V})_607HGDVD(Q@C1T1%]2.png ]V})_607HGDVD(Q@C1T1%]2.png](data/attachment/forum/202203/21/143019ar9t0zrda28tdit9.png)

再比如200Mhz的AHB4经过分频生成了APB4最高位100Mhz ![9_~6DV(3U[]N0315QW9[S[T.png 9_~6DV(3U[]N0315QW9[S[T.png](data/attachment/forum/202203/21/143017vonawkrj22yx5zzg.png)

APB1 定时器有 TIM2, TIM3 ,TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14,LPTIM1 APB2 定时器有 TIM1, TIM8 , TIM15, TIM16,TIM17 APB3 上有 LCD-TFT FIFO APB4 定时器有 LPTIM2,LPTIM3,LPTIM4,LPTIM5 还有下面的总线系统框架 ![SWA]V0DDFM@IPTU@3BUX.png SWA]V0DDFM@IPTU@3BUX.png](data/attachment/forum/202203/21/143020sumlq4jkqwz4o14a.png)

可以很清楚的看到外设共分为三个域:D1 Domain,D2 Domain 和 D3 Domain。 ◆ D1 Domain D1 域中的各个外设是挂在 64 位 AXI 总线组成 6*7 的矩阵上。 6 个从接口端 ASIB1 到 ASIB6 外接的主控是 LTDC,DMA2D,MDMA,SDMMC1,AXIM 和 D2-to-D1 AHB 总线。 7 个主接口端 AMIB1 到 AMIB7 外接的从设备是 AHB3 总线,Flash A,Flash B,FMC 总线,QSPI 和 AXI SRAM。 AHB3也是由 AXI 总线分支出来的,然后再由 AHB3 分支出 APB3 总线。 ◆ D2 Domain D2 域的各个外设是挂在 32 位 AHB 总线组成 10*9 的矩阵上。 10 个从接口外接的主控是 D1-to-D2 AHB 总线,AHBP 总线,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1 和 USB HS2。 9 个主接口外接的从设备是 SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB1,APB2,D2-to-D1 AHB总线和 D2-to-D3 AHB 总线。 ◆ D3 Domain D3 域的各个外设是挂在 32 位 AHB 总线组成 3*2 的矩阵上。 3 个从接口外接的主控 D1-to-D3 AHB 总线,D2-to-D3 AHB 总线和 BDMA。 2 个主接口外接的从设备是 AHB4,SRAM4 和 Bckp SRAM。另外 AHB4 也是这个总线矩阵分支出来的,然后再由 AHB4 分支出 APB4 总线。 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版