.png) STMCU小助手

发布时间:2022-3-31 11:00

STMCU小助手

发布时间:2022-3-31 11:00

|

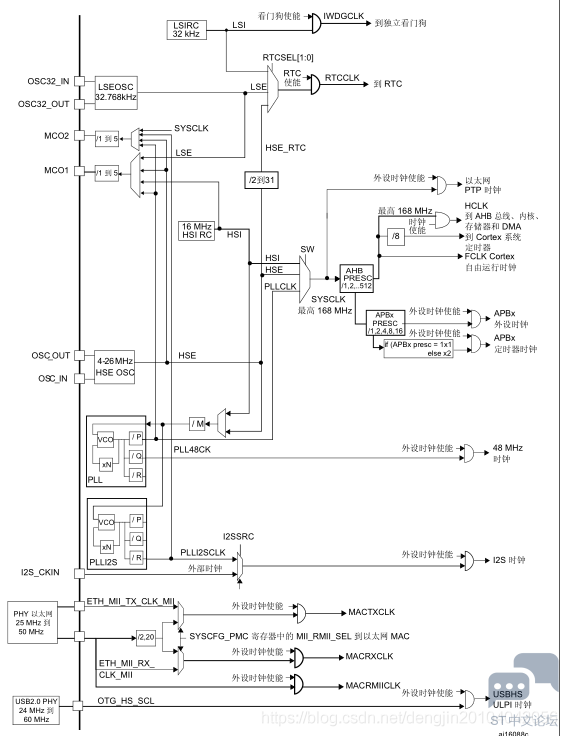

01. 时钟概述 可以使用三种不同的时钟源来驱动系统时钟 (SYSCLK): ● HSI 振荡器时钟 ● HSE 振荡器时钟 ● 主 PLL (PLL) 时钟 器件具有以下两个次级时钟源: ● 32 kHz 低速内部 RC (LSI RC),该 RC 用于驱动独立看门狗,也可选择提供给 RTC 用于停机/待机模式下的自动唤醒。 ● 32.768 kHz 低速外部晶振(LSE 晶振),用于驱动 RTC 时钟 (RTCCLK)对于每个时钟源来说,在未使用时都可单独打开或者关闭,以降低功耗

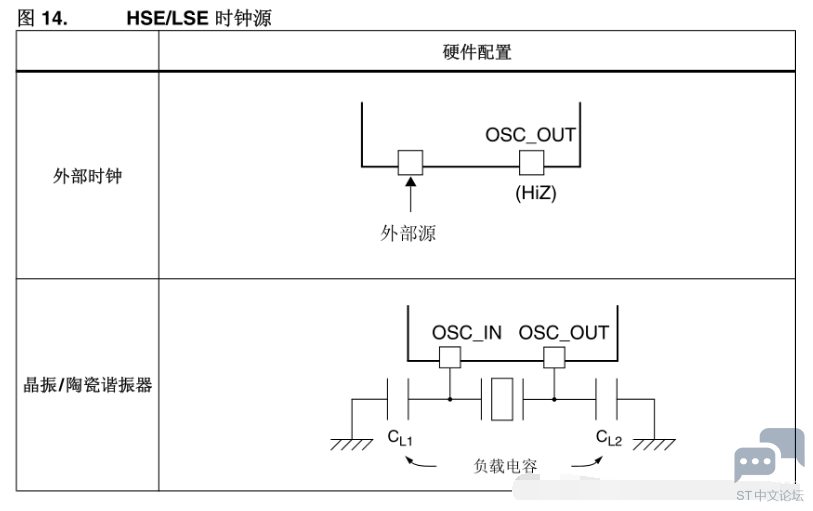

时钟控制器为应用带来了高度的灵活性,用户在运行内核和外设时可选择使用外部晶振或者使用振荡器,既可采用最高的频率,也可为以太网、USB OTG FS 以及 HS、I2S 和 SDIO等需要特定时钟的外设保证合适的频率 可通过多个预分频器配置 AHB 频率、高速 APB (APB2) 和低速 APB (APB1)。AHB 域的最大频率为 168 MHz。高速 APB2 域的最大允许频率为 84 MHz。低速 APB1 域的最大允许频率为 42 MHz。 除以下时钟外,所有外设时钟均由系统时钟 (SYSCLK) 提供: ● 来自于特定 PLL 输出 (PLL48CLK) 的 USB OTG FS 时钟 (48 MHz)、基于模拟技术的随机数发生器 (RNG) 时钟 (<=48 MHz) 和 SDIO 时钟 (<=48 MHz)。 ● I2S 时钟 要实现高品质的音频性能,可通过特定的 PLL (PLLI2S) 或映射到 I2S_CKIN 引脚的外部时钟提供 I2S 时钟。有关 I2S 时钟频率和精度的详细信息,请参见 第 27.4.4 节:时钟发生器 。 ● 由外部 PHY 提供的 USB OTG HS (60 MHz) 时钟 ● 由外部 PHY 提供的以太网 MAC 时钟(TX、RX 和 RMII)。有关以太网配置的更多信息,请参见以太网外设说明中的 第 29.4.4 节: MII/RMII 选择 。当使用以太网时,AHB时钟频率至少应为 25 MHz。 RCC 向 Cortex 系统定时器 (SysTick) 馈送 8 分频的 AHB 时钟 (HCLK)。SysTick 可使用此时钟作为时钟源,也可使用 HCLK 作为时钟源,具体可在 SysTick 控制和状态寄存器中配置。 STM32F405xx/07xx 和 STM32F415xx/17xx 的定时器时钟频率由硬件自动设置。分为两种情况: 如果 APB 预分频器为 1,定时器时钟频率等于 APB 域的频率。 否则,等于 APB 域的频率的两倍 (×2)。 02. HSE时钟 高速外部时钟信号 (HSE) 有 2 个时钟源: ● HSE 外部晶振/陶瓷谐振器 ● HSE 外部用户时钟 谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选振荡器的不同做适当调整。

外部源(HSE 旁路) 在此模式下,必须提供外部时钟源。此模式通过将 RCC 时钟控制寄存器 (RCC_CR) 中的HSEBYP 和 HSEON 位置 1 进行选择。必须使用占空比约为 50% 的外部时钟信号(方波、正弦波或三角波)来驱动 OSC_IN 引脚,同时 OSC_OUT 引脚应保持为高阻态 (hi-Z)。 外部晶振/ 陶瓷谐振器(HSE 晶振) HSE 的特点是精度非常高。 RCC 时钟控制寄存器 (RCC_CR) 中的 HSERDY 标志指示高速外部振荡器是否稳定。在启动时,硬件将此位置 1 后,此时钟才可以使用。如在 RCC 时钟中断寄存器 (RCC_CIR) 中使能中断,则可产生中断。 HSE 晶振可通过 RCC 时钟控制寄存器 (RCC_CR) 中的 HSEON 位打开或关闭。 03. HSI时钟 HSI 时钟信号由内部 16 MHz RC 振荡器生成,可直接用作系统时钟,或者用作 PLL 输入。HSI RC 振荡器的优点是成本较低(无需使用外部组件)。此外,其启动速度也要比 HSE 晶振块,但即使校准后,其精度也不及外部晶振或陶瓷谐振器。 校准 因为生产工艺不同,不同芯片的 RC 振荡器频率也不同,因此 ST 会对每个器件进行出厂校准,达到 T A = 25 °C 时 1% 的精度。 复位后,工厂校准值将加载到 RCC 时钟控制寄存器 (RCC_CR) 的 HSICAL[7:0] 位中。 如果应用受到电压或温度变化影响,则这可能也会影响到 RC 振荡器的速度。用户可通过RCC 时钟控制寄存器 (RCC_CR) 中的 HSITRIM[4:0] 位对 HSI 频率进行微调。 RCC 时钟控制寄存器 (RCC_CR) 中的 HSIRDY 标志指示 HSI RC 是否稳定。在启动时,硬件将此位置 1 后,HSI 才可以使用。 HSI RC 可通过 RCC 时钟控制寄存器 (RCC_CR) 中的 HSION 位打开或关闭。 HSI 信号还可作为备份时钟源(辅助时钟)使用,以防 HSE 晶振发生故障。 04. PLL配置 STM32F4xx 器件具有两个 PLL: ● 主 PLL (PLL) 由 HSE 或 HSI 振荡器提供时钟信号,并具有两个不同的输出时钟: — 第一个输出用于生成高速系统时钟(最高达 168 MHz) — 第二个输出用于生成 USB OTG FS 的时钟 (48 MHz)、随机数发生器的时钟 (<=48 MHz) 和 SDIO 时钟 (<=48 MHz)。 ● 专用 PLL (PLLI2S) 用于生成精确时钟,从而在 I2S 接口实现高品质音频性能。 由于在 PLL 使能后主 PLL 配置参数便不可更改,所以建议先对 PLL 进行配置,然后再使能(选择 HSI 或 HSE 振荡器作为 PLL 时钟源,并配置分频系数 M、N、P 和 Q)。 PLLI2S 使用与 PLL 相同的输入时钟(PLLM[5:0] 和 PLLSRC 位为两个 PLL 所共用)。但是,PLLI2S 具有专门的使能/禁止和分频系数(N 和 R)配置位。在 PLLI2S 使能后,配置参数便不能更改。 当进入停机和待机模式后,两个 PLL 将由硬件禁止;如将 HSE 或 PLL(由 HSE 提供时钟信号)用作系统时钟,则在 HSE 发生故障时,两个 PLL 也将由硬件禁止。RCC PLL 配置寄存器 (RCC_PLLCFGR) 和RCC 时钟配置寄存器 (RCC_CFGR) 可分别用于配置 PLL 和 PLLI2S。 05. LSE时钟 LSE 晶振是 32.768 kHz 低速外部 (LSE) 晶振或陶瓷谐振器,可作为实时时钟外设 (RTC) 的时钟源来提供时钟/日历或其它定时功能,具有功耗低且精度高的优点。 LSE 晶振通过 RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSEON 位打开和关闭。 RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSERDY 标志指示 LSE 晶振是否稳定。在启动时,硬件将此位置 1 后,LSE 晶振输出时钟信号才可以使用。如在 RCC 时钟中断寄存器(RCC_CIR) 中使能中断,则可产生中断。 外部源(LSE 旁路) 在此模式下,必须提供外部时钟源,最高频率不超过 1 MHz。此模式通过将 RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSEBYP 和 LSEON 位置 1 进行选择。必须使用占空比约为 50%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC32_IN 引脚,同时 OSC32_OUT 引脚应保持为高阻态 (Hi-Z)。 06. LSI时钟 LSI RC 可作为低功耗时钟源在停机和待机模式下保持运行,供独立看门狗 (IWDG) 和自动唤醒单元 (AWU) 使用。时钟频率在 32 kHz 左右。有关详细信息,请参见数据手册的电气特性部分。 LSI RC 可通过 RCC 时钟控制和状态寄存器 (RCC_CSR) 中的 LSION 位打开或关闭。 RCC 时钟控制和状态寄存器 (RCC_CSR) 中的 LSIRDY 标志指示低速内部振荡器是否稳定。在启动时,硬件将此位置 1 后,此时钟才可以使用。如在 RCC 时钟中断寄存器 (RCC_CIR) 中使能中断,则可产生中断。 07. 系统时钟 (SYSCLK)选择 在系统复位后,默认系统时钟为 HSI。在直接使用 HSI 或者通过 PLL 使用时钟源来作为系统时钟时,该时钟源无法停止。 只有在目标时钟源已就绪时(时钟在启动延迟或 PLL 锁相后稳定时),才可从一个时钟源切 换到另一个。如果选择尚未就绪的时钟源,则切换在该时钟源就绪时才会进行。RCC 时钟 控制寄存器 (RCC_CR) 中的状态位指示哪个(些)时钟已就绪,以及当前哪个时钟正充当系 统时钟。 |

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

微信公众号

微信公众号

手机版

手机版