.png) STMCU小助手

发布时间:2022-4-24 22:16

STMCU小助手

发布时间:2022-4-24 22:16

|

5.3 配置工程文件 默认情况下会进入“LEDTest_Project.ioc”界面,也可以通过双击工程目录的“LEDTest_Project.ioc”进入。点击“Project Manager->Code Generator”,将“Generated files”第1和第2选项勾选,其余默认。

5.4 配置芯片时钟 5.4.1 配置外部时钟引脚 点击“Pinout & Configuration->System Core->RCC”,在“RCC Mode”中将“High Speed Clock(HSC)”设置为“Crystal/Ceramic Resonator”,其余保持默认。 ![FT5}2SLU]}$LL20F6V~24%5.png FT5}2SLU]}$LL20F6V~24%5.png](data/attachment/forum/202204/24/221713rcgt6d7ghczkwbbp.png)

第一个选项High Speed Clock即为HSE(高速时钟源),一般为接外部晶振为主,因此选择Crystal/Ceramic Resonator(使用晶振/外部陶瓷振荡器)来使用外部晶振。 第二个选项Low Speed Clock(低速时钟源)若无特殊需求,不用打开。 第三个选项以及第四,五,六个选项用是用来配置MCO1、MCO2和PC9引脚是否要作为时钟输入脚来使用,无特殊需求不用打开。 配置好晶振设置后可以看到右边芯片实时会显示引脚状态已改变。 5.4.2 配置时钟频率 本指南使用的STM32H743II芯片,最大CPU时钟可以配置到480MHZ,外部晶振是25MHZ。点击“Clock Configuration”,在“Input Frequency”输入“25”,在“PLL Source Mux”选择“HSE”作为时钟输入,在“System Clock Mux”选择“PLLCLK”作为时钟输入,在“SPI1,2,3 Clock Mux”输入“480”,然后按下回车键,软件自动计算设置好其他选项,目前时钟配置只需要满足跑马灯实验,其他暂不设置,保持默认。

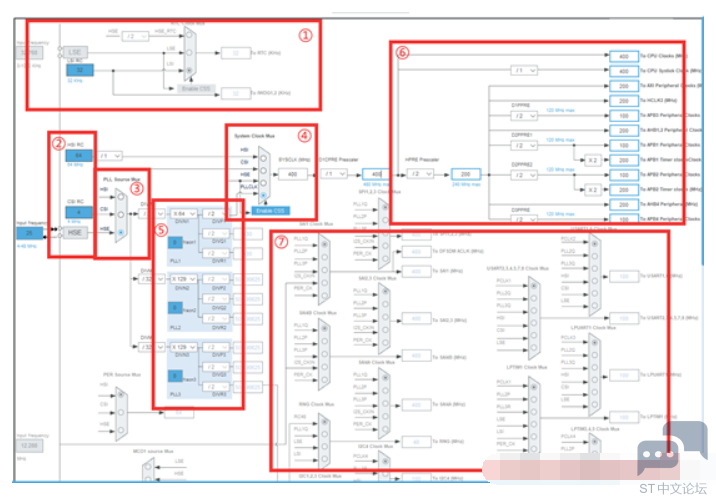

5.4.3 时钟图介绍 本章节不涉及操作,可以忽略跳过。 STM32CubeIDE专门为时钟系统分频单独建了一套配置体系,在主界面点击“Clock Configuration”即可进入时钟树配置界面。由于该部分没有汉化因此单独介绍。

简单介绍一下时钟树中各个整体的名称以及内容:

①:低速时钟源,包括LSI和LSE两个,LSI属于STM32H7内部低速时钟源,频率约为32Khz。LSE则是外部低速时钟源,为32.768Khz(使用32.768Khz外部晶振)。这两个时钟源一般用于看门狗和RTC。 ②:高速时钟源,包括:HSE、HIS、CSI和HSI48。HSE是外部高速时钟,由于使用了25M的外部晶振,所以HSE频率为25Mhz;HSI是内部高速时钟,频率为 64Mhz; CSI是低功耗内部时钟,频率为4Mhz;HSI48是内部高精度时钟源,频率为 48Mhz,配合CRS可以直接作为USB的时钟源使用。 ③:PLL1~3的时钟源选择器,一般选择PLL时钟源来自HSE_ck, 25Mhz。 ④:sys_ck时钟选择器,可选择sys_ck的时钟来自:HSI_ck、CSI_ck、HSE_ck 或pll1_p_ck等,在PLL1还没设置好的时候,系统默认是选择hsi_ck(64Mhz)作为时钟源的,当PLL1配置好以后,则系统时钟可以切换为plll1_q_ck(480Mhz),以得到最高性能。 ⑤:PLL1 锁相环,该 PLL 主要用到两路输出: pll1_p_ck 和 pll1_q_ck,其中: pll1_p_ck一般用于 sys_ck 的时钟源,最终作为 CPU、 SysTick、 AXI、 AHB1~4 和 APB1~4 等的时钟源;而 pll1_q_ck 则可以通过 PKSU 选择作为部分外设的内核时钟( perx_ker_ck),如 FMC、 QSPI、SDMMC1/2 等。

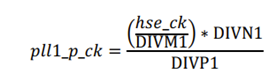

假设外部晶振为25Mhz,若需要得到400Mhz的pll1_p_ck频率,则可以设置:DIVM1=5,DIVN1=160,DIVP1=2即可。其他分频输出(pll1_q_ck/pll1_r_ck)计算方法与上式相似。 ⑥:SCGU(System Clock Generation Unit,系统时钟生成单元)以及SCEU(System Clock Eable Unit,系统时钟使能单元)于将sys_ck分成各种时钟频率,用于使能各个外设、总线等,如:CPU 频率、SysTick、AXI、AHB14和APB14 等。 ⑦:PKSU(Peripheral Kernel clock Selection Unit,外设内核时钟选择单元)以及PKEU(Peripheral Kernel clock Enable Unit,外设内核时钟使能单元),用于选择部分外设的内核时钟源以及用于使能部分外设的内核时钟,STM32H7内部很多外设都可以自由选择内核时钟来源,从而提高灵活性,详见《STM32H7xx 参考手册》 335 页, Table 51。 ![5SH@$PE6M}7Q3]N]GG{~]XO.png 5SH@$PE6M}7Q3]N]GG{~]XO.png](data/attachment/forum/202204/24/221714i7wz76az76jpd3ey.png)

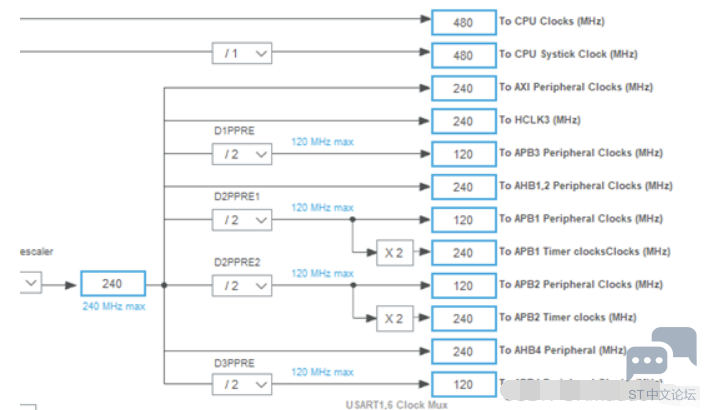

此图片频率400为方便讲解设置,实际还是按最大频48MHZ来设置! ①:Input frequency:输入晶振频率,在这个选项中可根据单片机的外部晶振来填写晶振频率,下面的蓝色范围为可接受频率范围。这边按25MHZ来配。 ②:PLL source Mux:PLL时钟源选择器,选择HSE高速时钟源即可。 ③:PLL 分频系数 M 配置。由于我们需要系统时钟设为480MHZ,因此需要通过PLL分频来把25MHZ的晶振时钟转换为系统时钟。 ④:主 PLL 倍频系数 N 配置。倍频系数 N(自动配频会自动计算) ⑤:主 PLL 分频系数 P 配置。分频系数 P(自动配频会自动计算) ⑥:系统时钟时钟源选择,选择PLLCLK,系统时钟就会和PLL同步为480MHZ ⑦,⑧:SYSCLK系统时钟,引脚的工作频率都由它分频来配置。

系统时钟分频得到的总线时钟:AHB(Advanced High performance Bus,高级高性能总线,用于高性能模块CPU、DMA、DSP之间的连接)、APB1、APB2、APB3和APB总线时钟(Advanced Peripheral Bus,高性能外围总线,用于低带宽的周边外设之间的连接,例如UART)以及Systick时钟的最终来源都是系统时钟SYSCLK。 |

经验分享 | 利用TIMER定时和捕获功能实现编解码演示

STM32 LSE 不起振排查指南:五大核心原因与快速解决方案

我心中的ST中文论坛

经验分享 | 利用STM32 TIMER实现同频跟随输出示例

2025软件工具兔哥知道

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

经验分享 | 利用STM32 TIMER实现同频跟随输出示例

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

微信公众号

微信公众号

手机版

手机版