.png) STMCU小助手

发布时间:2022-6-22 21:01

STMCU小助手

发布时间:2022-6-22 21:01

|

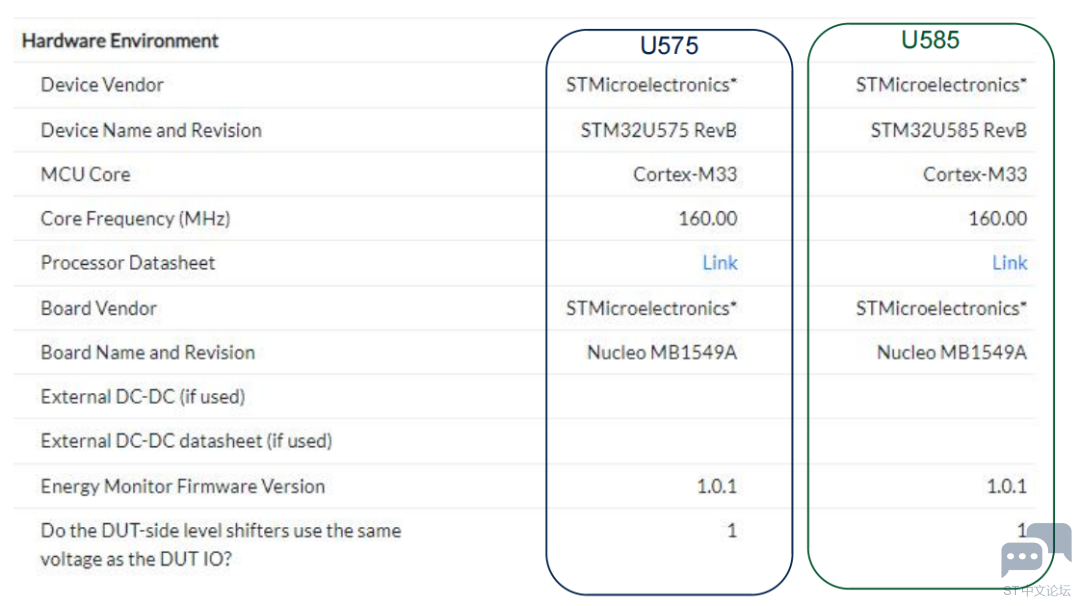

STM32U5 是ST在2021年推出的新一代超低功耗产品,不仅在工艺(40nm制程),性能(主频160MHz),低功耗(超低功耗模式低至:110nA,动态功耗低至:19μA/MHz )等多个方面都有显著提升,在信息安全方面也增加很多新特性。STM32U5目前已经推出STM32U575、 STM32U585两个系列,这两者区别之一是 STM32U585芯片内置了AES,SAES和PKA硬件加解密引擎, STM32U575只有软件方式实现的加解密算法。STM32U5的硬件加解密引擎相对于纯软件实现有多方面的优势,比如:硬件SAES、PKA模块具备侧信道攻击防御能力,有更高的安全性,更高的性能,更快的运算速度,计算过程中不需要CPU参与,CPU可以处理其他更具有实时性要求的任务,同时在存储空间占用和功耗上也更有优势。我们将从性能、功耗和存储空间占用几方面 ,将STM32U5硬件加解密引擎和软件实现算法做一个对比。" n0 P+ X& }" M, R2 R0 B3 J 通过EEMBC SecureMarkTLS评测跑分,对比软硬件算法实现 . Q3 {9 k' |4 Y我们使用 EEMBC SecureMarkTLS 对U575(纯软件)和U585(带硬件加速引擎)分别进行性能和能耗的对比。EEMBC SecureMark是一个公认标准化的、用于衡量加解密操作效率的基准测试套件。在SecureMark中,EEMBC计划支持对不同应用领域的各种安全配置进行测试和分析。其中第一个授权可用的是SecureMark-TLS,它专注于物联网(IoT)边缘节点的传输层安全(TLS)。SecureMark-TLS基准配置文件对用于安全互联网通信的传输层安全(TLS)协议所需的加解密操作进行建模。TLS协议提供了交换消息的机密性和完整性,并且可以对通信双方进行身份验证。SecureMark-TLS测量物理设备(可以是开发板或最终产品) 在执行一组指定的加解密操作时的性能和功耗。功耗测量被换算成一个最终的单一分数,该分数代表物联网边缘节点设备的TLS操作。[url=https://www.eembc.org/securemark/][/url] ✦ EEMBC SecureMarkTLS跑分对比 可以看到 ST发布的使用 EEMBC SecureMarkTLS测试套件的测试报告。选择STM32U575 RevB Core MHz:160 和STM32U585 RevB Core MHz:160 (我们选择的是最大主频 160MHz),可以看到测试的硬件环境如下图所示:

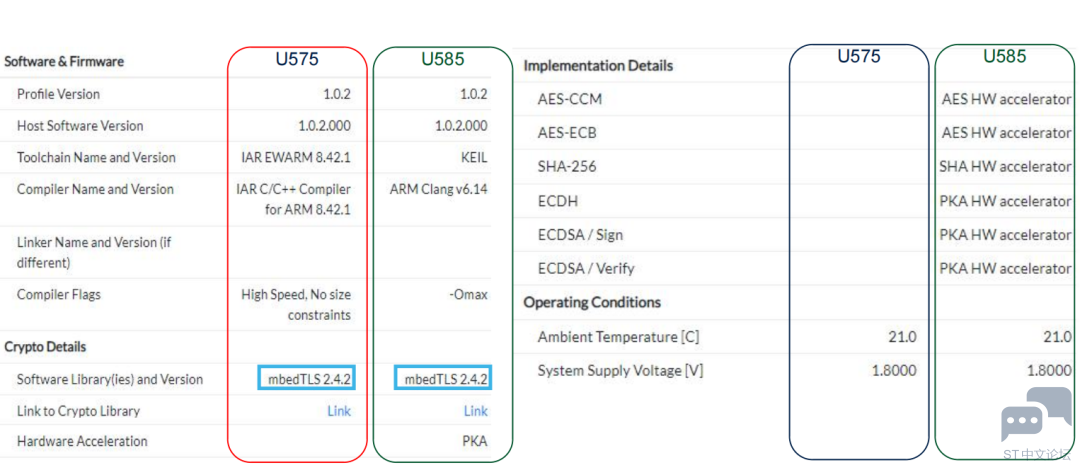

测试的软件和Crypto信息如下:

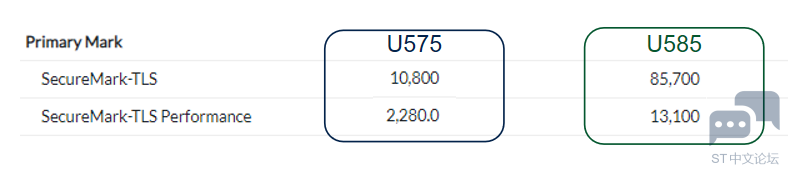

请注意蓝框中标出测试的算法库和版本:Software Library(ies) and Version: mbedTLS 2.4.2。mbedTLS 现已被arm公司收购并由arm技术团队进行维护更新,是对TLS和SSL协议实现的算法库。mbedTLS的目标是:易于理解,使用,集成和扩展。它主要是面向小型嵌入式设备,代码紧凑,而且执行效率高,可以说是行业内最小巧的SSL加密算法库。并且mbedTLS是完全OpenSource的,支持Apache 2.0 license 或者GPL 2.0 license双重许可,可以自由应用于商业项目中。在 U575 上,我们直接运行的是开源的mbedTLS 2.4.2,算法部分是开源的mbedTLS 2.4.2里面实现的软件算法; 在U585上,同样运行的是开源的mbedTLS 2.4.2,但算法部分使用U585自带的硬件加解密引擎。在下图的测试结果中,SecureMark-TLS 是对整体功耗的跑分总评,SecureMark-TLS Performance 是对整体性能的跑分总评。后面我们又分别列出了不同算法的性能和功耗的分数。Benchmark跑分总评) |: E1 o5 r. z

说明:

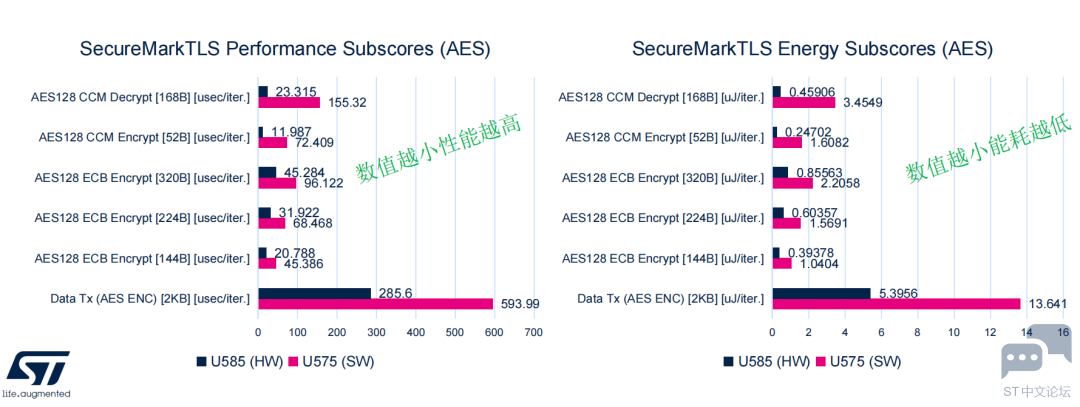

Mbedtls软件作为运行的代码进行benchmark,对比U575纯软件和U585带硬件加速的性能和能耗。 Benchmark子项:AES 性能 + 能耗

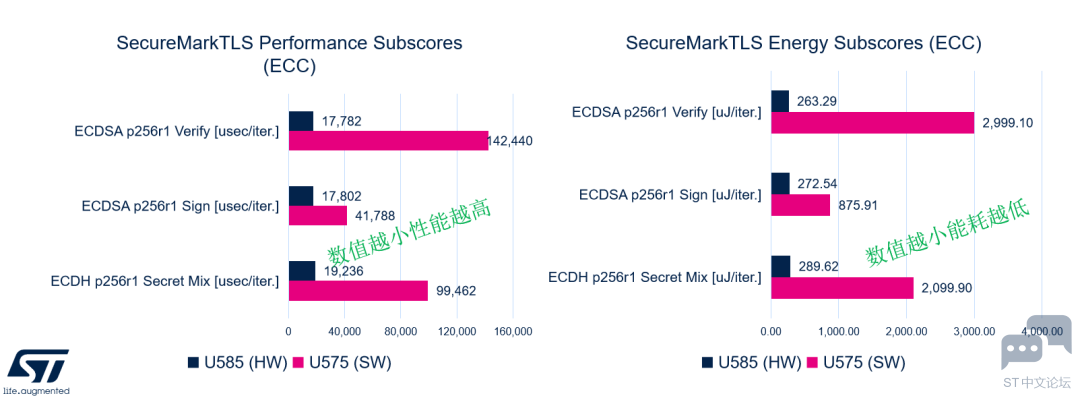

Benchmark子项:ECC 性能 + 能耗

硬件加解密引擎(HAL驱动)与Cryptolib软件算法对比 / L' [, ]5 A A% `7 }: I软件算法部分采用ST 的 X-CUBE-CRYPTOLIB作为对比的对象。X-CUBE-CRYPTOLIB是基于STM32的软件算法库,支持STM32全系列产品,提供多种主流算法的实现,针对不同的内核进行了算法优化,支持多种使用的配置模式(高性能、小代码量等选择)。硬件引擎的使用则通过直接调用HAL驱动来完成。我们通过以下几个常用的典型算法进行对比,比较的内容为软硬件实现的性能和存储空间占用情况:

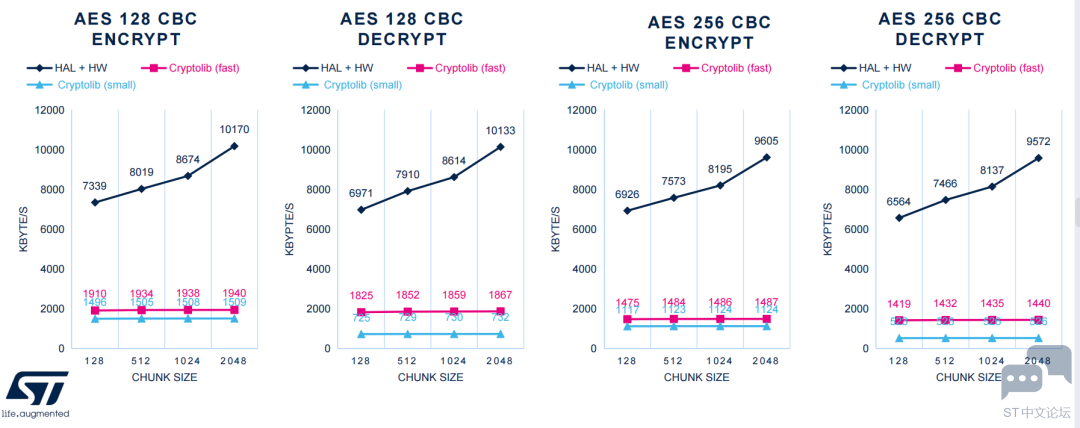

✦ 性能对比 AES CBC 数据流加解密:每秒数据处理能力 (以8KB数据做测试, 每次处理大小分别为128, 512, 1024, 2048字节的结果)

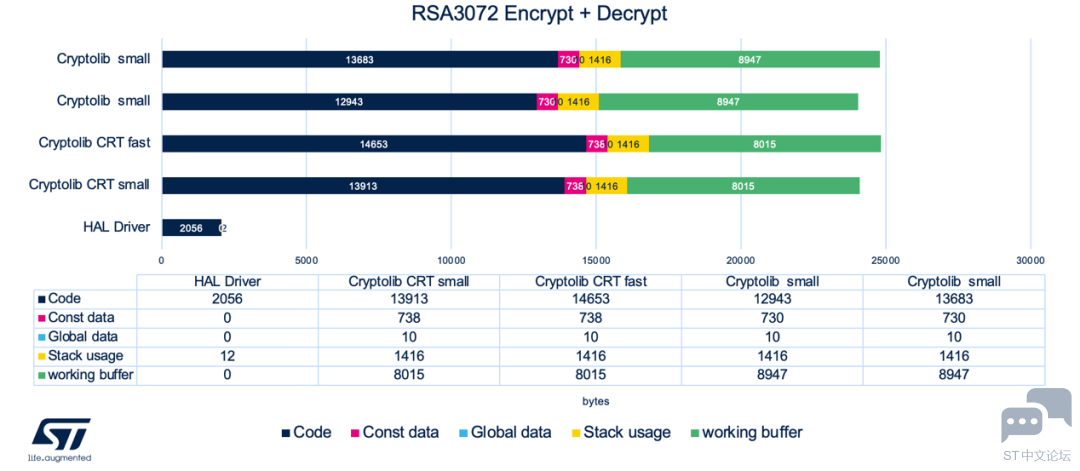

RSA加解密

ECC签名验签

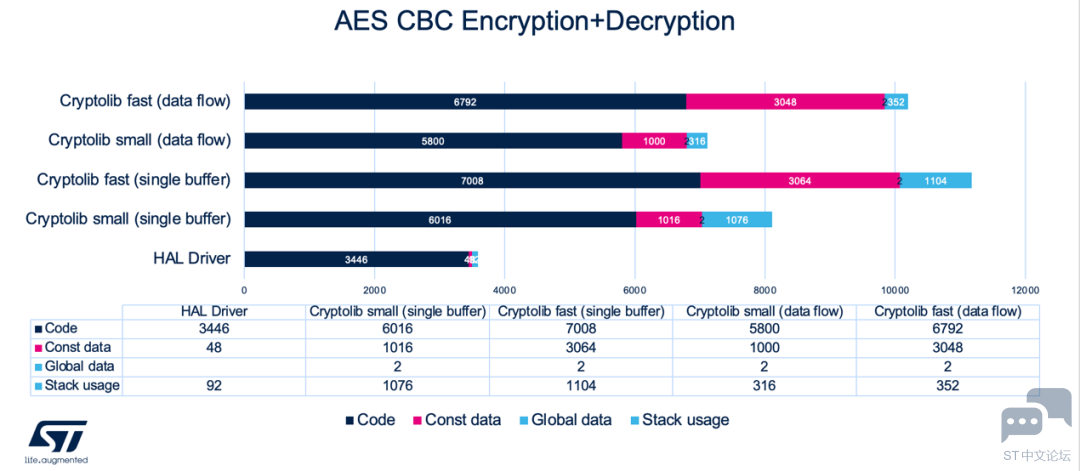

✦ 存储空间占用情况 存储空间的占用和选择的编译器、编译器版本、编译选项和配置等很多因素有关,下面的数据仅供参考。Memory Footprint HAL + HW vs. Cryptolib SW

* N, t: u# o5 r% e; q5 ]6 v: N

4 Y8 R' b- R0 t$ G$ A 硬件加解密引擎优势总结 综上所述,硬件加解密引擎具有更高安全性、更高性能、更低功耗和更少的系统资源需求。 ✦ 更高安全性

✦ 更高性能

✦ 更低功耗

✦ 更少系统资源需求

|

【2025·STM32峰会】GUI解决方案实训分享1-对LVGL咖啡机例程的牛刀小试以及问题排查

OpenBLT移植到STM32F405开发板

为什么要先开启STM32外设时钟?

【STM32MP157】从ST官方例程中分析RPMsg-TTY/SDB核间通信的使用方法

【经验分享】STM32实例-RTC实时时钟实验④-获取RTC时间函数与中断服务函数

STM32 以太网 MAC Loopback 的实现

STM32功能安全设计包,助力产品功能安全认证

基于STM32启动过程startup_xxxx.s文件经验分享

HRTIM 指南

ST 微控制器电磁兼容性 (EMC) 设计指南

微信公众号

微信公众号

手机版

手机版