.png) STMCU小助手

发布时间:2022-7-21 14:31

STMCU小助手

发布时间:2022-7-21 14:31

|

前言 本应用笔记对如何使用 STM32F2xx 和 STM32F4xx 系列直接存储器访问控制器 (DMA)进行了说明。STM32F2xx/F4xx DMA 控制器所具有的系统架构、多层总线矩阵和存储系统等,使其能够为应用提供很高的数据带宽,让用户可以开发出响应迅速的应用软件。 本应用笔记还提供了一些使用DMA的技巧,以便开发者能够充分利用STM32F2和STM32F4DMA 的特性来为不同的外设和子系统的 DMA 请求保证足够快的响应时间。 本文档中,使用 "STM32F2/F4 设备 " 代替 STM32F2xx 和 STM32F4xx,使用 “DMA” 代替DMA 控制器。 本应用笔记适用于表 1 中所列产品

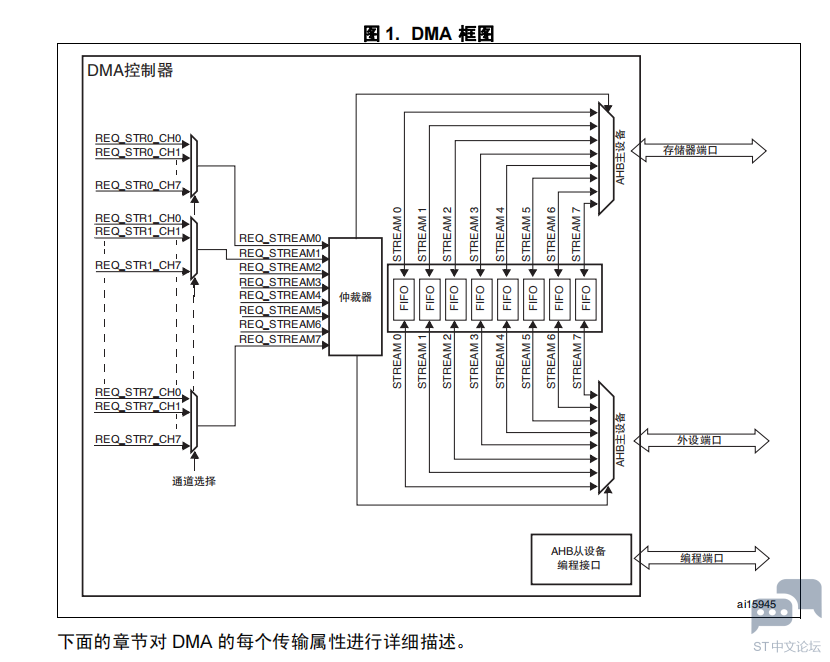

1 DMA 控制器说明 DMA 是一种 AMBA 先进高性能总线 (AHB)模块,它具有三个 AHB 端口:1 个用于 DMA编程的从端口和 2 个允许 DMA 在从模块之间进行数据传输的主端口(外设和存储器端口)。 DMA 使得数据传输在后台进行,而无需 Cortex-Mx 处理器干预。在数据传输过程中,主处理器能够执行其他任务,仅当需要处理一个完整数据块时才会被中断。 可以在不显著影响系统性能的情况下进行大量数据的传输。DMA 主要用于实现不同外设模块的集中数据缓冲存储 (通常在 SRAM 中)。在分布式方案中,每个外设均需实现其各自的本地数据存储,该解决方案从硅片面积的使用和功耗方面来说是比较便宜的。 STM32F2/F4 DMA 控制器充分利用了 Cortex-Mx 哈佛结构和多层总线系统的优势,保证了DMA 传输和 CPU 中断响应的及时性。 1.1 DMA 传输属性 DMA 传输的属性如下: • DMA 数据流 / 通道 • 数据流优先级 • 源和目标地址 • 传输模式 • 传输数据量大小 (仅当 DMA 为流量控制器时) • 源 / 目标地址递增或非增 • 源和目标数据宽度 • 传输类型 • FIFO 模式 • 源 / 目标批量传输数据量大小 • 双缓冲区模式 • 流控 STM32F2/F4 器件集成了 2 个 DMA 控制器,每个 DMA 有两个端口,一个外设端口和一个存储器端口,它们可以同时工作。 图 1 显示了 DMA 框图。

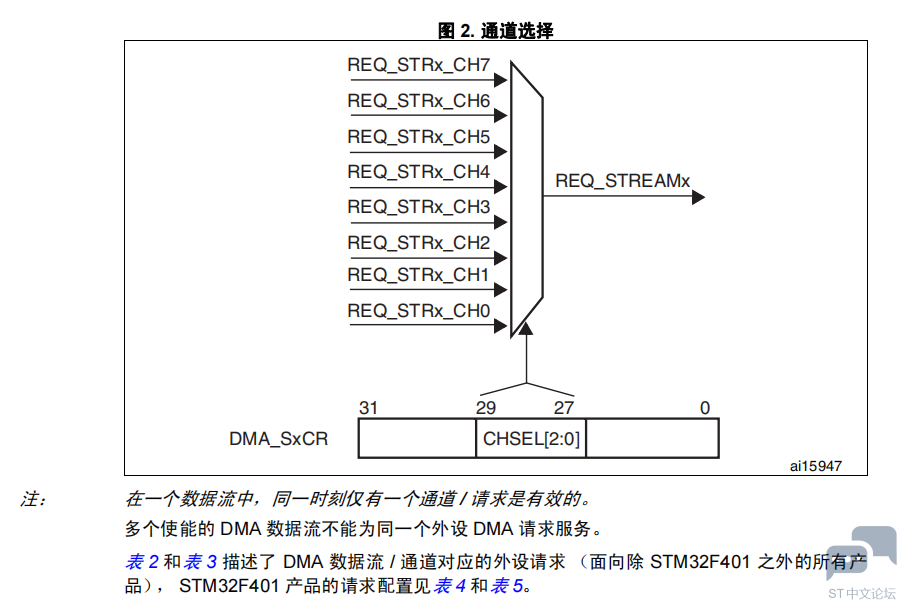

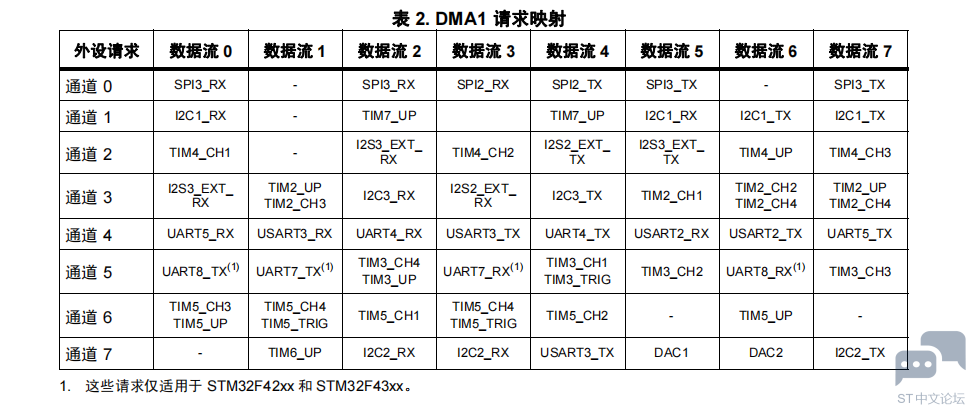

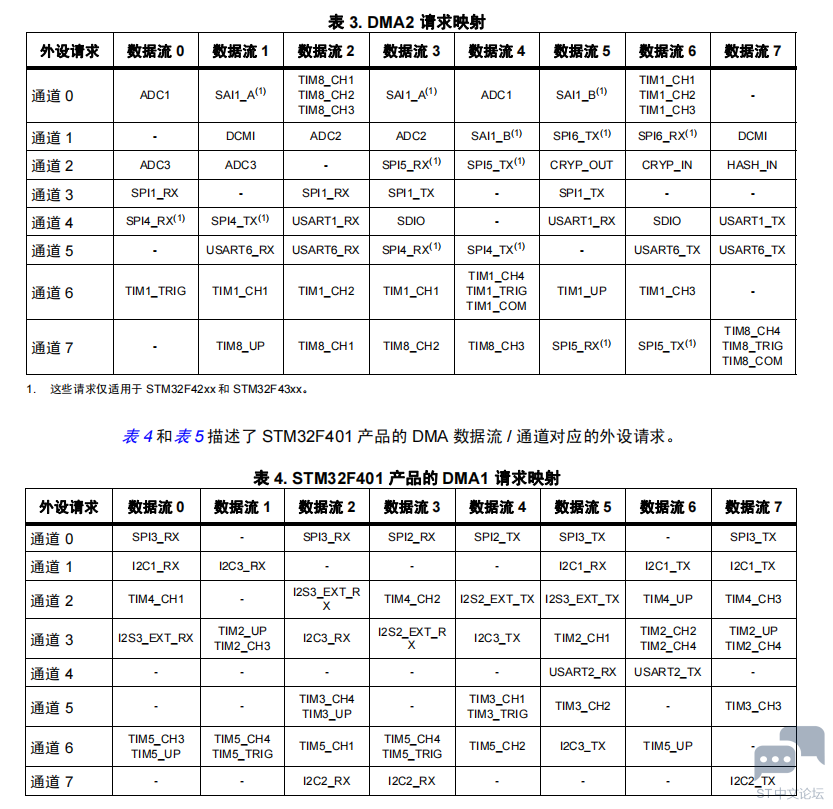

1.1.1 DMA 数据流 / 通道 STM32F2/F4 器件集成了 2 个 DMA 控制器,提供了共计多达 16 个数据流 (每个控制器 8个),每个数据流都可用来处理来自一个或多个外设的存储器访问请求。 每个数据流共有多达 8 个可选通道(请求), 可由软件配置,允许多个外设启动 DMA 请求。 图 2 描述了某个特定数据流的通道选择。

STM32F2/F4 DMA 请求映射经过了精心设计,软件应用可以更加灵活地为关联的外设请求配置 DMA 传输通道,并且通过复用相应的 DMA 数据流和通道可覆盖大部分应用。 1.1.2 数据流优先级 每个 DMA 端口都有一个仲裁器来处理 DMA 数据流之间的优先级。数据流优先级可由软件配置(共有 4 个软件级别)。如果两个或更多的 DMA 数据流具有同样的软件优先级别,则使用硬件优先级 (数据流 0 比数据流 1 优先级高,以此类推)。 1.1.3 源和目标地址 DMA 传输由源地址和目标地址决定。源和目标 (地址)均应当在 AHB 或 APB 存储范围之内,并且与传输宽度保持一致。 1.1.4 传输模式 DMA 能够实现 3 种不同的传输模式: • 外设到存储器, • 存储器到外设, • 存储器到存储器 (仅 DMA2 能够实现该传输,在这种模式下,禁用循环和直接模式。) 1.1.5 传输数据量大小 仅当 DMA 为流量控制器时,才必须定义其传输数据量大小。实际上,传输数据量值决定了从数据源到目标传输的数据总量。 传输数据量大小由 DMA_SxNDTR 寄存器值和外设端的数据传输宽度决定。随着已接收的请求 (批量或单个的),传输数据总量减少,减少量为已传输数据量。 完整版请查看:附件 |

DM00046011_ZHV1.pdf

下载1.47 MB, 下载次数: 3

微信公众号

微信公众号

手机版

手机版