.png) STMCU小助手

发布时间:2022-10-31 23:35

STMCU小助手

发布时间:2022-10-31 23:35

图1 STM32F103RCT6实物 既然是“STM32开发必备知识“就请把基础夯实,如同写“FPGA基础知识”笔者也把常用IP核的仿真、模块划分等知识说明清楚,用了4年STM32芯片个人觉得,有几样东西是在做STM32开发前所必须要掌握的,学习任何知识都有过程,需要循循渐进把握住规律,才可能层层深入。而对于STM32开发:STM32的中断系统、时钟分配、定时器、ADC模数转换、DMA数据搬运、GPIO EXTI中断类型等这些请必须掌握,然后再把C语言的数据结构、函数指针捡起来,相信这些大家在上学的时候多多少少都有学习,这些都搞明白了再动手实践“STM32 10个项目”,这10个项目的选取也费尽心思,一方面参考了市面经典的开发板例程,另一方面更站在了4年产品研发的角度,笔者会把项目的源码开源方便大家后期学习实践。 什么叫做中断,如图2所示是一个日常生活中的中断,比如现在大家在看电视,然后这时候电话响了,我们要去接电话显然电话比看电视这件事紧急,接完电话这时候又要去取快递了,下楼取快递以后再回来继续看电视,那类似的什么是处理器中的中断呢? 在处理器中,中断是一个过程,即CPU在正常执行程序的过程中,遇到外部/内部的紧急事件需要处理,暂时中止当前程序的执行,转而去为处理紧急的事件,待处理完毕后再返回被打断的程序处继续往下执行。中断在计算机多任务处理,尤其是即时系统中尤为重要,如uCOS和FreeRTOS等。

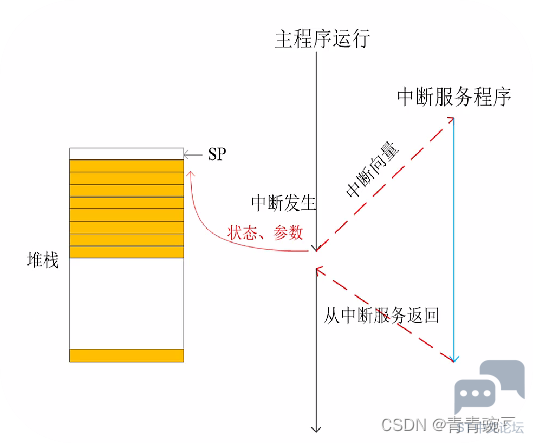

图2 日常生活中的中断 如图3所示是STM32中断处理过程,很多培训机构或者网络教程会说得很复杂繁琐,在这里其实大家只需要记住CPU进入中断前要做什么,退出中断后要做什么即可。 进入中断前 1. 处理器自动保存现场到堆栈里 2. {PC, xPSR, R0-R3, R12, LR} 3. 一旦入栈结束,ISR便可开始执行 4. 晚到的中断会重新取ISR地址,但无需再次保存现场 退出中断后 1. 中断前的现场被自动从堆栈中恢复 2. 一旦出栈完成,继续执行被中断打断的指令 3. 出栈的过程也可被打断,使得随时可以响应新的中断, 而不再进行 4. 现场保存

图3 STM32中断处理过程 如图4所示以STM32F0为例,是STM32F0中断的体系结构,在这里以Cortex-M0内部产生的中断,通常叫做“异常”,而外设产生的中断,通常就叫做“中断”,注意到对于外部产生的中断不管是串口、定时器、IIC还是EXTI GPIO都由一个叫做NVIC即“嵌套向量中断控制器”来管理,NVIC的主要功能可以概括为:1. 中断管理;2.支持异常及中断向量化处理;3.支持嵌套中断。

图4 STM32F0中断的体系结构 1. 中断管理 Cortex-M0处理器中,每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以电平的形式的,也可以是脉冲形式的,这样中断控制器就可以处理任何中断源,如图5所示是Cortex-M0处理器中的NVIC常用寄存器地址,例如ISER表示对一个中断的使能、ICER表示对一个中断的禁止、ISPR表示一个挂起寄存器的设置、ICPR表示清除挂起寄存器、IPR0-7表示对一个中断源优先级的配置。

图5 Cortex-M0处理器的NVIC常用寄存器地址 2.支持异常及中断向量化处理 如图6所示是Cortex-M0处理器的中断和异常向量表,Cortex-M0内核可以处理15个内部异常,和32个外部中断。STM32F051实际上只使用了6个内部异常和28个外部中断。当异常或中断发生时,处理器会把PC设置为一个特定地址,这一地址就称为异常向量。每一类异常源都对应一个特定的入口地址,这些地址按照优先级排列以后就组成一张异常向量表。 向量化处理中断的好处 统的处理方式需要软件去完成。采用向量表处理异常,M0处理器会从存储器的向量表中,自动定位异常的程序入口,从发生异常到异常的处理中间的时间被缩减。

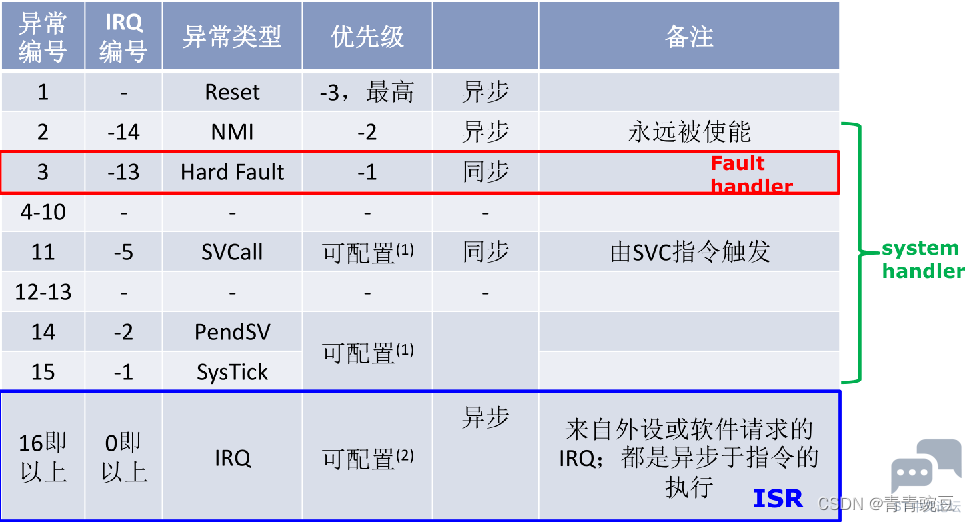

图6 Cortex-M0处理器的中断和异常向量表 中断和异常的区别: 中断是微处理器外部发送的,通过中断通道送入处理器内部,一般是硬件引起的,比如串口接收中断,而异常通常是微处理器内部发生的,大多是软件引起的,比如除法出错异常,特权调用异常等待。不管是中断还是异常,微处理器通常都有相应的中断/异常服务程序,如图7所示是Cortex-M0处理器的NVIC中断编号,大家可以看到1-15即Cortex-M0内部的异常,16以上为外设的中断。

图7 Cortex-M0处理器的NVIC中断编号 3.支持嵌套中断 如图8所示是Cortex-M0处理器的优先级配置STM32F0中断的优先级,不同优先级的中断同时发生,优先处理优先级编号较小的那个同样优先级的中断同时发生,中断向量号较小的那个优先响应: 3个固定的优先级,都是负值不能改变 ;4个可编程优先级,用两个bit位表示,00,01,10,11 ;优先级越小优先级越高

图8 Cortex-M0处理器的优先级配置 ———————————————— 版权声明:青青豌豆 |

STM32中断响应延迟优化:从NVIC配置到DMA加速的极致性能调优

基于STM32串口中断之缓存区溢出卡死经验分享

基于STM32数组越界异常中断经验分享

基于STM32之数组越界异常中断经验分享

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32的定时器不按设定超时产生中断

基于STM32利用TIMER事件和栈帧体验中断响应经验分享

基于STM32外部中断原理和配置代码经验分享

基于stm32定时器定时中断经验分享

微信公众号

微信公众号

手机版

手机版