.png) STMCU小助手

发布时间:2022-11-21 17:00

STMCU小助手

发布时间:2022-11-21 17:00

|

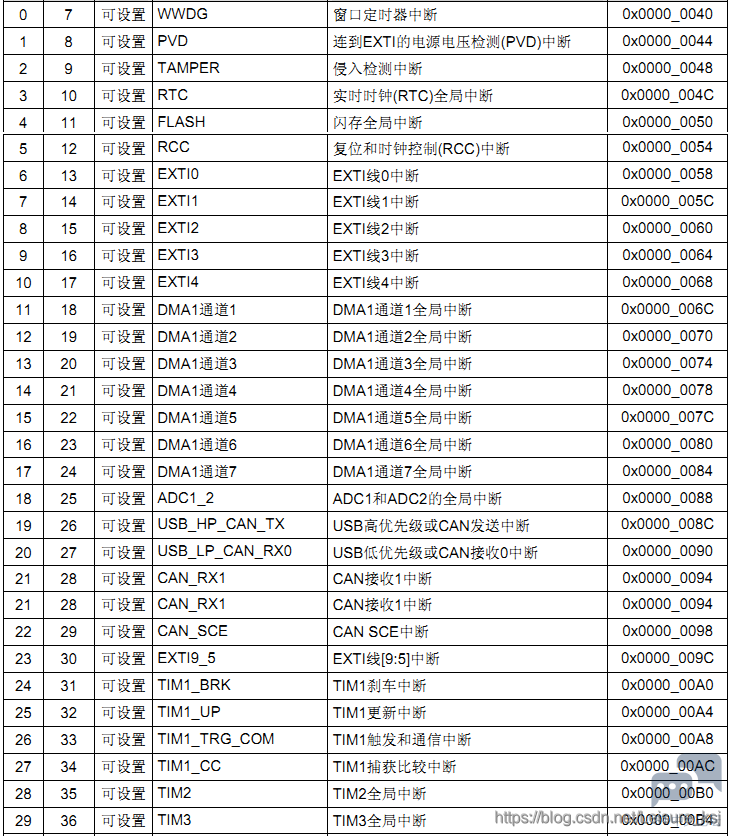

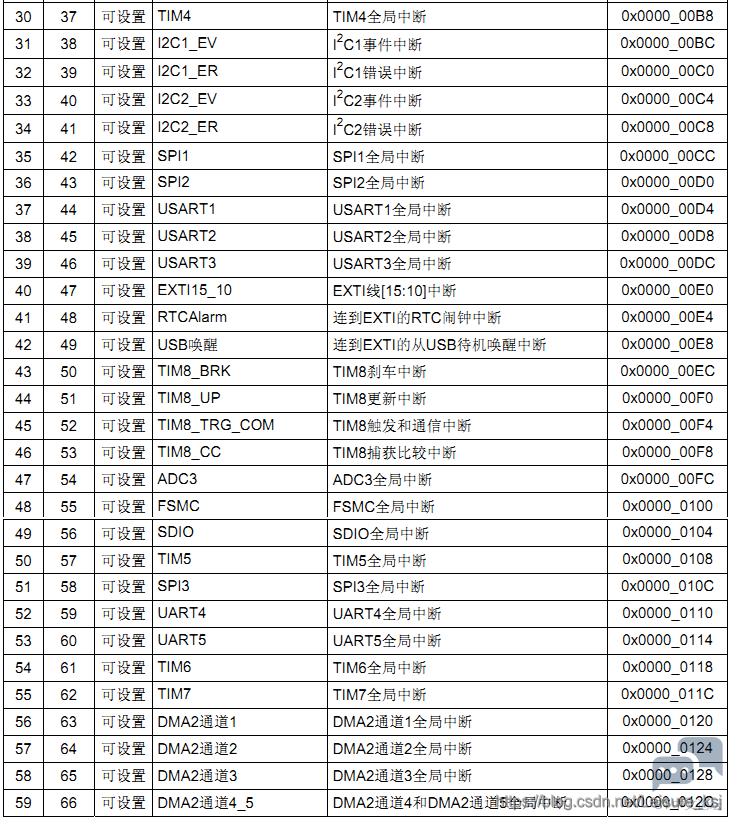

主要内容: 1) NVIC中断优先级分组; 2) NVIC中断优先级设置。 1. NVIC中断优先级分组 1.1 CM3内核支持256个中断,其中包含16个内核中断和240个外部中断,并且具有256级的可编程中断设置; 1.2 STM32并没有使用CM3内核的全部东西,只用了它的一部分; 1.3 STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程的中断优先级; 1.4 STM32F103系列上面,又只有60个可屏蔽中断(在107系列才有68个)。 2. NVIC中断优先级向量表(STM32F10xx产品(非互联型))

3. NVIC中断优先级管理方法 3.1 对STM32中断进行分组,组0~4。同时,对每个中断设置一个抢占优先级和一个响应优先级值; 3.2 分组配置是在寄存器SCB->AIRCR中配置:

3.3 分组配置是在寄存器SCB->AIRCR中配置。 4. 抢占优先级和响应优先级区别 4.1 高优先级(值越小越高)的抢占优先级是可以打断正在进行的低抢占优先级中断的; 4.2 抢占优先级相同的中断,高响应优先级不可以打断低响应优先级的中断; 4.3 抢占优先级相同的中断,当两个中断同时发生的情况下,高响应优先级先执行; 4.4 如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行。 举例: 假定设置中断优先级组为2, 设置中断3(RTC中断)的抢占优先级为2,响应优先级为1; 设置中断6(外部中断0)的抢占优先级为3,响应优先级为0; 设置中断7(外部中断1)的抢占优先级为2,响应优先级为0。 那么这3个中断的优先级顺序为:中断7>中断3>中断6。 **备注:**一般情况下,系统代码执行过程中,只设置一次中断优先级分组,比如分组2,设置好分组之后一般不会再改变分组。随意改变分组会导致中断管理混乱,程序出现意想不到的执行结果。 5. 中断优先级分组函数:

6. MDK中NVIC寄存器结构体

7. 每个中断的优先级设置 1.1 中断优先级控制的寄存器组:IP[240] (全称:Interrupt Priority Registers) 240个8位寄存器,每个中断使用一个寄存器来确定优先级。STM32F10x系列一共60个可屏蔽中断,使用IP[59]~IP[0]。每个IP寄存器的高4位用来设置抢占和响应优先级(根据分组),低4位没有用到。 相关函数:

7.2 中断使能寄存器组:ISER[8] (作用:用来使能中断) 32位寄存器,每个位控制一个中断的使能。STM32F10x只有60个可屏蔽中断,所以只使用了其中的ISER[0]和ISER[1]。ISER[0]的bit0bit31分别对应中断031。ISER[1]的bit027对应中断3259。 相关函数:

7.3 中断失能寄存器组:ICER[8] (作用:用来失能中断) 32位寄存器,每个位控制一个中断的失能。STM32F10x只有60个可屏蔽中断,所以只使用了其中的ICER[0]和ICER[1]。ICER[0]的bit0bit31分别对应中断031。ICER[1]的bit027对应中断3259。 相关函数:

7.4 中断挂起控制寄存器组:ISPR[8] (作用:用来挂起中断) 7.5 中断解挂控制寄存器组:ICPR[8] (作用:用来解挂中断)

7.6 中断激活标志位寄存器组:IABR [8] (作用:只读,通过它可以知道当前在执行的中断是哪一个) 如果对应位为1,说明该中断正在执行。 相关函数:

8. 中断参数初始化函数解读

9. 中断优先级设置步骤 9.1 系统运行后先设置中断优先级分组;

9.2 针对每个中断,设置对应的抢占优先级和响应优先级;

9.3 如果需要挂起/解挂,查看中断当前激活状态,分别调用相关函数即可。 ———————————————— 版权声明:天亮继续睡 |

STM32中断响应延迟优化:从NVIC配置到DMA加速的极致性能调优

基于STM32串口中断之缓存区溢出卡死经验分享

基于STM32数组越界异常中断经验分享

基于STM32之数组越界异常中断经验分享

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32的定时器不按设定超时产生中断

基于STM32利用TIMER事件和栈帧体验中断响应经验分享

基于STM32外部中断原理和配置代码经验分享

基于stm32定时器定时中断经验分享

微信公众号

微信公众号

手机版

手机版