|

原理讲解

% M4 [5 s* g( l! a% l芯片讲解

. z4 s4 k( a1 ^: SSTM32F103芯片 b* A$ s" a. d' e5 X

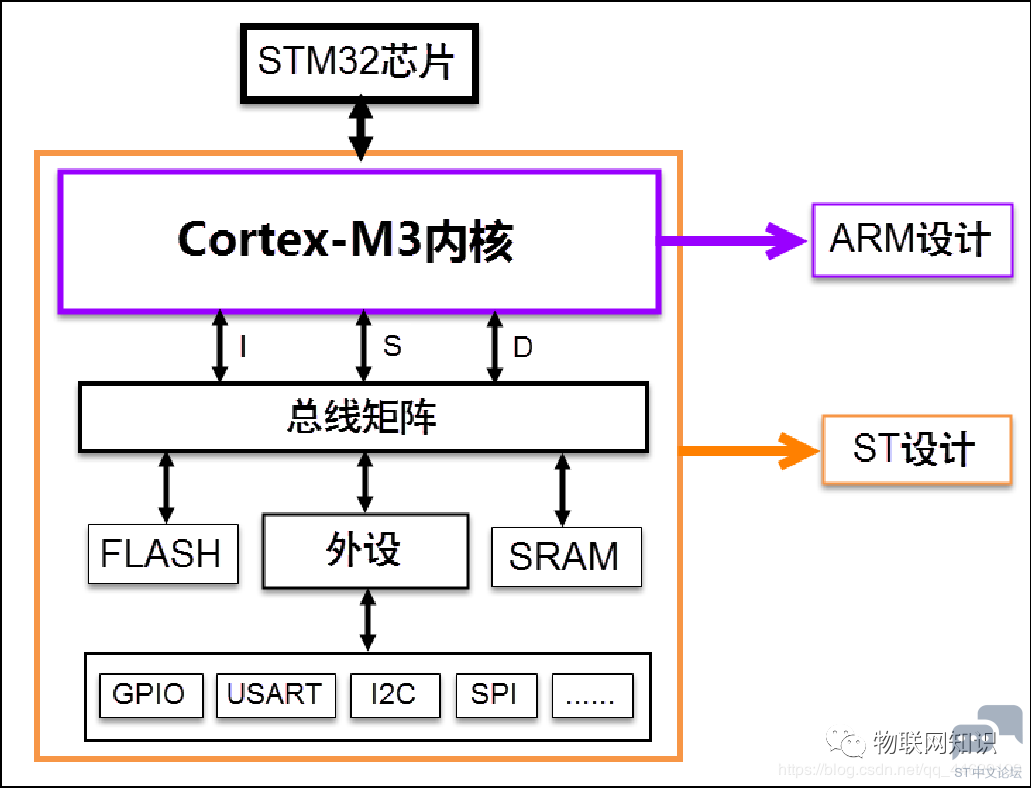

我们看到的 STM32 芯片是已经封装好的成品,主要由内核和片上外设组成。若与电脑类比,内核与外设就如同电脑上的 CPU与主板、内存、显卡、硬盘的关系。

- V1 n6 \5 k" P% Z/ S+ uSTM32F103采用的是 Cortex-M3内核,内核即 CPU,由 ARM公司设计。ARM公司并不生产芯片,而是出售其芯片技术授权。芯片生产厂商(SOC)如 ST、TI、Freescale,负责在内核之外设计部件并生产整个芯片,这些内核之外的部件被称为核外外设或片上外设。如 GPIO、USART(串口)、I2C、SPI等都叫做片上外设。(采用野火官方的介绍)。

. z, g* U" H" u$ i3 ~6 P, @芯片(这里指内核,或者叫 CPU)和外设之间通过各种总线连接,其中驱动单元有 4个,被动单元也有 4 个。为了方便理解,我们都可以把驱动单元理解成是CPU 部分,被动单元都理解成外设。下面我们简单介绍下驱动单元和被动单元的各个部件。 ' V% A1 K" |! M3 D

ICode总线

' z9 H6 V& k2 H7 [! i0 U. G+ WICode 中的 I 表示 Instruction,即指令。我们写好的程序编译之后都是一条条指令,存放在 FLASH 中,内核要读取这些指令来执行程序就必须通过 ICode 总线,它几乎每时每刻都需要被使用,它是专门用来取指的。 : i4 [8 [% {. Y9 @4 s

驱动单元! w- n7 J7 k- G* E' c8 O' z

DCode 总线( T* _& I4 O* i

DCode 中的 D 表示 Data,即数据,那说明这条总线是用来取数的 。我们在写程序的时候,数据有常量和变量两种,常量就是固定不变的,用 C语言中的 const关键字修饰,是放到内部的 FLASH 当中的,变量是可变的,不管是全局变量还是局部变量都放在内部的SRAM。因为数据可以被 Dcode总线和 DMA总线访问,所以为了避免访问冲突,在取数的时候需要经过一个总线矩阵来仲裁,决定哪个总线在取数。 5 i& e; }1 Y6 E+ ]& s

系统总线' r) l, y4 f7 j

系统总线主要是访问外设的寄存器,我们通常说的寄存器编程,即读写寄存器都是通过这根系统总线来完成的。 2 k1 [9 L6 w2 Y& B4 S, K5 y! k

DMA 总线

& n) ]; g- p8 a4 J: QDMA 总线也主要是用来传输数据,这个数据可以是在某个外设的数据寄存器,可以在SRAM,可以在内部的 FLASH。因为数据可以被 Dcode 总线和 DMA 总线访问,所以为了避免访问冲突,在取数的时候需要经过一个总线矩阵来仲裁,决定哪个总线在取数。

. ]7 G* `' E5 b2 V1 |5 U9 V9 W+ t. _被动单元, p2 q. t0 ]. v) I: j

内部的闪存存储器

- I+ R" `5 ^& X& E2 ?% }+ _ f内部的闪存存储器即 FLASH,我们编写好的程序就放在这个地方。内核通过 ICode 总线来取里面的指令。8 V% i d3 A# ^

内部的 SRAM

: @9 ]; N+ ?; n7 Q2 }) f内部的 SRAM,即我们通常说的 RAM,程序的变量,堆栈等的开销都是基于内部的SRAM。内核通过DCode总线来访问它。

+ E# x: c! g% S1 h( I3 N4 rFSMC

3 B" Y- ~- ^% z7 ~FSMC 的英文全称是 Flexible static memory controller,叫灵活的静态的存储器控制器是 STM32F10xx 中一个很有特色的外设,通过 FSMC,我们可以扩展内存,如外部的SRAM,NANDFLASH 和 NORFLASH。但有一点我们要注意的是,FSMC 只能扩展静态的内存,即名称里面的 S:static,不能是动态的内存,比如 SDRAM就不能扩展。% y$ X) Y( @) a+ K

AHB 到 到 APB 的桥

' h( b; ]+ l+ b u p. n+ ?( D从 AHB 总线延伸出来的两条 APB2 和 APB1 总线,上面挂载着 STM32 各种各样的特色外设。我们经常说的GPIO、串口、I2C、SPI这些外设就挂载在这两条总线上,这个是我们学习 STM32 的重点,就是要学会编程这些外设去驱动外部的各种设备。

存储器映射/ U8 }0 u7 x; k; h4 V/ o& B

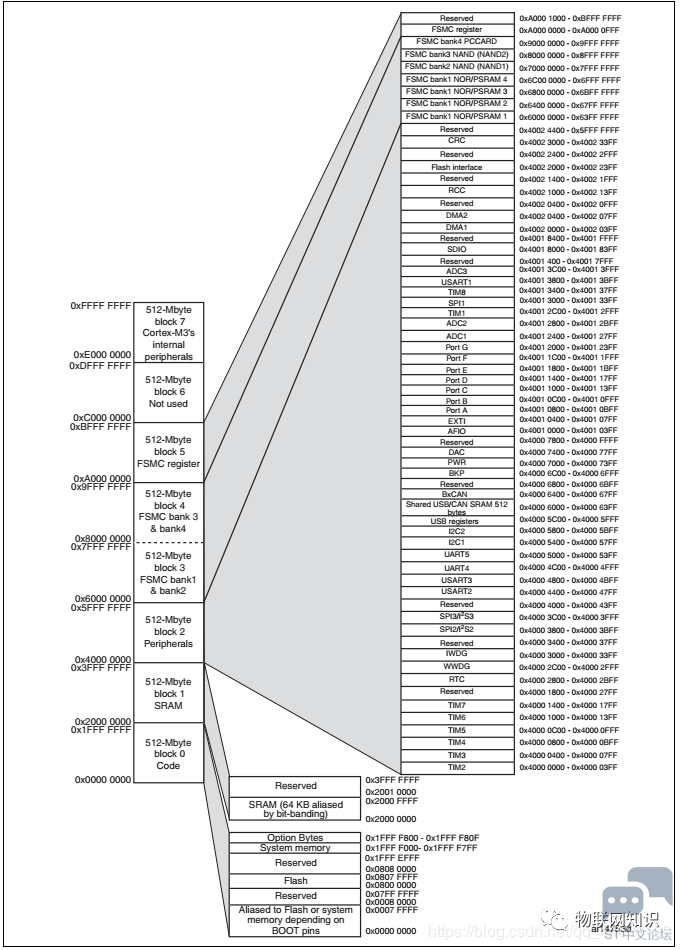

被控单元的FLASH,RAM,FSMC和AHB到APB的桥(即片上外设),这些功能部件共同排列在一个 4GB 的地址空间内。我们在编程的时候,可以通过他们的地址找到他们,然后来操作他们(通过 C 语言对它们进行数据的读和写)。3 C! O* K; M0 p* }0 \' o

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射。如果给存储器再分配一个地址就叫存储器重映射。

" o9 ]8 g6 i0 l- ]" p

0 D, u/ z/ c$ W2 U9 H' A5 R

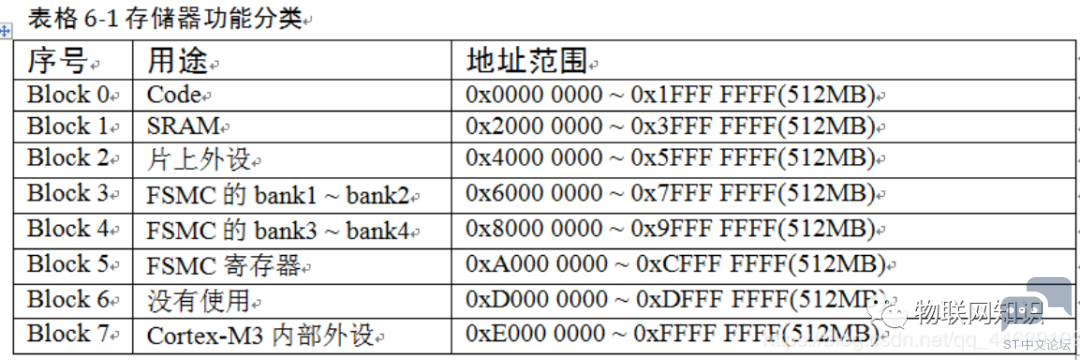

存储器区域功能划分

0 E3 t! n# n2 w2 N7 K3 I在这 4GB 的地址空间中,ARM 已经粗线条的平均分成了 8 个块,每块 512MB,每个块也都规定了用途,每个块的大小都有 512MB,显然这是非常大的,芯片厂商在每个块的范围内设计各具特色的外设时并不一定都用得完,都是只用了其中的一部分而已。

2 v5 i* e' w: l& Y9 s1 q1 u# Z i5 T

' Q" {/ K) }/ s4 E/ _7 ~% [- T

在这 8个Block里面,有 3个块非常重要,也是我们最关心的三个块。Block0用来设计成内部 FLASH,Block1 用来设计成内部 RAM,Block2 用来设计成片上的外设,下面我们简单的介绍下这三个 Block 里面的具体区域的功能划分。

: m+ j. d7 ~; s! t% g' v$ m3 g) c3 p

存储器 Block0 内部区域功能划分

# F' j7 H, B! A( CBlock0 主要用于设计片内的 FLASH,STM32F103ZET6和STM32F103VET6的 FLASH 都是 512KB,属于大容量。要在芯片内部集成更大的 FLASH或者 SRAM都意味着芯片成本的增加,往往片内集成的 FLASH都不会太大,ST能在追求性价比的同时做到512KB,实乃良心之举。 $ d% @: G+ O! _% c- j9 |8 N g7 L, B

存储器 Block1 内部区域功能划分

, w+ P; h5 Z2 g# L" a/ }Block1 用 于 设 计 片 内 的 SRAM 。 STM32F103ZET6 和STM32F103VET6的 SRAM 都是 64KB。

6 X0 b$ Y: |9 e k6 i存储器 Block2 内部区域功能划分1 F3 U: w! h# F [6 C6 y4 H

Block1 用 于 设 计 片 内 的 SRAM 。STM32F103ZET6 和STM32F103VET6的 SRAM 都是 64KB。

% A% x2 [8 ~. L/ [

寄存器映射

) V, F4 F' R% h' x s0 w我们知道,存储器本身没有地址,给存储器分配地址的过程叫存储器映射。/ d; X; D! Z {& e

在存储器 Block2这块区域,设计的是片上外设,它们以四个字节为一个单元,共 32bit,每一个单元对应不同的功能,当我们控制这些单元时就可以驱动外设工作。我们可以找到每个单元的起始地址,然后通过 C 语言指针的操作方式来访问这些单元,如果每次都是通过这种地址的方式来访问,不仅不好记忆还容易出错,这时我们可以根据每个单元功能的不同,以功能为名给这个内存单元取一个别名,这个别名就是我们经常说的寄存器,这个给已经分配好地址的有特定功能的内存单元取别名的过程就叫寄存器映射。9 A& \* e( Z3 f+ B _7 c0 F

比如,我们找到 GPIOB 端口的输出数据寄存器 ODR 的地址是 0x4001 0C0C(至于这个地址如何找到可以先跳过,后面我们会有详细的讲解),ODR 寄存器是 32bit,低 16bit有效,对应着 16 个外部 IO,写 0/1 对应的的 IO 则输出低/高电平。现在我们通过 C 语言指针的操作方式,让 GPIOB 的 16 个 IO都输出高电平。 - // GPIOB 端口全部输出 高电平

5 a+ @& e4 J" N2 Z5 { - *(unsigned int*)(0x4001 0C0C) = 0xFFFF;

0x4001 0C0C在我们看来是 GPIOB端口ODR的地址,但是在编译器看来,这只是一个普通的变量,是一个立即数,要想让编译器也认为是指针,我们得进行强制类型转换,把它转换成指针,即(unsigned int *)0x4001 0C0C,然后再对这个指针进行 * 操作。

3 ]5 u0 Y* Y; ^9 }! [刚刚我们说了,通过绝对地址访问内存单元不好记忆且容易出错,我们可以通过寄存器的方式来操作。 - // GPIOB 端口全部输出 高电平2 I! G' ?4 @: O$ W

- #define GPIOB_ODR (unsigned int*)(GPIOB_BASE+0x0C)

/ Y8 \$ b) _+ o7 ]/ A, j6 C1 W - * GPIOB_ODR = 0xFF;

为了方便操作,我们干脆把指针操作“*”也定义到寄存器别名里面。 - // GPIOB 端口全部输出 高电平

, U4 K" ^8 `7 Z2 [6 ]: ?, D - #define GPIOB_ODR *(unsigned int*)(GPIOB_BASE+0x0C)1 F+ c! \) f: ^$ \, S/ t/ C* ^6 ^: \

- GPIOB_ODR = 0xFF;

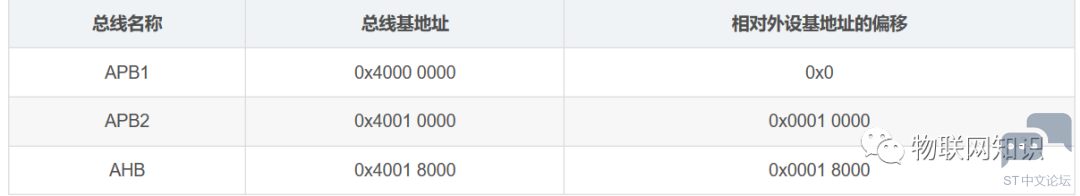

STM32的外设地址映射' k0 X) y( x+ |$ w9 k$ V

片上外设区分为三条总线,根据外设速度的不同,不同总线挂载着不同的外设,APB1挂载低速外设,APB2 和 AHB 挂载高速外设。相应总线的最低地址我们称为该总线的基地址,总线基地址也是挂载在该总线上的首个外设的地址。其中 APB1 总线的地址最低,片上外设从这里开始,也叫外设基地址。 4 P9 \* A8 u1 z4 [/ A! |1 u `

总线基地址: X0 ]) M# B. U; `! k

外设基地址

' J1 X& P- Q( _- o总线上挂载着各种外设,这些外设也有自己的地址范围,特定外设的首个地址称为“XX外设基地址”,也叫 XX外设的边界地址。具体有关 STM32F10xx外设的边界地址请参考《STM32F10xx 参考手册》的 2.3 小节的存储器映射的表 1:STM32F10xx 寄存器边界地址。' [1 G, R( F% K

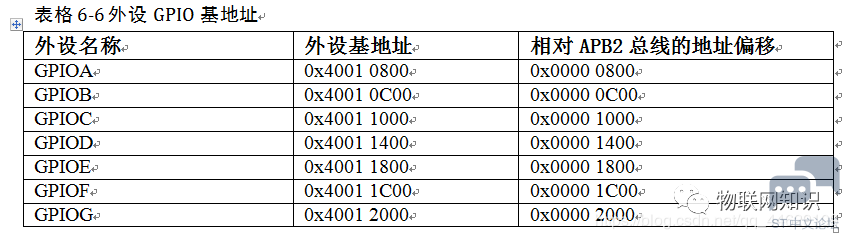

这里面我们以 GPIO 这个外设来讲解外设的基地址,GPIO 属于高速的外设 ,挂载到APB2总线上. + m6 ^: _# @) C! C+ n$ T: c( B

! S2 ?3 T$ Q0 E4 p; ]

外设寄存器

. a! h7 t; l: c* k在 XX 外设的地址范围内,分布着的就是该外设的寄存器。以 GPIO 外设为例,GPIO是通用输入输出端口的简称,简单来说就是 STM32 可控制的引脚,基本功能是控制引脚输出高电平或者低电平。最简单的应用就是把 GPIO 的引脚连接到 LED 灯的阴极,LED 灯的阳极接电源,然后通过 STM32控制该引脚的电平,从而实现控制 LED 灯的亮灭。

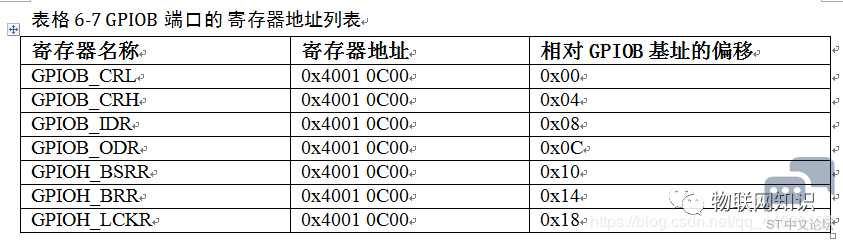

" V+ |' T' n: `, V0 t/ Q" G! V& N8 p) MGPIO 有很多个寄存器,每一个都有特定的功能。每个寄存器为 32bit,占四个字节,在该外设的基地址上按照顺序排列,寄存器的位置都以相对该外设基地址的偏移地址来描述。这里我们以 GPIOB 端口为例,来说明 GPIO 都有哪些寄存器.

1 w: T' a+ k m0 R$ | O) w

W5 t2 P! I4 i/ u, s2 |* t

有关外设的寄存器说明可参考《STM32F10xx 参考手册》中具体章节的寄存器描述部分,在编程的时候我们需要反复的查阅外设的寄存器说明。) c4 O A) V- [5 d$ s

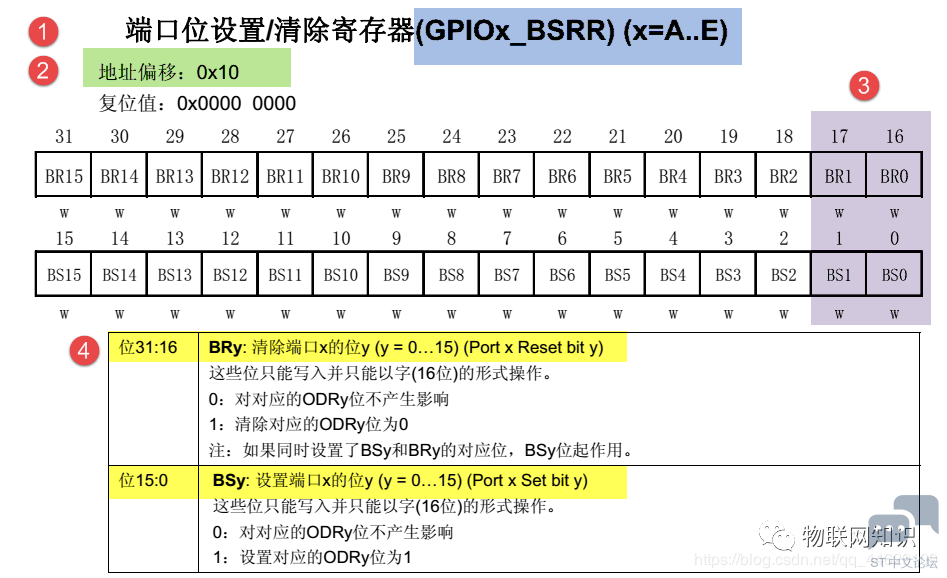

这里我们以“GPIO 端口置位/复位寄存器”为例,教大家如何理解寄存器的说明.

& x! h; v# X- {# R

6 I5 T% o" A6 i. N& V/ z9 `①名称# G2 b% a3 k) k/ A* x [: g

寄存器说明中首先列出了该寄存器中的名称,“(GPIOx_BSRR)(x=A…E)”这段的意思是该寄存器名为“GPIOx_BSRR”其中的“x”可以为 A-E,也就是说这个寄存器说明适用于 GPIOA、GPIOB至 GPIOE,这些 GPIO端口都有这样的一个寄存器。

+ |1 x, [' \, O# W7 Y$ z4 b1 ~6 K②偏移地址

, k) N$ v# O- ^* n5 G6 J0 a偏移地址是指本寄存器相对于这个外设的基地址的偏移。本寄存器的偏移地址是 0x18,从参考手册中我们可以查到 GPIOA外设的基地址为 0x4001 0800 ,我们就可以算出 GPIOA的这个 GPIOA_BSRR 寄存器的地址为:0x4001 0800+0x18 ;同理,由于 GPIOB 的外设基地址为 0x4001 0C00,可算出 GPIOB_BSRR 寄存器的地址为:0x4001 0C00+0x18 。其他GPIO端口以此类推即可。

: B% e9 f( H4 I③寄存器位表

4 s) p" r8 T) O, l紧接着的是本寄存器的位表,表中列出它的 0-31 位的名称及权限。表上方的数字为位编号,中间为位名称,最下方为读写权限,其中w表示只写,r表示只读,rw表示可读写。本寄存器中的位权限都是 w,所以只能写,如果读本寄存器,是无法保证读取到它真正内容的。而有的寄存器位只读,一般是用于表示 STM32 外设的某种工作状态的,由 STM32硬件自动更改,程序通过读取那些寄存器位来判断外设的工作状态。

- o% Q J" C: `5 u: f1 s- w④位功能说明- B8 \. d1 s8 j- E" _

位功能是寄存器说明中最重要的部分,它详细介绍了寄存器每一个位的功能。例如本寄存器中有两种寄存器位,分别为 BRy及 BSy,其中的 y数值可以是 0-15,这里的 0-15表示端口的引脚号,如 BR0、BS0 用于控制 GPIOx的第 0 个引脚,若 x 表示 GPIOA,那就是控制 GPIOA的第 0 引脚,而 BR1、BS1就是控制 GPIOA 第 1个引脚。, C2 f, ~6 Z! `$ `4 q! f" U) ~

其中 BRy 引脚的说明是“0:不会对相应的 ODRx 位执行任何操作;1:对相应 ODRx位进行复位”。这里的“复位”是将该位设置为 0 的意思,而“置位”表示将该位设置为1;说明中的 ODRx是另一个寄存器的寄存器位,我们只需要知道 ODRx位为 1的时候,对应的引脚 x 输出高电平,为 0 的时候对应的引脚输出低电平即可(感兴趣的读者可以查询该寄存器 GPIOx_ODR 的说明了解)。所以,如果对 BR0 写入“1”的话,那么 GPIOx 的第 0: U# u, q* k' q. q/ j3 r

个引脚就会输出“低电平”,但是对 BR0 写入“0”的话,却不会影响 ODR0 位,所以引脚电平不会改变。要想该引脚输出“高电平”,就需要对“BS0”位写入“1”,寄存器位BSy与 BRy是相反的操作。 操作实例

. e, F1 Z; r0 k, K. |0 OC语言对寄存器的封装, y1 c! b; g; [8 [

以上所有的关于存储器映射的内容,最终都是为大家更好地理解如何用 C 语言控制读写外设寄存器做准备,此处是本章的重点内容。

2 h/ t9 L; h7 j' ]5 o2 ~0 g' ~封装总线和外设基地址

' K2 W: E3 a- q3 \8 G- ^9 ?在编程上为了方便理解和记忆,我们把总线基地址和外设基地址都以相应的宏定义起来,总线或者外设都以他们的名字作为宏名。 - /* 外设基地址 */; Y. E/ U0 Y0 Q- B7 M

- #define PERIPH_BASE ((unsigned int)0x40000000); e* h" \. D2 j3 Y t- U9 ~4 `

- /* 总线基地址 */

/ |: C0 \* b3 L5 F5 p; ` - #define APB1PERIPH_BASE PERIPH_BASE

5 E% ~% T% C6 s* Y- t4 s5 ` - #define APB2PERIPH_BASE (PERIPH_BASE + 0x10000)+ L; p- q' @$ o) I( a( S$ I- X

- #define AHBPERIPH_BASE (PERIPH_BASE + 0x20000)9 v- L! Y4 h# r6 K3 L+ n1 |

- /* GPIO 外设基地址 */ A2 o* x1 F- q# g4 c8 r

- #define GPIOA_BASE (APB2PERIPH_BASE + 0x0800)

) u! a3 n3 n! z6 J - #define GPIOB_BASE (APB2PERIPH_BASE + 0x0C00)! d& r( L" X5 A7 x2 e; V/ ]

- #define GPIOC_BASE (APB2PERIPH_BASE + 0x1000)

- W% I& y4 j8 W3 z. x - #define GPIOD_BASE (APB2PERIPH_BASE + 0x1400)7 K# M6 b0 ]7 q& L3 b

- #define GPIOE_BASE (APB2PERIPH_BASE + 0x1800)

. f$ C- \( Y& o& V) Q" o! T$ G- q - #define GPIOF_BASE (APB2PERIPH_BASE + 0x1C00)3 F: ]7 I6 b2 h; f

- #define GPIOG_BASE (APB2PERIPH_BASE + 0x2000)* b# Y# e @; d: _& k( [1 I( D

- /* 寄存器基地址,以 GPIOB 为例 */

) s; R5 o1 K% F' U2 Z) z8 j - #define GPIOA_CRL *(unsigned int*)(GPIOA_BASE+0x00)

% N* [' J9 L# x$ K# h8 u! P - #define GPIOA_CRH *(unsigned int*)(GPIOA_BASE+0x04)! R! Z5 r5 c- C$ J. O8 w1 I- J

- #define GPIOA_IDR *(unsigned int*)(GPIOA_BASE+0x08)+ I$ K8 g) P/ m0 Q+ E; X: T

- #define GPIOA_ODR *(unsigned int*)(GPIOA_BASE+0x0C), ]- K! H3 ~! [( A7 p% E

- #define GPIOA_BSRR *(unsigned int*)(GPIOA_BASE+0x10)

2 M! e$ W2 g" t$ o" `6 A - #define GPIOA_BRR *(unsigned int*)(GPIOA_BASE+0x14)9 x5 `- R5 d8 v3 p' Z1 v) x

- #define GPIOA_LCKR *(unsigned int*)(GPIOA_BASE+0x18)

' A" w) A# R2 J+ p8 [5 H

" K. T7 a* F4 }+ |- #define GPIOB_CRL *(unsigned int*)(GPIOB_BASE+0x00)

9 z/ K! Y, b0 s( ?. o1 z) b9 W4 S - #define GPIOB_CRH *(unsigned int*)(GPIOB_BASE+0x04)

- S' |8 h# z. I: M( X7 [* m - #define GPIOB_IDR *(unsigned int*)(GPIOB_BASE+0x08)% _- k; i4 M* C/ r

- #define GPIOB_ODR *(unsigned int*)(GPIOB_BASE+0x0C)" _9 Z) M/ r0 ?! G* `9 W

- #define GPIOB_BSRR *(unsigned int*)(GPIOB_BASE+0x10), g1 y$ P/ N9 {) e

- #define GPIOB_BRR *(unsigned int*)(GPIOB_BASE+0x14)5 E) i' n' p# U$ ^+ v

- #define GPIOB_LCKR *(unsigned int*)(GPIOB_BASE+0x18) " r, D7 u7 t* h _4 r. o* L

* k" |& K" X+ y$ N* B, q- #define GPIOC_CRL *(unsigned int*)(GPIOC_BASE+0x00)

) ^9 \! i- f3 }- o8 p - #define GPIOC_CRH *(unsigned int*)(GPIOC_BASE+0x04)% O) ]) P2 s6 z |& s) }5 y

- #define GPIOC_IDR *(unsigned int*)(GPIOC_BASE+0x08)0 c+ H e5 e# I" t4 R% A8 u

- #define GPIOC_ODR *(unsigned int*)(GPIOC_BASE+0x0C)

6 O [5 ~: K6 L: W1 { - #define GPIOC_BSRR *(unsigned int*)(GPIOC_BASE+0x10)

- _( O" u# t2 W+ _3 e* l/ P' @ - #define GPIOC_BRR *(unsigned int*)(GPIOC_BASE+0x14)

- r0 m; K; C a5 L O/ D8 a - #define GPIOC_LCKR *(unsigned int*)(GPIOC_BASE+0x18) 0 M. |2 r' @0 @5 W& V9 n. k @ P

# { H/ s% N+ j! B/ V6 h- #define GPIOD_CRL *(unsigned int*)(GPIOD_BASE+0x00)" F: v' z' n. d% h$ H, S

- #define GPIOD_CRH *(unsigned int*)(GPIOD_BASE+0x04)

- R5 c4 Y0 z' N% `* \8 _$ w - #define GPIOD_IDR *(unsigned int*)(GPIOD_BASE+0x08)

- u3 R5 i. e B6 F" _5 e - #define GPIOD_ODR *(unsigned int*)(GPIOD_BASE+0x0C)

7 D: I! u$ ]$ m7 P$ ] - #define GPIOD_BSRR *(unsigned int*)(GPIOD_BASE+0x10)

4 [1 _2 w0 m" e - #define GPIOD_BRR *(unsigned int*)(GPIOD_BASE+0x14)# r# \, _ D! `5 a

- #define GPIOD_LCKR *(unsigned int*)(GPIOD_BASE+0x18)

4 H9 D( |9 q+ k! r. c -

9 F+ ^) t8 N. ?: e4 U - #define GPIOE_CRL *(unsigned int*)(GPIOE_BASE+0x00): K. g; h. L% Z4 v. d" |/ W1 K

- #define GPIOE_CRH *(unsigned int*)(GPIOE_BASE+0x04)

# t* k% [0 ?. {5 ^ s3 \- F - #define GPIOE_IDR *(unsigned int*)(GPIOE_BASE+0x08)9 x; j& R& H: _9 l0 M

- #define GPIOE_ODR *(unsigned int*)(GPIOE_BASE+0x0C)

9 X" z6 K1 ?, {! g& Y O0 w1 F - #define GPIOE_BSRR *(unsigned int*)(GPIOE_BASE+0x10)

5 o2 \% ]7 {, d. J% w/ k0 H5 p - #define GPIOE_BRR *(unsigned int*)(GPIOE_BASE+0x14)

" A s" s4 P; A, X - #define GPIOE_LCKR *(unsigned int*)(GPIOE_BASE+0x18)

+ i3 m6 r) {; H# G

, U# c5 S4 |* S& ]. ^' ^5 t首先定义了 “片上外设”基地址 PERIPH_BASE,接着在 PERIPH_BASE上加入各个总线的地址偏移,得到 APB1、APB2 总线的地址 APB1PERIPH_BASE、APB2PERIPH_BASE,在其之上加入外设地址的偏移,得到 GPIOA-G 的外设地址,最后在外设地址上加入各寄存器的地址偏移,得到特定寄存器的地址。一旦有了具体地址,就可以用指针读写。 - /* 控制 GPIOB 引脚 0 输出低电平(BSRR 寄存器的 BR0 置 1) */& J$ z T: e, E( v* U) }9 f3 _

- *(unsigned int *)GPIOB_BSRR = (0x01<<(16+0));

- [6 P2 Z6 O+ d - /* 控制 GPIOB 引脚 0 输出高电平(BSRR 寄存器的 BS0 置 1) */: _2 X' L9 a" v! h

- *(unsigned int *)GPIOB_BSRR = 0x01<<0;

: d+ |5 A) U. ?1 X% S6 x5 H3 H N6 y - unsigned int temp;

( n; R8 s- n1 m9 Y: B* T7 R! M - /* 读取 GPIOB 端口所有引脚的电平(读 IDR 寄存器) */9 e U! _: i3 C: c/ V0 s

- temp = *(unsigned int *)GPIOB_IDR;

该代码使用 (unsigned int *) 把 GPIOB_BSRR宏的数值强制转换成了地址,然后再用“ * ”号做取指针操作,对该地址的赋值,从而实现了写寄存器的功能。同样,读寄存器也是用取指针操作,把寄存器中的数据取到变量里,从而获取 STM32外设的状态。

" U+ U# V1 `$ \9 |/ A, a封装寄存器列表. e" D: e$ }9 H/ l; K" ~

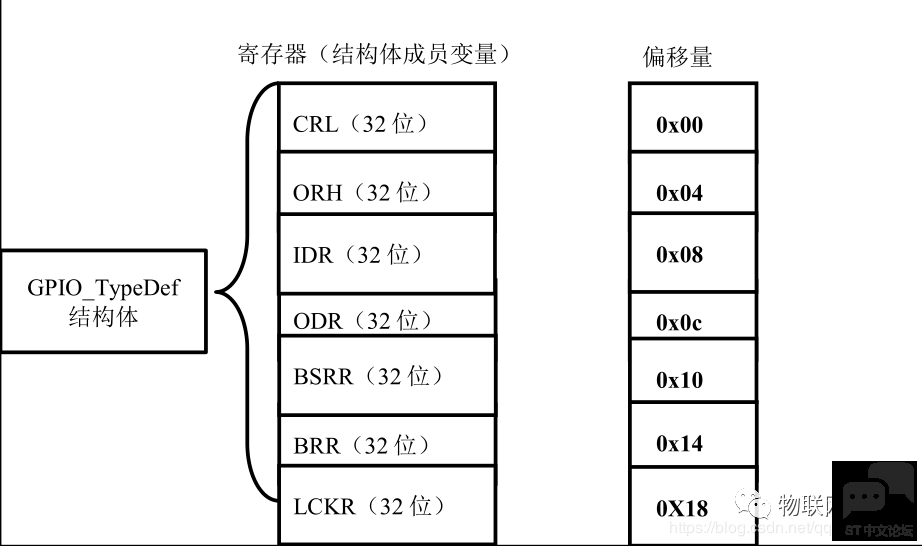

用上面的方法去定义地址,还是稍显繁琐,例如 GPIOA-GPIOE 都各有一组功能相同的寄存器,如 GPIOA_ODR/GPIOB_ODR/GPIOC_ODR 等等,它们只是地址不一样,但却要为每个寄存器都定义它的地址。为了更方便地访问寄存器,我们引入 C 语言中的结构体语法对寄存器进行封装。 - typedef unsigned int uint32_t; /*无符号 32 位变量*/) {4 _' o; d( A9 l9 D7 I, d, G

- typedef unsigned short int uint16_t; /*无符号 16 位变量*/0 y$ c" q9 i$ N6 a4 W% h6 A2 G

- /* GPIO 寄存器列表 */

- _5 l0 b: w) Q& i# G - typedef struct {6 R3 Y" W! g9 a1 b

- uint32_t CRL; /*GPIO 端口配置低寄存器 地址偏移: 0x00 */# S% S, V+ u4 I( z

- uint32_t CRH; /*GPIO 端口配置高寄存器 地址偏移: 0x04 */

( y( Q4 X6 @! C o W - uint32_t IDR; /*GPIO 数据输入寄存器 地址偏移: 0x08 */

+ v/ D/ ], c8 J1 _, |( U - uint32_t ODR; /*GPIO 数据输出寄存器 地址偏移: 0x0C */* z4 ~* B5 o: a6 O% ~, y

- uint32_t BSRR; /*GPIO 位设置/清除寄存器 地址偏移: 0x10 */

6 N& u6 E7 M9 N. v' n+ \ - uint32_t BRR; /*GPIO 端口位清除寄存器 地址偏移: 0x14 */

% g0 y6 A4 e& t/ k, F" f - uint16_t LCKR; /*GPIO 端口配置锁定寄存器 地址偏移: 0x18 */

7 _* [" Z1 ?" G& W' S - } GPIO_TypeDef;

这段代码用 typedef 关键字声明了名为 GPIO_TypeDef的结构体类型,结构体内有 7个成员变量,变量名正好对应寄存器的名字。C 语言的语法规定,结构体内变量的存储空间: ~2 Q8 l1 i3 w* X! x

是连续的,其中 32 位的变量占用 4个字节,16位的变量占用 2 个字节。 6 W+ j' { O* m- P

3 h4 ]6 b+ I6 o

也就是说,我们定义的这个 GPIO_TypeDef ,假如这个结构体的首地址为 0x4001 0C00(这也是第一个成员变量 CRL 的地址), 那么结构体中第二个成员变量 CRH 的地址即为/ }% M1 p0 X! ~) m; H' M' q) W. \* ^

0x4001 0C00 +0x04 ,加上的这个 0x04 ,正是代表 CRL所占用的 4个字节地址的偏移量,其它成员变量相对于结构体首地址的偏移,在上述代码右侧注释已给。

) J9 K# A' j: N4 {# H# e# ?7 ]8 W这样的地址偏移与 STM32 GPIO 外设定义的寄存器地址偏移一一对应,只要给结构体设置好首地址,就能把结构体内成员的地址确定下来,然后就能以结构体的形式访问寄存器。 - GPIO_TypeDef * GPIOx; //定义一个 GPIO_TypeDef 型结构体指针 GPIOx

- ~- D z5 O6 L9 W, A7 ]- |0 ]( Q/ k - GPIOx = GPIOB_BASE; //把指针地址设置为宏 GPIOH_BASE 地址

- c( K9 r1 r- K6 s$ v - GPIOx->IDR = 0xFFFF;

7 S- \9 j9 j6 O& x3 ~! N - GPIOx->ODR = 0xFFFF;3 C9 j5 [ T8 {( a) o1 g) Z: p& P2 H

- int32_t temp;

% z' f; h6 @$ k0 e - temp = GPIOx->IDR; //读取 GPIOB_IDR 寄存器的值到变量 temp 中

) K& X$ C+ J' }, d T+ z* |这段代码先用 GPIO_TypeDef 类型定义一个结构体指针GPIOx,并让指针指向地址GPIOB_BASE(0x4001 0C00),使用地址确定下来,然后根据 C 语言访问结构体的语法,用6 P/ B# {4 A$ }6 o

GPIOx->ODR及 GPIOx->IDR 等方式读写寄存器。# Z3 w2 V+ {7 x9 a) w6 n

最后,我们更进一步,直接使用宏定义好 GPIO_TypeDef 类型的指针,而且指针指向各个 GPIO端口的首地址,使用时我们直接用该宏访问寄存器即可. - /*使用 GPIO_TypeDef 把地址强制转换成指针*/

, Z' u3 s% S8 Q2 n6 {- p - #define GPIOA ((GPIO_TypeDef *) GPIOA_BASE)( M0 w9 I v% l& T

- #define GPIOB ((GPIO_TypeDef *) GPIOB_BASE)

; f3 G* L. e2 \" L4 u. [& q - #define GPIOC ((GPIO_TypeDef *) GPIOC_BASE)

8 t8 P# {. D4 P1 n - #define GPIOD ((GPIO_TypeDef *) GPIOD_BASE)

. C+ N2 a2 Y- u1 ]/ v - #define GPIOE ((GPIO_TypeDef *) GPIOE_BASE)

4 A- |3 [) q* @9 \. \' Y - #define GPIOF ((GPIO_TypeDef *) GPIOF_BASE)

* _, C. h$ u7 S# c B* ~+ c - #define GPIOG ((GPIO_TypeDef *) GPIOG_BASE)$ X9 A" g: ^$ u! A' s1 z

- #define GPIOH ((GPIO_TypeDef *) GPIOH_BASE)

- ^! O1 z/ J* C! N# W+ F - 使用定义好的宏直接访问*/( v5 ]2 ?1 L: t1 A2 r2 ^* F u

- /*访问 GPIOB 端口的寄存器*/! T, c) X/ b' [

- GPIOB->BSRR = 0xFFFF; //通过指针访问并修改 GPIOB_BSRR 寄存器

( |$ }; ^) A$ R9 C' v+ t - 1GPIOB->CRL = 0xFFFF; //修改 GPIOB_CRL 寄存器

/ I/ l& L( v' S - GPIOB->ODR =0xFFFF; //修改 GPIOB_ODR 寄存器

$ h% k; b% `( n6 g6 G4 s, r - int32_t temp;

2 Y+ H/ P8 j# P# V% S# [& ]7 Z' D, p, w - temp = GPIOB->IDR; //读取 GPIOB_IDR 寄存器的值到变量 temp 中6 s2 M6 T* l$ p0 f. n! u* ^( l

- *访问 GPIOA 端口的寄存器*/

0 Z! `; Z+ H$ o+ ~0 A - GPIOA->BSRR = 0xFFFF;

$ e& A- o/ T1 P# Z- c) C8 K - GPIOA->CRL = 0xFFFF;

: E% Y8 {( B+ `, v. [ - GPIOA->ODR =0xFFFF;

/ N; n# M! W" P - uint32_t temp;- D0 L; t4 V( X' P" x4 n

- temp = GPIOA->IDR; //读取 GPIOA_IDR 寄存器的值到变量 temp 中

3 I# l6 g2 A* D- _这里我们仅是以 GPIO 这个外设为例,给大家讲解了 C 语言对寄存器的封装。以此类推,其他外设也同样可以用这种方法来封装。好消息是,这部分工作都由固件库帮我们完成了,这里我们只是分析了下这个封装的过程,让大家知其然,也只其所以然。" m5 c9 ], R# R _: l

点亮LED灯

( u! j: a7 l7 y思路 1. 打开引脚PC13时钟$ n* O$ X# ]6 K! c

2. 配置输出,确定输出模式

7 S6 w x3 z2 y7 n3. 输出低电平 程序 - int main()

$ l9 y( |, G I- A, i0 A) [ - {

4 f0 `9 z* [0 k5 e$ x6 R - *(unsigned int*)0x40021018 |=(1<<4);//打开GPIO时钟1 g/ o" j6 N* I2 s! a+ B

- *(unsigned int*)0x40011004 &=~(0x0F<<(4*5));//配置输出模式, k4 C/ Q9 o9 s: i# `2 P4 f. Q

- *(unsigned int*)0x40011004 |=(1<<(4*5));; K9 F5 e r( s# @$ j% d Y

- *(unsigned int*)0x4001100C &=~(1<<13);//配置输出低电平% `# F u* \! ?$ @, A; E+ s' H+ Z

- }

转载自: [color=var(--weui-FG-2)]跋扈洋2 q8 P- p) b: h8 B! t5 F# a

|

.png) STMCU小助手

发布时间:2022-11-28 14:27

STMCU小助手

发布时间:2022-11-28 14:27

微信公众号

微信公众号

手机版

手机版