.png) STMCU小助手

发布时间:2022-12-14 13:28

STMCU小助手

发布时间:2022-12-14 13:28

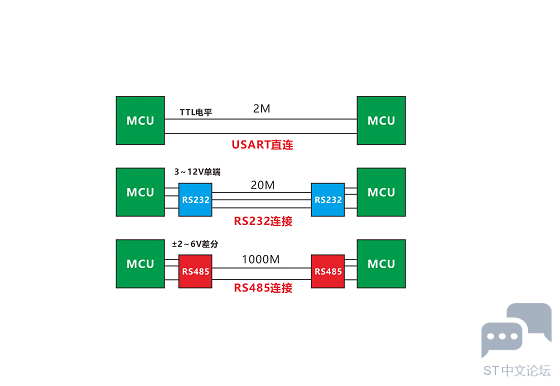

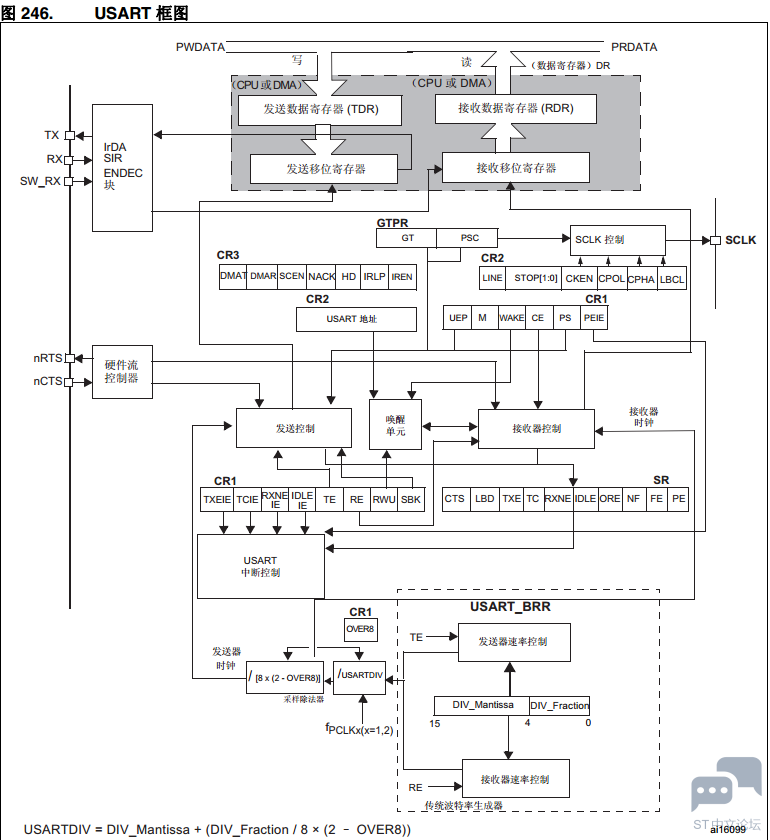

通用同步异步收发器(USART:universal synchronous asynchronous receiver and transmitter)能够灵活地与外部设备进行全双工数据交换,满足外部设备对工业标准NRZ异步串行数据格式的要求。USART通过小数波特率发生器提供了多种波特率。 它支持同步单向通信和半双工单线通信,还支持LIN(局域网互连网络)、智能卡协议与IrDA(红外线数据协会)SIR ENDEC规范,以及调制解调解调器操作(CTS/RTS)。而且,还支持多处理器通信。通过配置多个缓冲区使用DMA可实现高速数据通信。USART主要特性

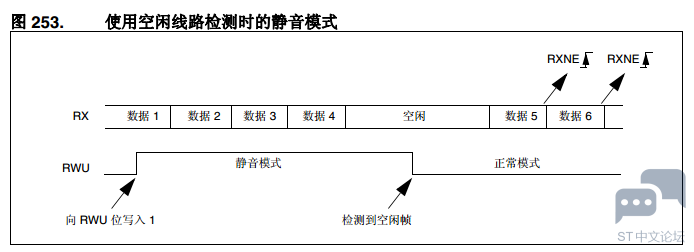

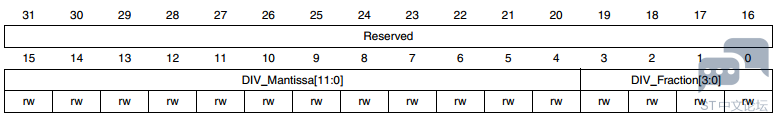

USARTDIV 是一个存放在 USART_BRR 寄存器中的无符号定点数。 ● 当 OVER8=0 时,小数部分编码为 4 位并通过 USART_BRR 寄存器中的 DIV_fraction[3:0]位编程。 ● 当 OVER8=1 时,小数部分编码为 3 位并通过 USART_BRR 寄存器中的 DIV_fraction[2:0]位编程,此时 DIV_fraction[3] 位必须保持清零状态。 注意:对 USART_BRR 执行写操作后,波特率计数器更新为波特率寄存器中的新值。因此,波特率寄存器的值不应在通信时发生更改。 OVER8=0 时如何从 USART_BRR 寄存器值中获取 USARTDIV 示例 1: 如果 DIV_Mantissa = 0d27 且 DIV_Fraction = 0d12 (USART_BRR = 0x1BC),则 尾数 (USARTDIV) = 0d27=0x1B 小数 (USARTDIV) = 12/16 = 0d0.75=0x0C 因此 USARTDIV = 0d27.75 =0x1B<<4| 0x0C=0x1BC USART 接收器对时钟偏差的容差 仅当总时钟系统偏差小于 USART 接收器的容差时, USART 异步接收器器才能正常工作。 影响总偏差的因素包括: ● DTRA:发送器误差引起的偏差(其中还包括发送器本地振荡器的偏差) ● DQUANT:接收器的波特率量化引起的误差 ● DREC:接收器本地振荡器的偏差 ● DTCL:传输线路引起的偏差(通常是由于收发器所引起,它可能会在低电平到高电平转换时序与高电平到低电平转换时序之间引入不对称) DTRA + DQUANT + DREC + DTCL < USART 接收器的容差 对于正常接收数据, USART 接收器的容差等于所容许的最大偏差,具体取决于以下选择: ● 由 USART_CR1 寄存器中的 M 位定义的 10 位或 11 位字符长度 ● 由 USART_CR1 寄存器中的 OVER8 位定义的 8 倍或 16 倍过采样 ● 是否使用小数波特率 ● 使用 1 位或 3 位对数据进行采样,取决于 USART_CR3 寄存器中 ONEBIT 位的值 多处理器通信 可以与 USART 进行多处理器通信(多个 USART 连接在一个网络中)。例如,其中一个 USART 可以是主 USART,其 TX 输出与其它 USART 的 RX 输入相连接。其它 USART 为 从 USART,其各自的 TX 输出在逻辑上通过与运算连在一起,并与主 USART 的 RX 输入相 连接。 在多处理器配置中,理想情况下通常只有预期的消息接收方主动接收完整的消息内容,从而 减少由所有未被寻址的接收器造成的冗余 USART 服务开销。 可通过静音功能将未被寻址的器件置于静音模式下。在静音模式下: ● 不得将接收状态位置 1。 ● 禁止任何接收中断。 ● USART_CR1 寄存器中的 RWU 位置 1。RWU 可由硬件自动控制,或在特定条件下由软 件写入。 根据 USART_CR1 寄存器中 WAKE 位的设置, USART 可使用以下两种方法进入或退出静 音模式: ● 如果 WAKE 位被复位,则进行空闲线路检测, ● 如果 WAKE 位置 1,则进行地址标记检测。 空闲线路检测 (WAKE=0) 当向 RWU 位写入 1 时, USART 进入静音模式。 当检测到空闲帧时,它会被唤醒。此时 RWU 位会由硬件清零,但 USART_SR 寄存器中的 IDLE 位不会置 1。还可通过软件向 RWU 位写入 0。 图 253 中给出了使用空闲线路检测时静音模式行为的示例

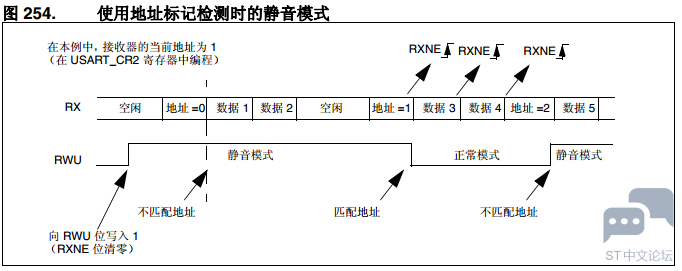

地址标记检测 (WAKE=1) 在此模式下,如果字节的 MSB 为 1,则将这些字节识别为地址,否则将其识别为数据。在 地址字节中,目标接收器的地址位于 4 个 LSB 上。接收器会将此 4 位字与其地址进行比较,该接收器的地址在 USART_CR2 寄存器的 ADD 位中进行设置。 当接收到与其编程地址不匹配的地址字符时, USART 会进入静音模式。此时, RWU 位将由硬件置 1。由于当时 USART 已经进入了静音模式,所以 RXNE 标志不会针对此地址字节置 1,也不会发出中断或 DMA 请求。 当接收到与编程地址匹配的地址字符时,它会退出静音模式。然后 RWU 位被清零,可以开始正常接收后续字节。由于 RWU 位已清零, RXNE 位会针对地址字符 置 1。 当接收器的缓冲区不包含任何数据(USART_SR 寄存器中 RXNE=0)时,可向 RWU 位写入 0 或 1。否则会忽略写尝试。 图 254 中给出了使用地址标记检测时静音模式行为的示例。

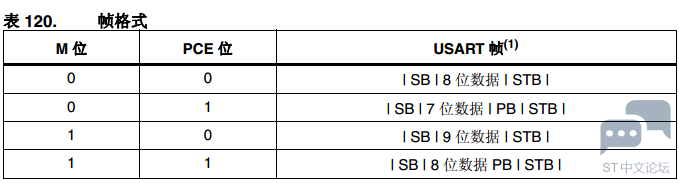

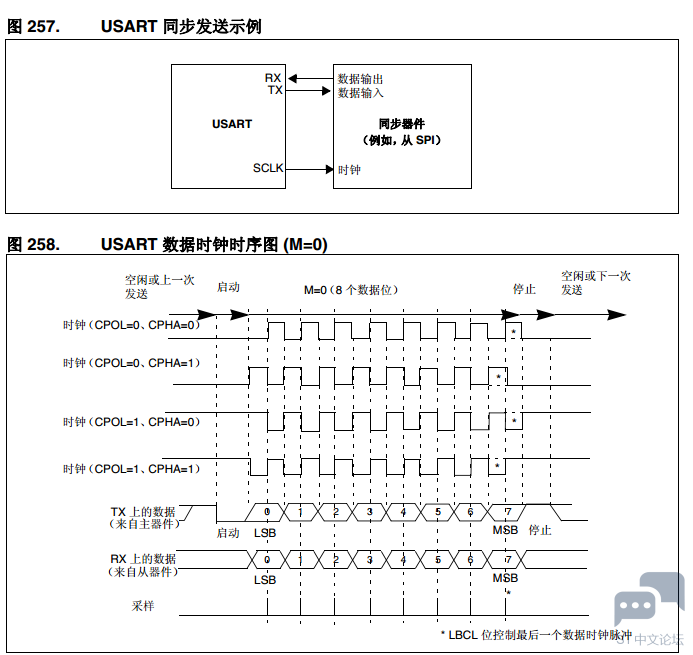

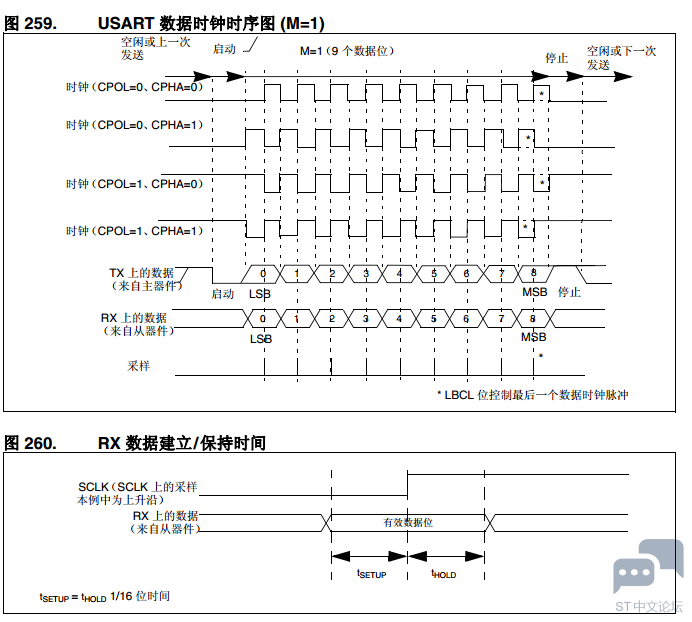

奇偶校验控制 将 USART_CR1 寄存器中的 PCE 位置 1,可以使能奇偶校验控制(发送时生成奇偶校验位,接收时进行奇偶校验检查)。根据 M 位定义的帧长度, 表 120 中列出了可能的 USART 帧格式。

偶校验 对奇偶校验位进行计算,使帧和奇偶校验位中“1”的数量为偶数(帧由 7 个或 8 个 LSB 位组成,具体取决于 M 等于 0 还是 1)。 例如:数据=00110101;4 个位置 1 => 如果选择偶校验(USART_CR1 寄存器中的 PS 位 =0),则校验位是 0。 奇校验 对奇偶校验位进行计算,使帧和奇偶校验位中“1”的数量为奇数(帧由 7 个或 8 个 LSB 位组成,具体取决于 M 等于 0 还是 1)。 例如:数据=00110101;4 个位置 1 => 如果选择奇校验(USART_CR1 寄存器中的 PS 位 =1),则校验位是 1。 接收时进行奇偶校验检查 如果奇偶校验检查失败,则 USART_SR 寄存器中的 PE 标志置 1;如果 USART_CR1 寄存 器中 PEIE 位置 1,则会生成中断。PE 标志由软件序列清零(从状态寄存器中读取,然后对USART_DR 数据寄存器执行读或写访问)。 注意:如果被地址标记唤醒:会使用数据的 MSB 位而非奇偶校验位来识别地址。此外,接收器不会对地址数据进行奇偶校验检查(奇偶校验出错时, PE 不置 1)。 发送时的奇偶校验生成 如果 USART_CR1 寄存器中的 PCE 位置 1,则在数据寄存器中所写入数据的 MSB 位会进行传送,但是会由奇偶校验位进行更改(如果选择偶校验 (PS=0),则“1”的数量为偶数; 如果选择奇校验 (PS=1),则“1”的数量为奇数)。 注意:用于管理发送过程的软件程序可以激活软件序列,进而将 PE 标志清零(从状态寄存器中读取,然后对数据寄存器执行读或写访问)。在半双工模式下工作时(具体取决于软件),这可能会导致 PE 标志意外清零. LIN(局域互连网络)模式 LIN 发送 与正常的 USART 发送相比,在 LIN 主器件中发送时必须采用 第 26.3.2 节 中介绍的相同步骤,同时还具有以下区别: ● M 位清零以配置 8 位字长度。 ● LINEN 位置 1 以进入 LIN 模式。此时,将 SBK 位置 1 会发送 13 个“0”位作为断路字符。然后会发送值为“1”的位以进行下一启动检测。 LIN 接收 断路检测电路在 USART 接口上实现。该检测完全独立于正常的 USART 接收器。在空闲状态或某个帧期间,只要发生断路即可检测出来。 接收器(USART_CR1 寄存器中 RE=1)使能后,电路便开始监测启动信号的 RX 输入。检测起始位的方法与搜索断路字符或数据的方法相同。检测到起始位后,电路会对接下来的位 进行采样,方法与数据采样相同(第 8、第 9 和第 10 次采样)。如果 10 个(USART_CR2寄存器中 LBDL = 0 时)或 11 个(USART_CR2 寄存器中 LBDL=1 时)连续位均检测为 “0”,且其后跟随分隔符,则 USART_SR 寄存器中的 LBD 标志将会置 1。如果 LBDIE 位=1,则会生成中断。在验证断路前,会对分隔符进行检查,因为它表示 RX 线路已恢复到高电平。 如果在第 10 或第 11 次采样前已对“1”采样,则断路检测电路会取消当前检测,并重新搜索起始位。 如果禁止 LIN 模式 (LINEN=0),接收器会作为正常的 USART 继续工作,不会再进行断路检测。 如果使能 LIN 模式 (LINEN=1), 只要发生帧错误(例如,在“0”处检测到停止位,这种情况可能出现在任何断路帧中),接收器即会停止,直到断路检测电路接收到“1”(断路字不完整时)或接收到分隔符(检测到断路时)为止。 USART 同步模式 通过将 USART_CR2 寄存器中的 CLKEN 位写入 1 来选择同步模式。在同步模式下,必须将以下位清零: ● USART_CR2 寄存器中的 LINEN 位, ● USART_CR3 寄存器中的 SCEN、 HDSEL 和 IREN 位。 通过 USART,用户可以在主模式下控制双向同步串行通信。SCLK 引脚是 USART 发送器时钟的输出。在起始位或停止位期间,不会向 SCLK 引脚发送时钟脉冲。在最后一个有效数据位(地址标记)期间,将会(也可能不会)生成时钟脉冲,这取决于 USART_CR2 寄存器中 LBCL 位的状态。通过 USART_CR2 寄存器中的 CPOL 位,用户可以选择时钟极性;通 过 USART_CR2 寄存器中的 CPHA 位,用户可以选择外部时钟相位 在空闲状态、报头模式和发送断路期间,外部 SCLK 时钟处于未激活状态。 USART 发送器在同步模式下的工作方式与异步模式下完全相同。但是由于 SCLK 与 TX 同步(根据 CPOL 和 CPHA),因此 TX 上的数据是同步的。 在此模式下, USART 接收器的工作方式与异步模式下不同。如果 RE=1,则数据在 SCLK上采样(上升或下降沿,取决于 CPOL 和 CPHA),而不会进行任何过采样。此时必须确保建立时间和保持时间(取决于波特率:1/16 位时间)符合要求。 注意:SCLK 引脚可与 TX 引脚结合使用。因此,仅当使能发送器 (TE=1) 且正在发送数据时(对数据寄存器 USART_DR 已被写入),才会提供时钟。这意味着,没有发送数据的情况下无法接收同步数据。 当发送器和接收器 (TE=RE=0) 都被禁止时,必须选择 LBCL、 CPOL 和 CPHA 位,以确保时钟脉冲正常工作。当使能发送器或接收器时,不得对这些位进行更改。 建议按照相同指令将 TE 和 RE 位置 1,以尽量缩短接收器的建立时间和保持时间。 USART 只支持主模式:它不能接收或发送与输入时钟相关的数据(SCLK 始终为输出

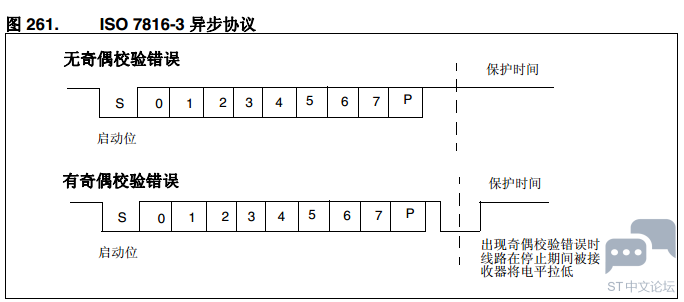

单线半双工通信 通过将 USART_CR3 寄存器中的 HDSEL 位置 1 来选择单线半双工模式。在此模式下,必须将以下位清零: ● USART_CR2 寄存器中的 LINEN 和 CLKEN 位, ● USART_CR3 寄存器中的 SCEN 和 IREN 位。 USART 可以配置为遵循单线半双工协议,其中 TX 和 RX 线路从内部相连接。使用控制位“HALF DUPLEX SEL”(USART_CR3 寄存器中的 HDSEL 位),可以在半双工通信和全双工通信间进行选择。 一旦向 HDSEL 位写入 1: ● TX 和 RX 线路从内部相连接 ● 不能再使用 RX 引脚 ● 无数据传输时, TX 引脚始终处于释放状态。因此,它在空闲状态或接收过程中用作标准I/O。这意味着,必须对 I/O 进行配置,以便在未受 USART 驱动时,使 TX 成为浮空输入(或高电平开漏输出) 除此之外,通信与正常 USART 模式下的通信相似。此线路上的冲突必须由软件进行管理(例如,使用中央仲裁器)。尤其要注意,发送过程永远不会被硬件封锁,只要数据是在TE 位置 1 的情况下写入,发送就会持续进行。 智能卡 通过将 USART_CR3 寄存器中的 SCEN 位置 1 来选择智能卡模式。在智能卡模式下,必须将以下位清零: ● USART_CR2 寄存器中的 LINEN 位, ● USART_CR3 寄存器中的 HDSEL 和 IREN 位。 此外,可能需要将 CLKEN 位置 1,以便为智能卡提供时钟。 智能卡接口支持符合 ISO 7816-3 标准的异步协议智能卡。USART 应如下所示进行配置: ● 8 个位加奇偶校验:当 USART_CR1 寄存器中 M=1 且 PCE=1 时 ● 发送和接收时使用 1.5 个停止位:当 USART_CR2 寄存器中 STOP=11 时。

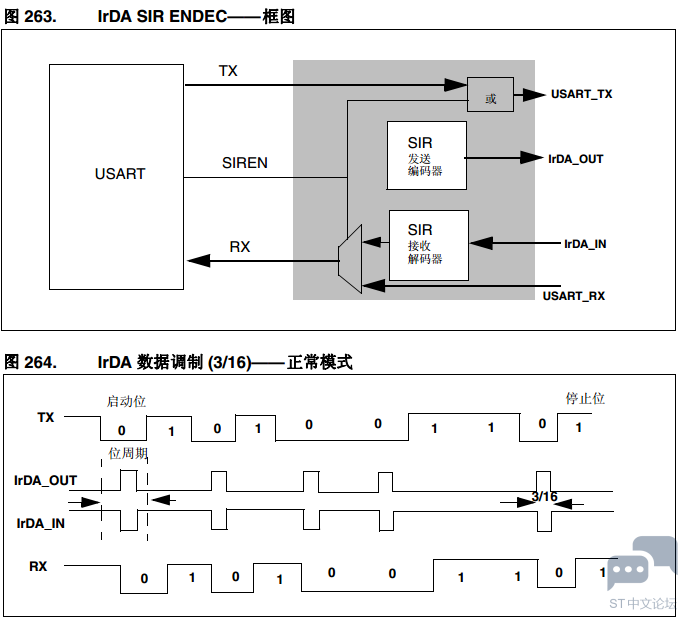

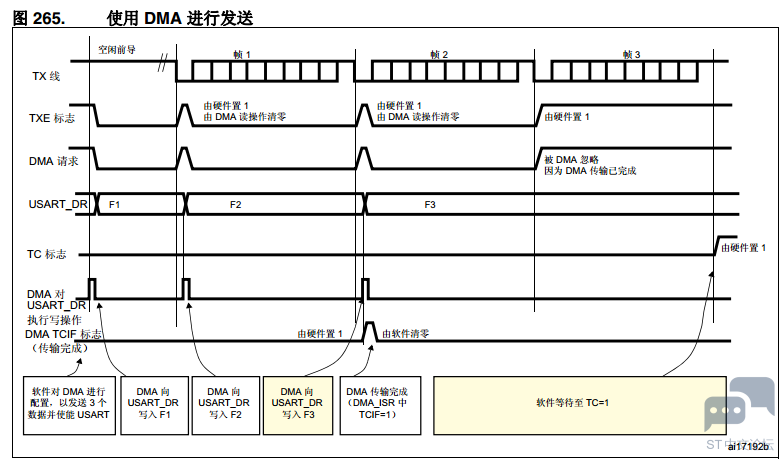

连接到智能卡时, USART 的 TX 输出会驱动一条双向线(它也由智能卡驱动)。必须将 TX引脚配置为开漏引脚。 智能卡是一个单线半双工通信协议。 ● 从发送移位寄存器发送数据会经过至少 1/2 个时钟周期的延迟。正常工作时,已满的发送移位寄存器会在下一个时钟边沿开始移位。在智能卡模式下,此发送过程还会进一步经过 1/2 波特时钟周期的延迟。 ● 如果在接收一个使用 0.5 或 1.5 个停止位编程的帧期间检测到奇偶校验错误,则在完成接收帧后,发送线会被拉低一个时钟周期。这是为了向智能卡指出发送到 USART 的数据尚未正确接收。此 NACK 信号(将发送线拉低 1 个时钟周期)会导致发送器端(配置为 1.5 个停止位)出现帧错误。应用程序可根据协议重新发送数据。如果 NACK 控制位置 1,则接收器会向奇偶校验错误发送“NACK”信号;否则不会发送 NACK 信号 . 通过对保护时间寄存器进行编程,可以延迟 TC 标志的置位。正常工作时,当发送移位寄存器为空且没有新的发送请求出现时,会对 TC 标志进行置位。在智能卡模式下,空的发送移位寄存器会触发保护时间计数器,使其递增计数至保护时间寄存器中的值。在此期间, TC 标志被强制为低电平。当保护时间计数器达到设置值时, TC 置位为高电平。 ● TC 标志的释放不受智能卡模式的影响。 ● 如果在发送端检测到帧错误(由来自接收器的 NACK 信号引起),则发送端的接收块不会将 NACK 作为起始位进行检测。根据 ISO 协议,接收到的 NACK 信号的持续时间可以是 1 或 2 个时钟周期。 ● 在接收端,如果检测到奇偶校验错误并发送了 NACK 信号,则接收端不会将 NACK 作为起始位进行检测。 注意:中断字符在智能卡模式下无效。带有帧错误的 0x00 数据将被视为数据,而非中断。 当翻转 TE 位时,不会发送空闲帧。空闲帧(在其它配置中进行了定义)在 ISO 协议中未进行定义 IrDA SIR ENDEC 模块 通过将 USART_CR3 寄存器中的 IREN 位置 1 来选择 IrDA 模式。在 IrDA 模式下,必须将以下位清零: ● USART_CR2 寄存器中的 LINEN、 STOP 和 CLKEN 位, ● USART_CR3 寄存器中的 SCEN 和 HDSEL 位。 IrDA SIR 物理层规定使用反相归零 (RZI) 调制方案,它以红外光脉冲表示逻辑 0。 SIR 发送编码器用于调制 USART 发出的非归零 (NRZ) 位流。输出脉冲流会发送到外部输出驱动器和红外线 LED。USART 支持的 SIR ENDEC 比特率最高为 115.2Kbps。在正常模式下,所发送的脉冲宽度规定为一个位周期的 3/16。 SIR 接收解码器用于解调由红外探测器发出的归零位流,并将接收到的 NRZ 串行位流输出到 USART。在空闲状态下,解码器输入通常为高电平(标记状态)。发送编码器输出的极性与解码器输入相反。当解码器输入为低电平时,会检测到起始位。 ● IrDA 是一个半双工通信协议。如果发送器忙(例如, USART 正在向 IrDA 编码器发送数据),则 IrDA 解码器会忽略 IrDA 接收线上的所有数据;如果接收器忙(例如, USART正在接收来自 USART 的解码数据),则 IrDA 不会对 USART 发送到 IrDA 的 TX 上的数据进行编码。在接收数据时,应避免同时进行发送,因为这样做可能会破坏要发送的数据。 ● “0”作为高电平脉冲发送,而“1”作为“0”发送。在正常模式下,脉冲宽度规定为所选位周期的 3/16。 ● SIR 解码器用于将兼容 IrDA 的接收信号转换为 USART 的位流。 ● SIR 接收逻辑将高电平状态视为逻辑“1”,将低电平脉冲视为逻辑“0”。 ● 发送编码器输出的极性与解码器输入相反。SIR 输出在空闲时处于低电平状态。 ● IrDA 规范要求脉冲容忍值要大于 1.41 us。可接受的脉冲宽度可通过寄存器设置。接收器端的干扰检测逻辑会滤除宽度小于 2 个 PSC 周期的脉冲(PSC 是在 IrDA 低功耗波特寄存器 USART_GTPR 中编程的预分频器值)。宽度小于 1 个 PSC 周期的脉冲都将被拒绝,但宽度大于 1 个而小于 2 个周期的脉冲可能被接受也可能被拒绝,而宽度大于 2 个周期的脉冲将被接受作为有效脉冲。当 PSC=0 时, IrDA 编码器/解码器不工作。 ● 接收器能够与低功耗发送器进行通信。 ● 在 IrDA 模式下, USART_CR2 寄存器中的 STOP 位必须配置为“1 个停止位” IrDA 低功耗模式 发送器: 在低功耗模式下,脉冲宽度不再保持为位周期的 3/16。此时的脉冲宽度为低功耗波特率的3 倍,最小可为 1.42 MHz。通常此值是 1.8432 MHz (1.42 MHz < PSC< 2.12 MHz)。低功耗 模式下的可编程分频器会对系统时钟进行分频,以达到此值。 接收器: 在低功耗模式下接收与在正常模式下接收类似。为进行干扰检测, USART 应丢弃持续时间短于 1/PSC 的脉冲。只有当持续时间大于 2 个 IrDA 低功耗波特时钟周期(USART_GTPR 寄存器中的 PSC 值)时,才是有效低电平。 注意:宽度小于两个但大于一个 PSC 周期的脉冲可能被接受,也可能被拒绝。 接收器的建立时间应由软件进行管理。IrDA 物理层规范规定发送和接收之间至少要经过 10 ms的延迟(IrDA 是一个半双工协议)

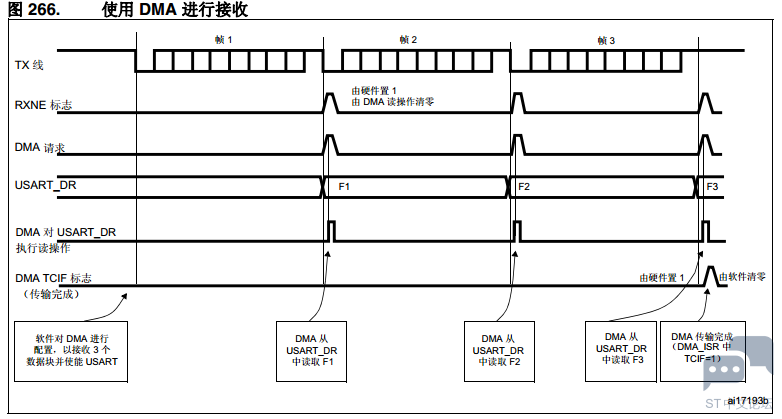

使用 DMA 进行连续通信 USART 能够使用 DMA 进行连续通信。接收缓冲区和发送缓冲区的 DMA 请求是独立的。 注意:有关 DMA 控制器可用性的信息,请参见产品规范。如果 DMA 不适用于该产品,应按照第26.3.2 节或 26.3.3 中的解释说明使用 USART。可以将 USART_SR 寄存器中的 TXE/RXNE标志清零,从而实现连续通信。使用 DMA 进行发送 将 USART_CR3 寄存器中的 DMAT 位置 1 可以使能 DMA 模式进行发送。当 TXE 位置 1 时,可将数据从 SRAM 区(通过 DMA 配置,参见 DMA 部分)加载到 USART_DR 寄存器。要映射一个 DMA 通道以进行 USART 发送,请按以下步骤操作(x 表示通道编号): 1. 在 DMA 控制寄存器中写入 USART_DR 寄存器地址,将其配置为传输的目标地址。每次发生 TXE 事件后,数据都会从存储器移动到此地址。 2. 在 DMA 控制寄存器中写入存储器地址,将其配置为传输的源地址。每次发生 TXE 事件后,数据都会从这个存储区域加载到 USART_DR 寄存器中。 3. 在 DMA 控制寄存器中配置要传输的总字节数。 4. 在 DMA 寄存器中配置通道优先级 5. 根据应用的需求,在完成一半或全部传输后产生 DMA 中断 6. 向 SR 寄存器中的 TC 位写入 0,将其清零。 7. 在 DMA 寄存器中激活该通道。 当达到在 DMA 控制器中设置的数据传输量时, DMA 控制器会在 DMA 通道的中断向量上产生一个中断。 在发送模式下, DMA 对所有要发送的数据执行了写操作(DMA_ISR 寄存器中的 TCIF 标志置 1)后,可以对 TC 标志进行监视,以确保 USART 通信已完成。在禁止 USART 或进入停止模式前必须执行此步骤,以避免损坏最后一次发送。软件必须等待直到 TC=1。TC 标志在所有数据发送期间都必须保持清零状态,然后在最后一帧发送结束后由硬件置 1。

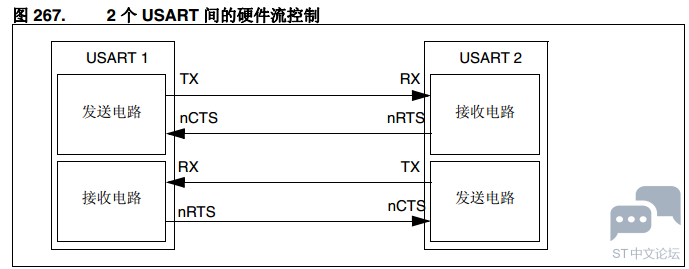

使用 DMA 进行接收 将 USART_CR3 寄存器中的 DMAR 位置 1 可以使能 DMA 模式进行接收。接收数据字节时,数据会从 USART_DR 寄存器加载到 SRAM 区域中(通过 DMA 配置,参见 DMA 规范)。要映射一个 DMA 通道以进行 USART 接收,请按以下步骤操作: 1. 在 DMA 控制寄存器中写入 USART_DR 寄存器地址,将其配置为传输的源地址。每次发生 RXNE 事件后,数据都会从此地址移动到存储器。 2. 在 DMA 控制寄存器中写入存储器地址,将其配置为传输的目标地址。每次发生 RXNE 事件后,数据都会从 USART_DR 寄存器加载到此存储区。 3. 在 DMA 控制寄存器中配置要传输的总字节数。 4. 在 DMA 控制寄存器中配置通道优先级。 5. 根据应用的需求,在完成一半或全部传输后产生中断。 6. 在 DMA 控制寄存器中激活该通道。 当达到在 DMA 控制器中设置的数据传输量时, DMA 控制器会在 DMA 通道的中断向量上产生一个中断。在中断子程序中, USART_CR3 寄存器中的 DMAR 位应由软件清零。注意:如果 DMA 用于接收,则不要使能 RXNEIE 位。

多缓冲区通信中的错误标志和中断生成 在多缓冲区通信中,如果事务中发生任何错误, 都会在当前字节后放置错误标志。如果中断使能置 1,则会产生中断。在单字节接收过程中,与 RXNE 一同置位的帧错误、上溢错误和噪声 标志具有单独的错误标志中断使能位(USART_CR3 寄存器中的 EIE 位);如果该位置 1, 则会因其中任何一个错误而在当前字节后产生中断。 硬件流控制 使用 nCTS 输入和 nRTS 输出可以控制 2 个器件间的串行数据流。图 267 显示了在这种模式下如何连接 2 个器件:

分别向 USART_CR3 寄存器中的 RTSE 位和 CTSE 位写入 1,可以分别使能 RTS 和 CTS 流控制。 RTS 流控制 如果使能 RTS 流控制 (RTSE=1),只要 USART 接收器准备好接收新数据,便会将 nRTS 变为有效(连接到低电平)。当接收寄存器已满时,会将 nRTS 变为无效,表明发送过程会在当前帧结束后停止。图 268 显示了在使能 RTS 流控制的情况下进行通信的示例。

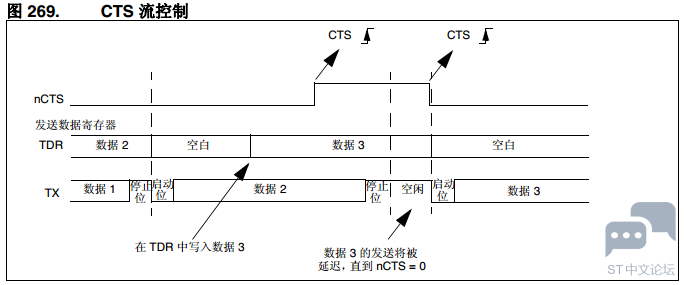

CTS 流控制 如果使能 CTS 流控制 (CTSE=1),则发送器会在发送下一帧前检查 nCTS。如果 nCTS 有效(连接到低电平),则会发送下一数据(假设数据已准备好发送,即 TXE=0);否则不会进行发送。如果在发送过程中 nCTS 变为无效,则当前发送完成之后,发送器停止。 当 CTSE=1 时,只要 nCTS 发生变化, CTSIF 状态位便会由硬件自动置 1。这指示接收器是否已准备好进行通信。如果 USART_CR3 寄存器中的 CTSIE 位置 1,则会产生中断。下图显示了在使能 CTS 流控制的情况下进行通信的示例。

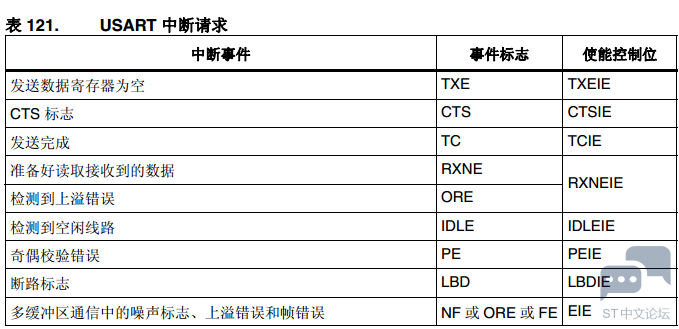

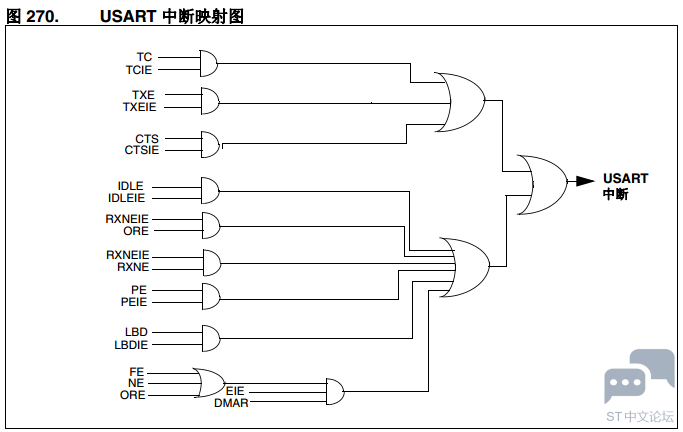

USART 中断

USART 中断事件被连接到相同的中断向量(请参见图 270)。 ● 发送期间:发送完成、清除以发送或发送数据寄存器为空中断。 ● 接收期间:空闲线路检测、上溢错误、接收数据寄存器不为空、奇偶校验错误、 LIN 断路检测、噪声标志(仅限多缓冲区通信)和帧错误(仅限多缓冲区通信)如果相应的使能控制位置 1,则这些事件会生成中断。

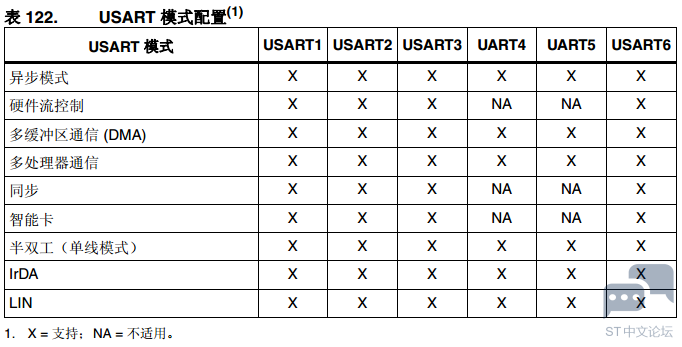

USART 模式配置

USART 寄存器 状态寄存器 (USART_SR)

位 31:10 保留,必须保持复位值 位 9 CTS:CTS 标志 (CTS flag) 如果 CTSE 位置 1,当 nCTS 输入变换时,此位由硬件置 1。通过软件将该位清零(通过向该位中写入 0)。如果 USART_CR3 寄存器中 CTSIE=1,则会生成中断。 0:nCTS 状态线上未发生变化 1:nCTS 状态线上发生变化 注意:该位不适用于 UART4 和 UART5。 位 8 LBD:LIN 断路检测标志 (LIN break detection flag) 检测到 LIN 断路时,该位由硬件置 1。通过软件将该位清零(通过向该位中写入 0)。如果USART_CR2 寄存器中 LBDIE = 1,则会生成中断。 0:未检测到 LIN 断路 1:检测到 LIN 断路 注意:如果 LBDIE=1,则当 LBD=1 时生成中断 位 7 TXE:发送数据寄存器为空 (Transmit data register empty) 当 TDR 寄存器的内容已传输到移位寄存器时,该位由硬件置 1。如果USART_CR1 寄存器中 TXEIE 位 = 1,则会生成中断。通过对 USART_DR 寄存器执行写入操作将该位清零。 0:数据未传输到移位寄存器 1:数据传输到移位寄存器 注意:单缓冲区发送期间使用该位。 位 6 TC:发送完成 (Transmission complete) 如果已完成对包含数据的帧的发送并且 TXE 置 1,则该位由硬件置 1。如果 USART_CR1 寄存器中 TCIE = 1,则会生成中断。该位由软件序列清零(读取 USART_SR 寄存器,然后写入USART_DR 寄存器)。TC 位也可以通过向该位写入‘0’来清零。建议仅在多缓冲区通信时使用此清零序列。 0:传送未完成 1:传送已完成 位 5 RXNE:读取数据寄存器不为空 (Read data register not empty) 当 RDR 移 位 寄 存 器 的 内 容 已 传 输 到 USART_DR 寄 存 器 时,该 位 由 硬 件 置 1。如 果USART_CR1 寄存器中 RXNEIE = 1,则会生成中断。通过对 USART_DR 寄存器执行读入操作将该位清零。RXNE 标志也可以通过向该位写入零来清零。建议仅在多缓冲区通信时使用此清零序列。 0:未接收到数据 1:已准备好读取接收到的数据 位 4 IDLE:检测到空闲线路 (IDLE line detected) 检测到空闲线路时,该位由硬件置 1。如果 USART_CR1 寄存器中 IDLEIE = 1,则会生成中断。该位由软件序列清零(读入 USART_SR 寄存器,然后读入 USART_DR 寄存器)。 0:未检测到空闲线路 1:检测到空闲线路 注意:直到 RXNE 位本身已置 1 时(即,当出现新的空闲线路时) IDLE 位才会被再次置 1。 位 3 ORE:上溢错误 (Overrun error) 在 RXNE = 1 的情况下,当移位寄存器中当前正在接收的字准备好传输到 RDR 寄存器时,该位由硬件置 1。如果 USART_CR1 寄存器中 RXNEIE = 1,则会生成中断。该位由软件序列清零(读入 USART_SR 寄存器,然后读入 USART_DR 寄存器)。 0:无上溢错误 1:检测到上溢错误 注意:当该位置 1 时, RDR 寄存器的内容不会丢失,但移位寄存器会被覆盖。如果 EIE 位置 1,则在进行多缓冲区通信时会对 ORE 标志生成一个中断。 位 2 NF:检测到噪声标志 (Noise detected flag) 当在接收的帧上检测到噪声时,该位由硬件置 1。该位由软件序列清零(读入 USART_SR 寄存器,然后读入 USART_DR 寄存器)。 0:未检测到噪声 1:检测到噪声 注意:如果 EIE 位置 1,则在进行多缓冲区通信时,该位不会生成中断,因为该位出现的时间与本身生成中断的 RXNE 位因 NF 标志而生成的时间相同。 注意:当线路无噪声时,可以通过将 ONEBIT 位编程为 1 提高 USART 对偏差的容差来禁止NF 标志 位 1 FE:帧错误 (Framing error) 当检测到去同步化、过度的噪声或中断字符时,该位由硬件置 1。该位由软件序列清零(读入USART_SR 寄存器,然后读入 USART_DR 寄存器)。 0:未检测到帧错误 1:检测到帧错误或中断字符 注意:该位不会生成中断,因为该位出现的时间与本身生成中断的 RXNE 位出现的时间相同。如果当前正在传输的字同时导致帧错误和上溢错误,则会传输该字,且仅有 ORE 位被置 1。 如果 EIE 位置 1,则在进行多缓冲区通信时会对 FE 标志生成一个中断。 位 0 PE:奇偶校验错误 (Parity error) 当在接收器模式下发生奇偶校验错误时,该位由硬件置 1。该位由软件序列清零(读取状态寄存器,然后对 USART_DR 数据寄存器执行读或写访问)。将 PE 位清零前软件必须等待。RXNE 标志被置 1。如果 USART_CR1 寄存器中 PEIE = 1,则会生成中断。 0:无奇偶校验错误 1:奇偶校验错误 数据寄存器 (USART_DR) 位 31:9 保留,必须保持复位值 位 8:0 DR[8:0]:数据值 包含接收到数据字符或已发送的数据字符,具体取决于所执行的操作是“读取”操作还是“写入”操作。 因为数据寄存器包含两个寄存器,一个用于发送 (TDR),一个用于接收 (RDR),因此它具有双重功能(读和写)。 TDR 寄存器在内部总线和输出移位寄存器之间提供了并行接口(参见图 1)。 RDR 寄存器在输入移位寄存器和内部总线之间提供了并行接口。 在使能奇偶校验位的情况下(USART_CR1 寄存器中的 PCE 位被置 1)进行发送时,由于MSB 的写入值(位 7 或位 8,具体取决于数据长度)会被奇偶校验位所取代,因此该值不起任何作用。 在使能奇偶校验位的情况下进行接收时,从 MSB 位中读取的值为接收到的奇偶校验位 。 波特率寄存器 (USART_BRR)

位 31:16 保留,必须保持复位值 位 15:4 DIV_Mantissa[11:0]:USARTDIV 的尾数 这 12 个位用于定义 USART 除数 (USARTDIV) 的尾数 位 3:0 DIV_Fraction[3:0]:USARTDIV 的小数 这 4 个位用于定义 USART 除数 (USARTDIV) 的小数。当 OVER8 = 1 时,不考虑 DIV_Fraction3位,且必须将该位保持清零 控制寄存器 1 (USART_CR1)

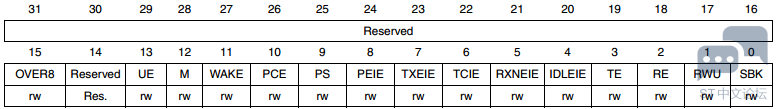

位 31:16 保留,必须保持复位值 位 15 OVER8:过采样模式 (Oversampling mode) 0:16 倍过采样 1:8 倍过采样 注意:8 倍过采样在智能卡、 IrDA 和 LIN 模式下不可用:当 SCEN=1、 IREN=1 或 LINEN=1 时,OVER8 由硬件强制清零。 位 14 保留,必须保持复位值 位 13 UE:USART 使能 (USART enable) 该位清零后, USART 预分频器和输出将停止,并会结束当前字节传输以降低功耗。此位由软 件置 1 和清零。 0:禁止 USART 预分频器和输出 1:使能 USART 位 12 M:字长 (Word length) 该位决定了字长。该位由软件置 1 或清零。 0:1 起始位, 8 数据位, n 停止位 1:1 起始位, 9 数据位, n 停止位 注意:在数据传输(发送和接收)期间不得更改 M 位 位 11 WAKE:唤醒方法 (Wakeup method) 该位决定了 USART 唤醒方法,该位由软件置 1 或清零。 0:空闲线路 1:地址标记 位 10 PCE:奇偶校验控制使能 (Parity control enable) 该位选择硬件奇偶校验控制(生成和检测)。使能奇偶校验控制时,计算出的奇偶校验位被插入到 MSB 位置(如果 M=1,则为第 9 位;如果 M=0,则为第 8 位),并对接收到的数据检查奇偶校验位。此位由软件置 1 和清零。一旦该位置 1, PCE 在当前字节的后面处于活动 状态(在接收和发送时)。 0:禁止奇偶校验控制 1:使能奇偶校验控制 位 9 PS:奇偶校验选择 (Parity selection) 该位用于在使能奇偶校验生成/检测(PCE 位置 1)时选择奇校验或偶校验。该位由软件置 1 和清零。将在当前字节的后面选择奇偶校验。 0:偶校验 1:奇校验 位 8 PEIE:PE 中断使能 (PE interrupt enable)此位由软件置 1 和清零。 0:禁止中断 1:当 USART_SR 寄存器中 PE=1 时,生成 USART 中断 位 7 TXEIE:TXE 中断使能 (TXE interrupt enable) 此位由软件置 1 和清零。 0:禁止中断 1:当 USART_SR 寄存器中 TXE=1 时,生成 USART 中断。 位 6 TCIE:传送完成中断使能 (Transmission complete interrupt enable) 此位由软件置 1 和清零。 0:禁止中断 1:当 USART_SR 寄存器中 TC=1 时,生成 USART 中断 位 5 RXNEIE:RXNE 中断使能 (RXNE interrupt enable) 此位由软件置 1 和清零。 0:禁止中断 1:当 USART_SR 寄存器中 ORE=1 或 RXNE=1 时,生成 USART 中断 位 4 IDLEIE:IDLE 中断使能 (IDLE interrupt enable)此位由软件置 1 和清零。 0:禁止中断 1:当 USART_SR 寄存器中 IDLE=1 时,生成 USART 中断 位 3 TE:发送器使能 (Transmitter enable)该位使能发送器。该位由软件置 1 和清零。 0:禁止发送器 1:使能发送器 注意:1:除了在智能卡模式下以外,传送期间 TE 位上的“0”脉冲(“0”后紧跟的是“1”)会在当前字的后面发送一个报头(空闲线路)。 2:当 TE 置 1 时,在发送开始前存在 1 位的时间延迟。 位 2 RE:接收器使能 (Receiver enable)该位使能接收器。该位由软件置 1 和清零。 0:禁止接收器 1:使能接收器并开始搜索起始位 位 1 RWU:接收器唤醒 (Receiver wakeup) 该位决定 USART 是否处于静音模式。该位由软件置 1 和清零,并可在识别出唤醒序列时由硬件清零。 0:接收器处于活动模式 1:接收器处于静音模式 注意:1:选择静音模式前(通过将 RWU 位置 1), USART 必须首先接收一个数据字节,否则,当由空闲线路检测到唤醒时,它无法于静音模式下正常工作。 2:在地址标记检测唤醒配置(WAKE 位 = 1)中, RXNE 位置 1 时, RWU 位不能由软件进行修改 位 0 SBK:发送断路 (Send break) 该位用于发送断路字符。该位可由软件置 1 和清零。该位应由软件置 1,并在断路停止位期间由硬件重置。 0:不发送断路字符 1:将发送断路字符 控制寄存器 2 (USART_CR2)

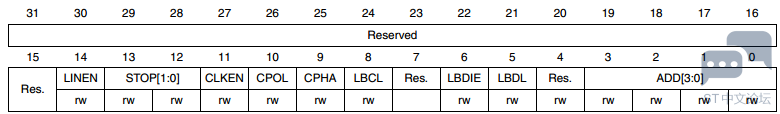

位 31:15 保留,必须保持复位值 位 14 LINEN:LIN 模式使能 (LIN mode enable) 此位由软件置 1 和清零。 0:禁止 LIN 模式 1:使能 LIN 模式 LIN 模式可以使用 USART_CR1 寄存器中的 SBK 位发送 LIN 同步断路(13 个低位),并可检测 LIN同步断路。 位 13:12 STOP:停止位 (STOP bit) 这些位用于编程停止位。 00:1 个停止位 01:0.5 个停止位 10:2 个停止位 11:1.5 个停止位 注意:0.5 个停止位和 1.5 个停止位不适用于 UART4 和 UART5。 位 11 CLKEN:时钟使能 (Clock enable) 该位允许用户使能 SCLK 引脚。 0:禁止 SCLK 引脚 1:使能 SCLK 引脚 该位不适用于 UART4 和 UART5。 位 10 CPOL:时钟极性 (Clock polarity) 该位允许用户在同步模式下选择 SCLK 引脚上时钟输出的极性。它与 CPHA 位结合使用可获得所需的时钟/数据关系 0:空闲时 SCLK 引脚为低电平。 1:空闲时 SCLK 引脚为高电平。 该位不适用于 UART4 和 UART5。 位 9 CPHA:时钟相位 该位允许用户在同步模式下选择 SCLK 引脚上时钟输出的相位。它与 CPOL 位结合使用可获得所需的时钟/数据关系 0:在时钟第一个变化沿捕获数据 1:在时钟第二个变化沿捕获数据 注意:该位不适用于 UART4 和 UART5。 位 8 LBCL:最后一个位时钟脉冲 (Last bit clock pulse) 该位允许用户在同步模式下选择与发送的最后一个数据位 (MSB) 关联的时钟脉冲是否必须在 SCLK引脚上输出。 0:最后一个数据位的时钟脉冲不在 SCLK 引脚上输出 1:最后一个数据位的时钟脉冲在 SCLK 引脚上输出 注意:1:最后一位为发送的第 8 或第 9 个数据位,具体取决于 USART_CR1 寄存器中 M 位所选择的8 位或 9 位格式。 2:该位不适用于 UART4 和 UART5。 位 7 保留,必须保持复位值 位 6 LBDIE:LIN 断路检测中断使能 (LIN break detection interrupt enable) 断路中断屏蔽(使用断路分隔符进行断路检测) 0:禁止中断 1:当 USART_SR 寄存器中 LBD = 1 时,生成中断 位 5 LBDL:lin 断路检测长度 (lin break detection length) 该位用于选择 11 位断路检测或 10 位断路检测。 0:10 位断路检测 1:11 位断路检测 位 4 保留,必须保持复位值 位 3:0 ADD[3:0]:USART 节点的地址,该位域用于指定 USART 节点的地址。将在多处理器通信时于静音模式下使用该位域,以通过地址标记检测进行唤醒。 注意:使能发送器时不应对这 3 个位(CPOL、 CPHA、 LBCL)进行写操作。 控制寄存器 3 (USART_CR3)

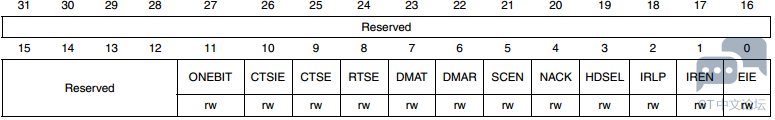

位 31:12 保留,必须保持复位值 位 11 ONEBIT:一个采样位方法使能 (One sample bit method enable) 该位允许用户选择采样方法。选择一个采样位方法后,将禁止噪声检测标志 (NF)。 0:三个采样位方法 1:一个采样位方法 位 10 CTSIE:CTS 中断使能 (CTS interrupt enable) 0:禁止中断 1:当 USART_SR 寄存器中 CTS = 1 时,生成中断 注意:该位不适用于 UART4 和 UART5。 位 9 CTSE:CTS 使能 (CTS enable) 0:禁止 CTS 硬件流控制 1:使能 CTS 模式,仅当 nCTS 输入有效 (连接到 0)时才发送数据。如果在发送数据时使 nCTS 输入无效,会在停止之前完成发送。如果使 nCTS 有效时数据已写入数据寄存器,则 将延迟发送,直到 nCTS 有效。 注意:该位不适用于 UART4 和 UART5。 位 8 RTSE:RTS 使能 (RTS enable) 0:禁止 RTS 硬件流控制 1:使能 RTS 中断,仅当接收缓冲区中有空间时才会请求数据。发送完当前字符后应停止发 送数据。可以接收数据时使 nRTS 输出有效 (连接到 0)。 注意:该位不适用于 UART4 和 UART5。 位 7 DMAT:DMA 使能发送器 (DMA enable transmitter) 该位由软件置 1/ 复位。 1:针对发送使能 DMA 模式。 0:针对发送禁止 DMA 模式。 位 6 DMAR:DMA 使能接收器 (DMA enable receiver) 该位由软件置 1/ 复位。 1:针对接收使能 DMA 模式 0:针对接收禁止 DMA 模式 位 5 SCEN:智能卡模式使能 (Smartcard mode enable) 该位用于使能智能卡模式。 0:禁止智能卡模式 1:使能智能卡模式 注意:该位不适用于 UART4 和 UART5。 位 4 NACK:智能卡 NACK 使能 (Smartcard NACK enable) 0:出现奇偶校验错误时禁止 NACK 发送 1:出现奇偶校验错误时使能 NACK 发送 注意:该位不适用于 UART4 和 UART5。 位 3 HDSEL:半双工选择 (Half-duplex selection) 选择单线半双工模式 0:未选择半双工模式 1:选择半双工模式 位 2 IRLP:IrDA 低功耗 (IrDA low-power) 该位用于选择正常模式和低功耗 IrDA 模式 0:正常模式 1:低功耗模式 位 1 IREN:IrDA 模式使能 (IrDA mode enable) 此位由软件置 1 和清零。 0:禁止 IrDA 1:使能 IrDA 位 0 EIE:错误中断使能 (Error interrupt enable) 对于多缓冲区通信(USART_CR3 寄存器中 DMAR = 1),如果发生帧错误、上溢错误或出 现噪声标志(USART_SR 寄存器中 FE = 1 或 ORE = 1 或 NF = 1),则需要使用错误中断 使能位来使能中断生成。 0:禁止中断 1:当 USART_CR3 寄存器中的 DMAR = 1 并且 USART_SR 寄存器中的 FE = 1 或 ORE = 1或 NF = 1 时,将生成中断。 保护时间和预分频器寄存器 (USART_GTPR)

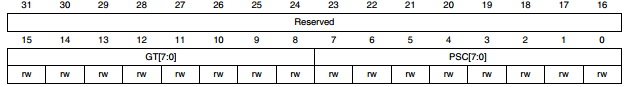

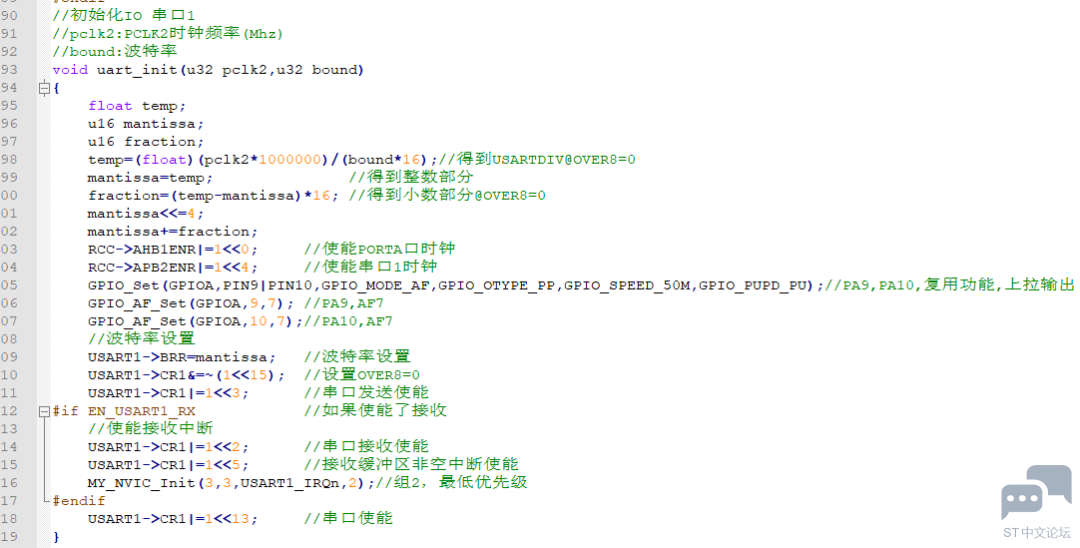

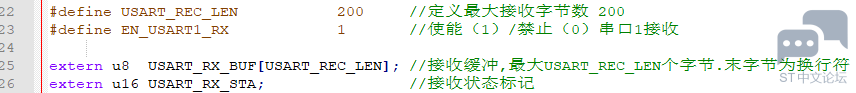

位 31:16 保留,必须保持复位值 位 15:8 GT[7:0]:保护时间值 (Guard time value) 该位域提供保护时间值 (以波特时钟数为单位)。 该位用于智能卡模式。经过此保护时间后,发送完成标志置 1。 注意:该位不适用于 UART4 和 UART5。 位 7:0 PSC[7:0]:预分频器值 — 在 IrDA 低功耗模式下: PSC[7:0] = IrDA 低功耗波特率 用于编程预分频器,进行系统时钟分频以获得低功耗频率: 使用寄存器中给出的值(8 个有效位)对源时钟进行分频: 00000000:保留 - 不编程此值 源时钟 1 分频 00000010:源时钟 2 分频 ... — 在正常 IrDA 模式下:PSC 必须设置为 00000001。 — 在智能卡模式下: PSC[4:0]:预分频器值 用于编程预分频器,进行系统时钟分频以提供智能卡时钟。 将寄存器中给出的值(5 个有效位)乘以 2 得出源时钟频率的分频系数: 00000:保留 - 不编程此值 00001:源时钟 2 分频 00010:源时钟 4 分频 00011:源时钟 6 分频 ... 注意:1:如果使用智能卡模式,则位 [7:5] 不起作用。 2:该位不适用于 UART4 和 UART5。 串口通信编程的一般步骤: 1.GPIO初始化 --使能GPIO对用的PORT时钟, --使能复用外设功能的时钟, --对使用的IO口进行mode ,otype,ospeed,opupd设置, --设置对应的IO为复用功能, 2.根据波特率和外设时钟,计算波特率,波特率转换为16进制,设置BRR寄存器, 3.配置CR1和CR2,配置字长和停止位, 4.使能发送、接收功能,使能接收中断位,设置中断分组; 5.使能串口, 6.编写串口发送函数(对单字节和字符串分别处理) 7.编写串口中断服务函数(对串口接收到的数据做分析和处理,提供容错能力,保证接收到错误的数据,不能死机) 串口初始化函数

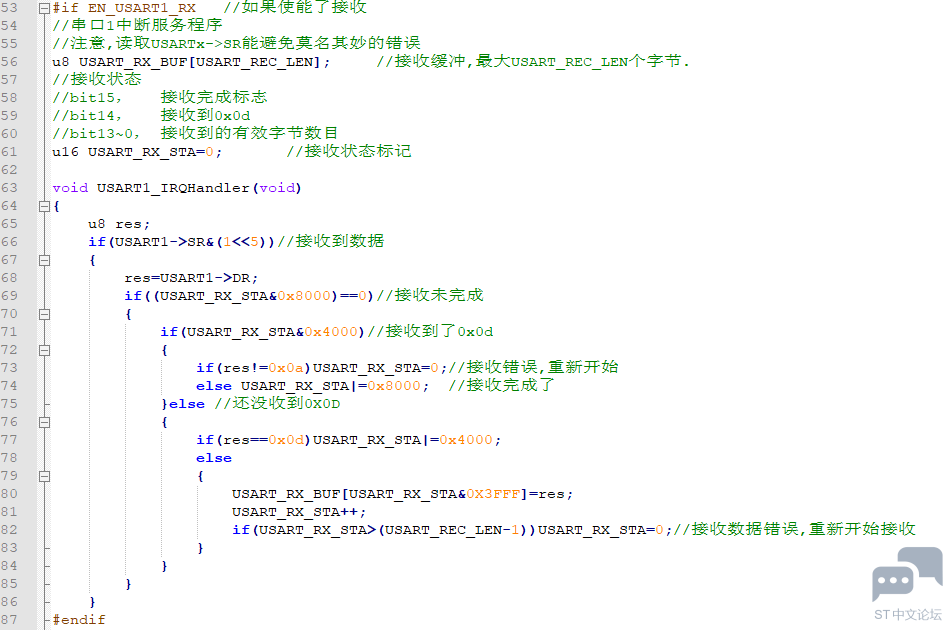

串口中断服务函数

串口发送函数

接收到的字符串数组设置

|

STM32 硬核调试技巧:用 DWT 硬件监控内存读写与函数调用

OpenBLT移植到STM32F103战舰开发板上适用于所有STM32F103系列的Bootloader

巧用 Linker 自定义变量,破解 STM32 Flash 全片自检 ROM 大小配置难题

经验分享 | LAT1471 Flash全片自检过程中巧用Linker自定义变量

STM32 LSE 不起振排查指南:五大核心原因与快速解决方案

学习STM32单片机,绕不开的串口

STM32串口通信基本原理

【STM32U3评测】实现双通道串口通信系统

OpenBLT移植到STM32F405开发板

【NUCLEO-WB09KE评测】STM32WB09KE的内部BootLoader使用

微信公众号

微信公众号

手机版

手机版