.png) STMCU小助手

发布时间:2022-12-26 15:00

STMCU小助手

发布时间:2022-12-26 15:00

|

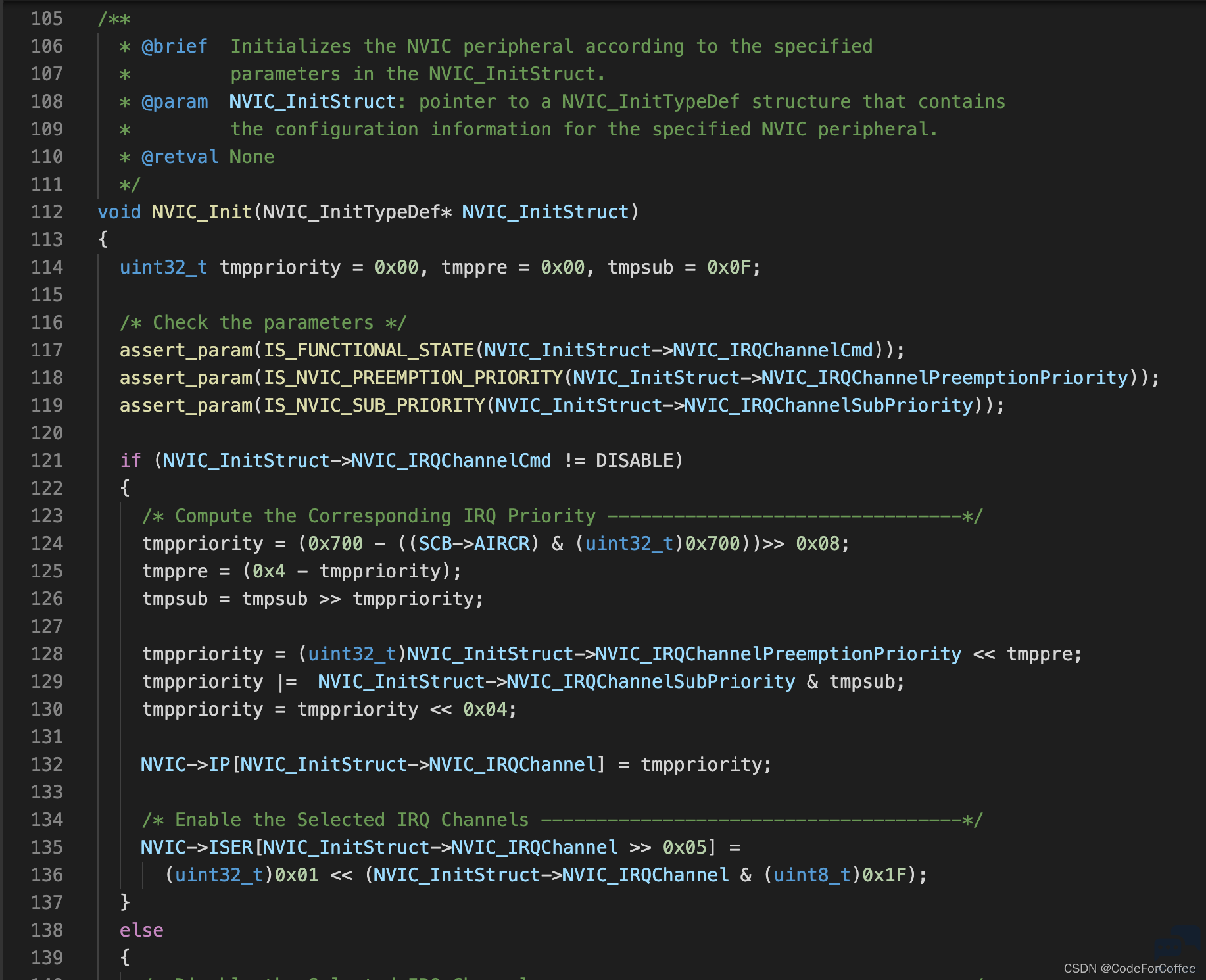

Cortex M3内核支持256个中断,其中包含: 16个内核中断 240个外部中断 并且具有256级可编程中断设置 STM32F1并没有使用Cortex M3的全部 STM32有84个中断,其中包括: 16个内核中断 68个外部中断(可屏蔽中断) STM32F103系列只有60个可屏蔽中断 中断优先级分组 首先,对STM32中断进行分组(在系统初始化时就分好组),组0~4.同时,对每个中断设置一个抢占优先级和一个响应优先级值 分组配置是在寄存器SCB->AIRCR中进行配置 ![UW`(R56FAUNXCXBQ)H0]6OO.png UW`(R56FAUNXCXBQ)H0]6OO.png](data/attachment/forum/202212/25/153227ku33x54p2qlb8xqz.png)

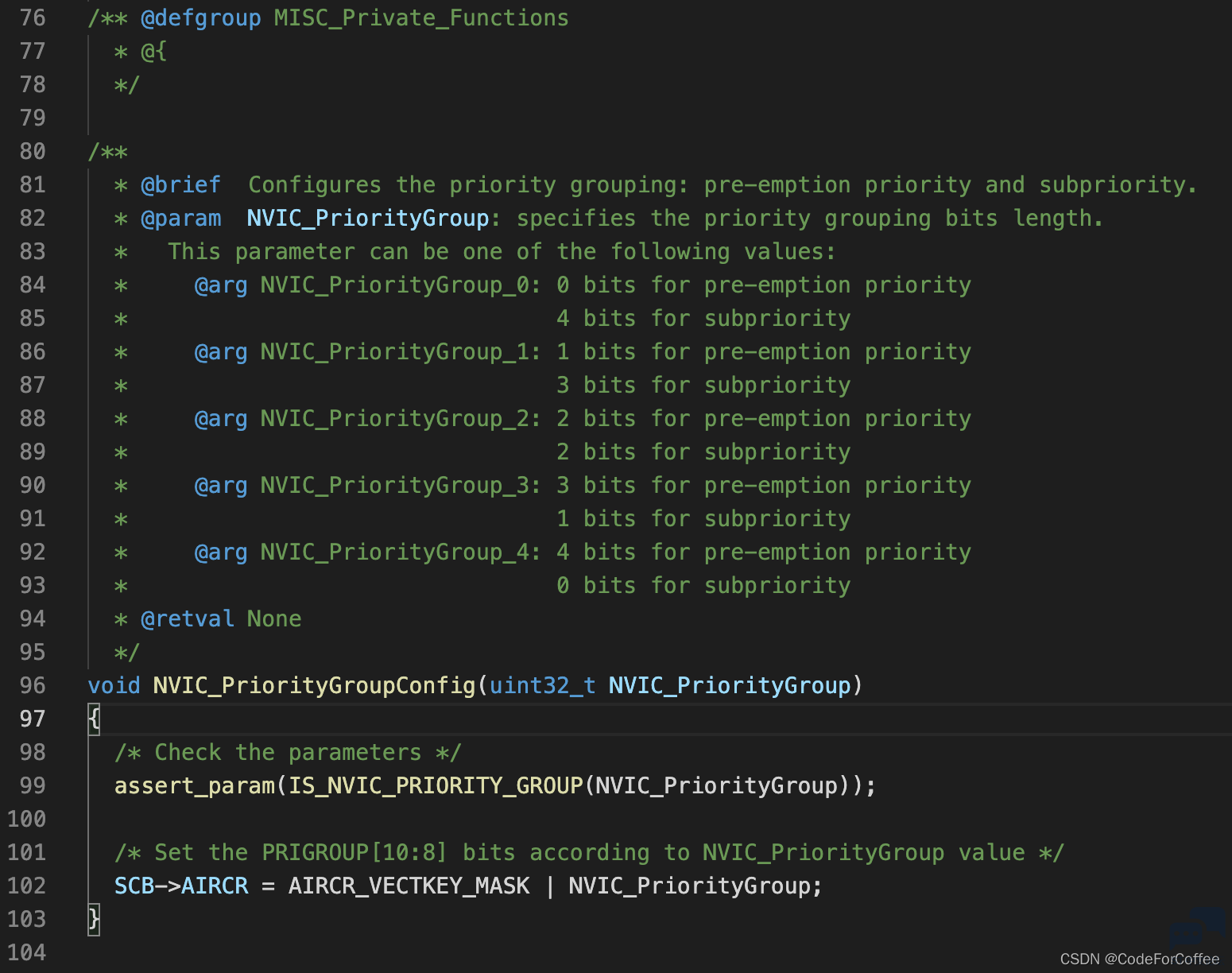

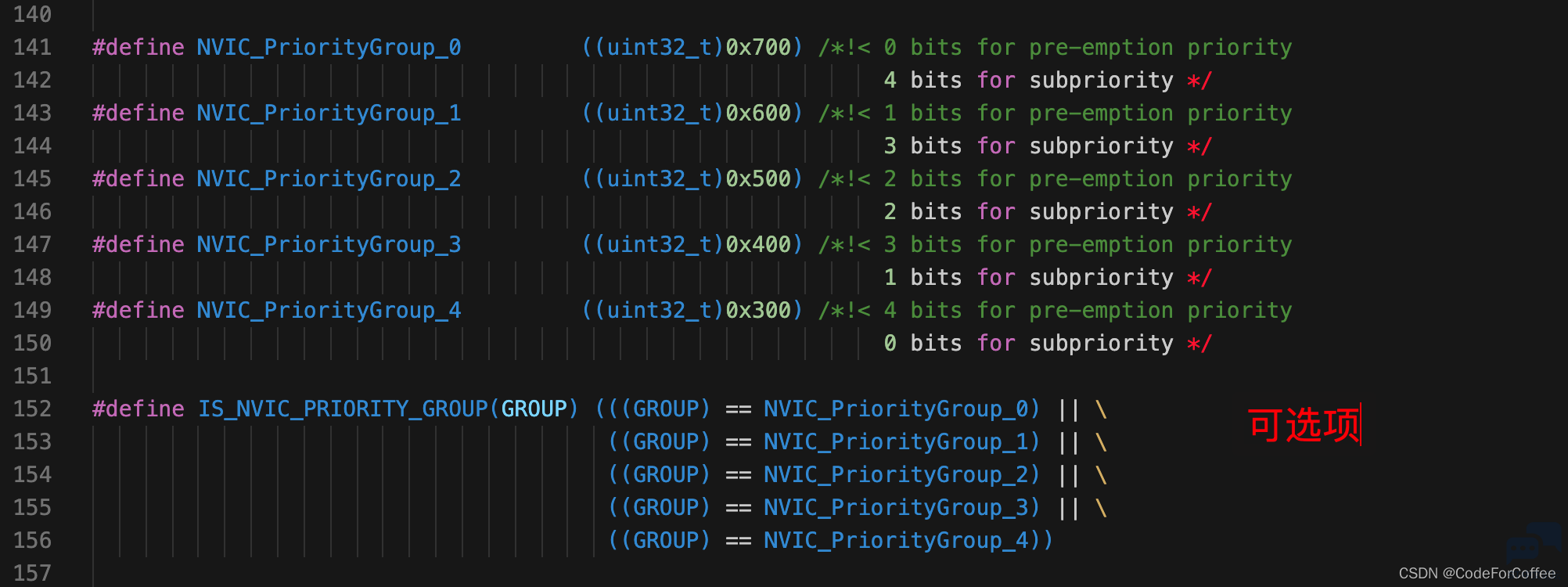

在SCB的AIRCR寄存器的8到10位可以对中断进行分组 假设被分到组2,意味着每个中断可以设置2位抢占优先级,2位响应优先级 对于每个中断,他有一个IP寄存器,4到7位,相当于一共4个位可以用来设置抢占和响应 STM32F103具有16级可编程的中断优先级,为什么是16级呢? 因为4个位可以用来设置抢占和响应 2的4次方就是16 抢占优先级与响应优先级的区别 抢占优先级是指,两个中断,抢占优先级谁高,谁就可以抢占另外一个正在执行的中断,可以打断 例如A中断的抢占优先级为0(优先级高),B中断的抢占优先级为3(低优先级),B正在发生,正在执行B中断的中断服务函数,如果A发生了,那么A是可以打断B的,执行完了再回去B 抢占优先级相同的中断,高响应优先级的中断不可以打断低响应优先级的中断 抢占优先级相同的中断,当两个中断同时发生时,哪个的优先级高,哪个就先执行 中断优先级分组函数 misc.c

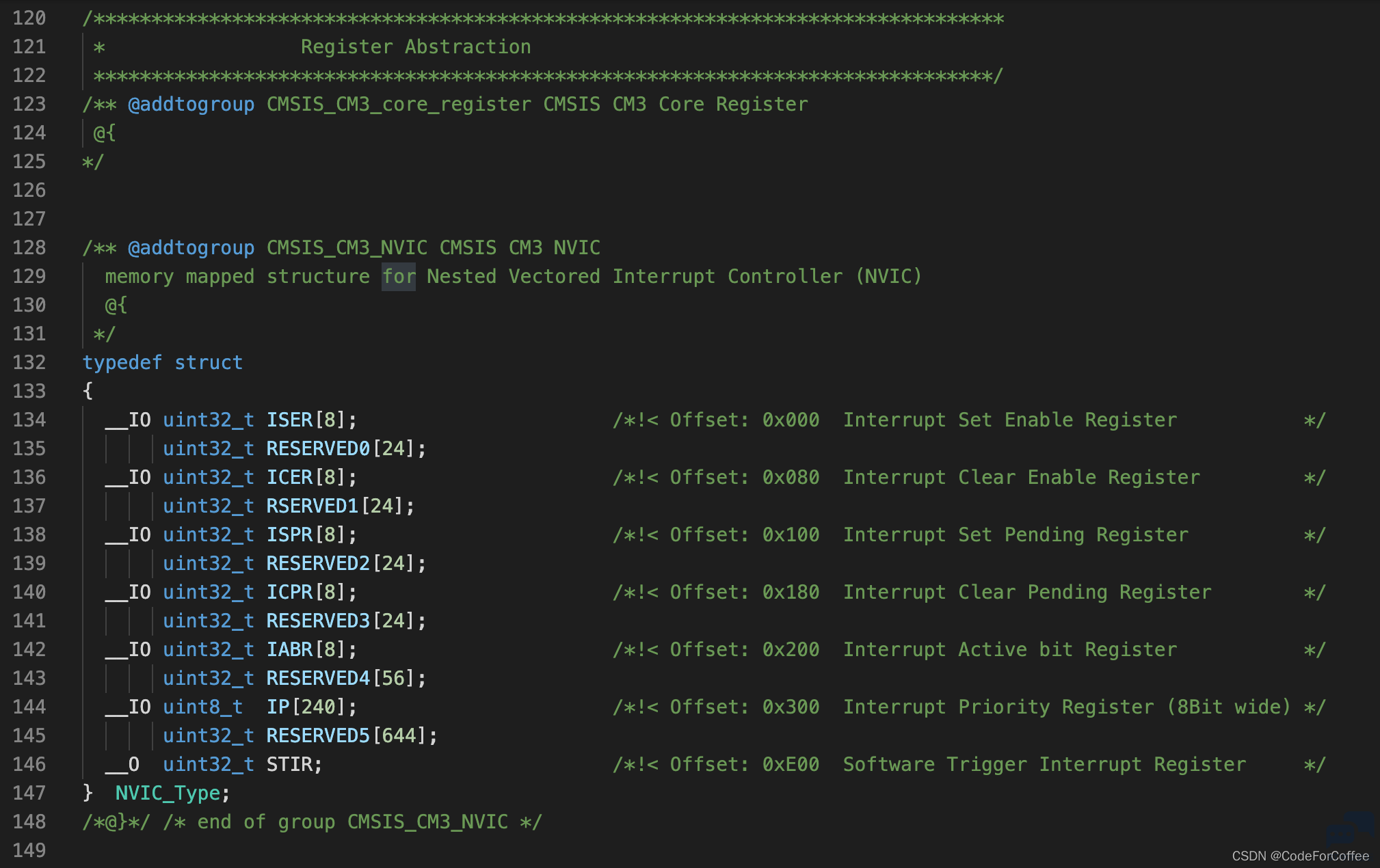

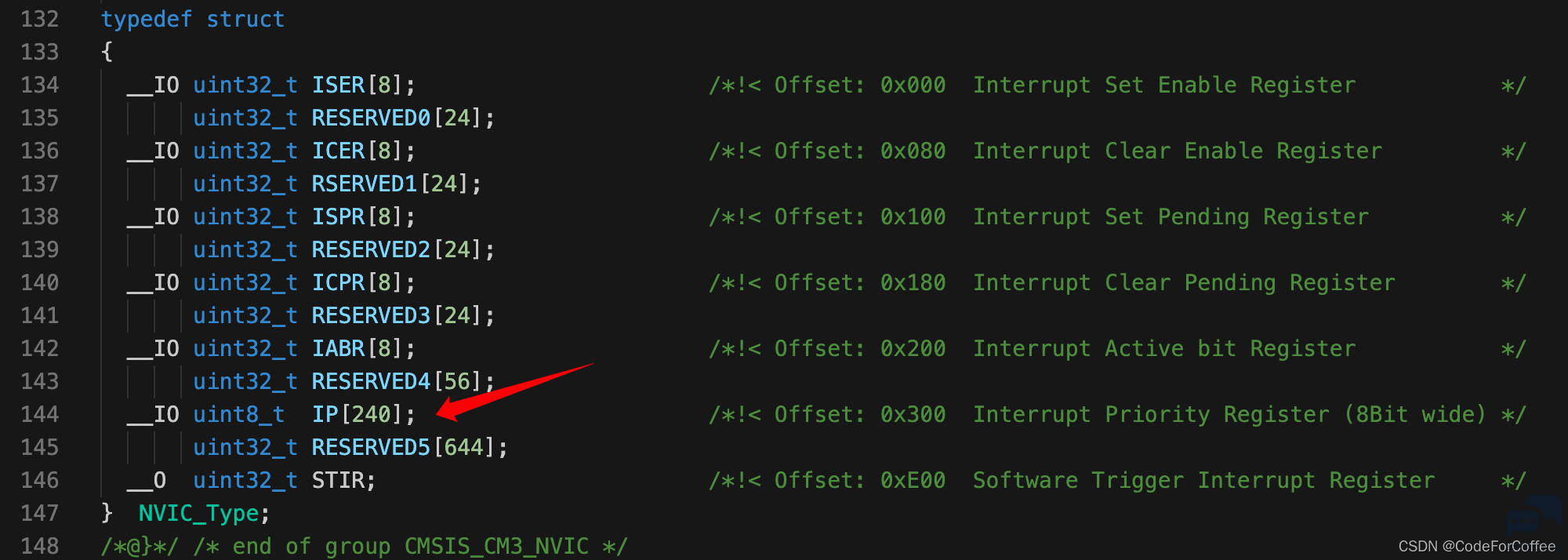

中断优先级设置寄存器 core_cm3.h

可以看到,有240个IP寄存器,即Interrupt Priority Register 240个8位寄存器,每个中断使用一个寄存器来确定优先级 STM32F10x系列一共60个可屏蔽中断,使用IP[59]~IP[0]

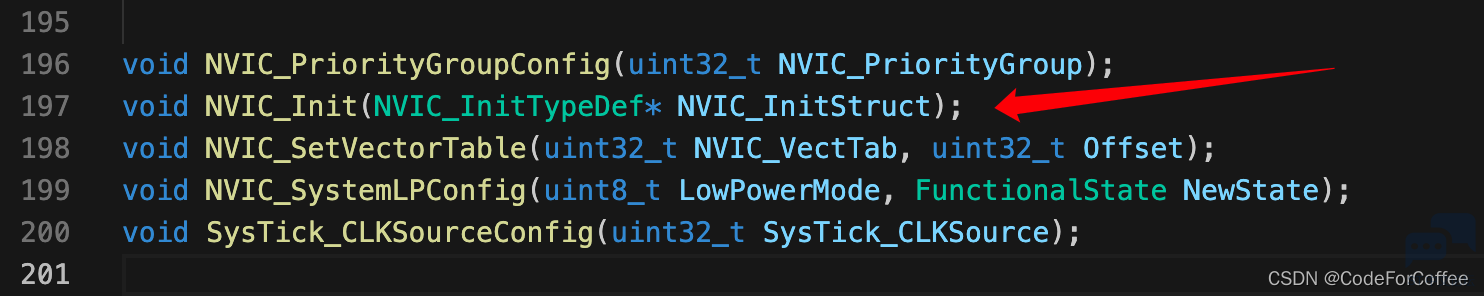

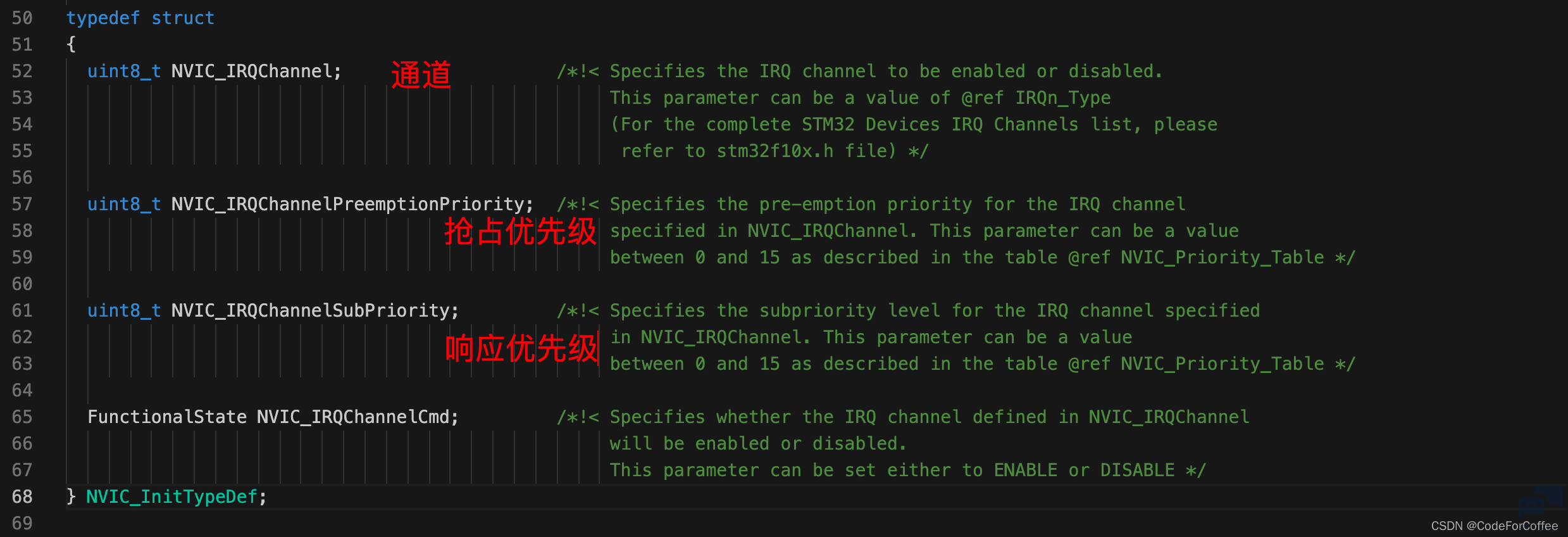

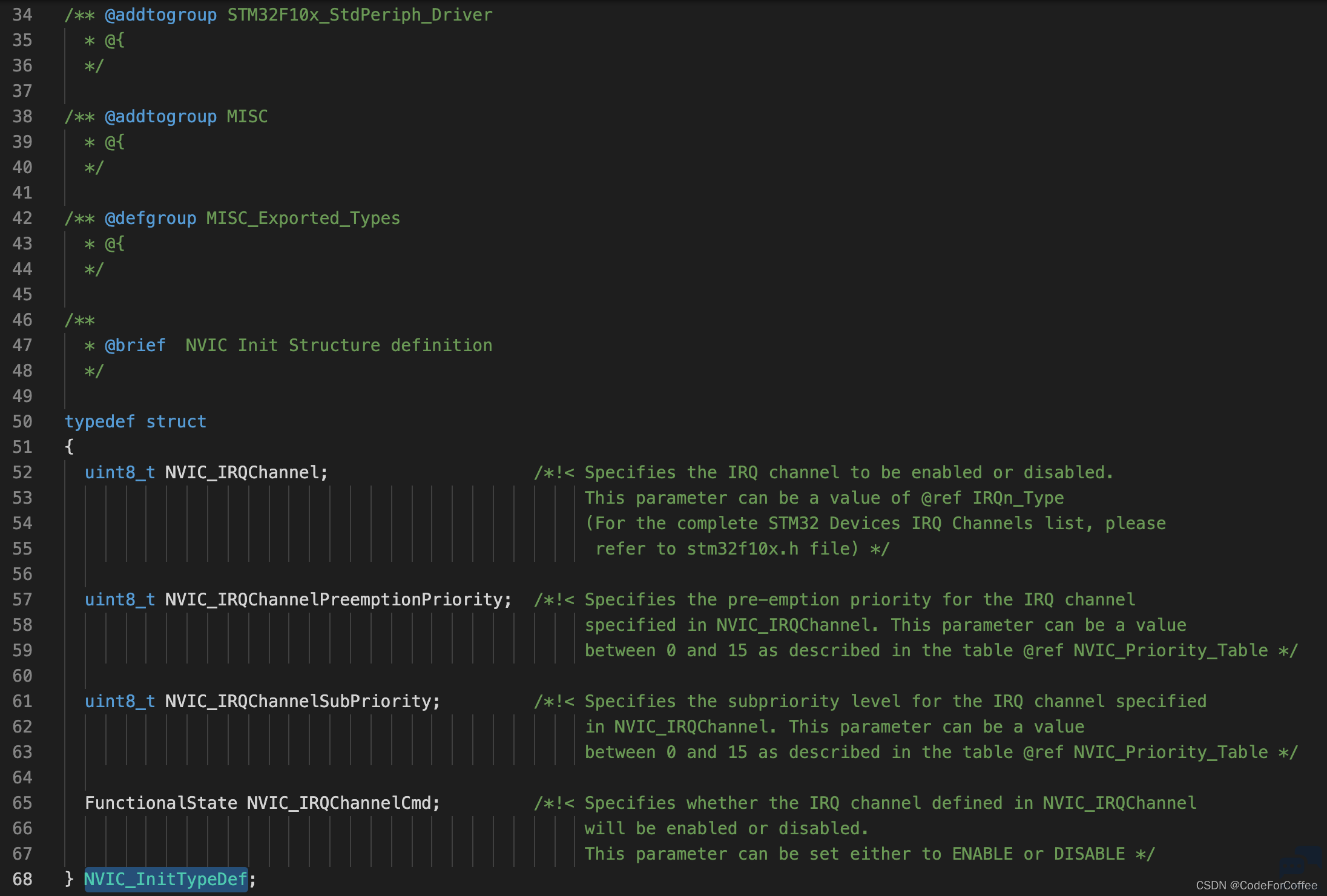

NVIC初始化 misc.c

misc.h

中断使能寄存器ISER寄存器 ISER[8]用于使能中断,共有8个32位寄存器 32位的寄存器,每个位控制一个中断的使能 STM32F10x只有60个可屏蔽中断,因此只能收了第1个和第2个寄存器,即ISER[0]和ISER[1] ISER[0]的bit 0~31分别对应中断0~31 ISER[1]的bit 0~27分别对应中断32~59 中断失能寄存器ICER寄存器 ICER[8] 其余上同 中断挂起控制寄存器ISPR ISPR[8]

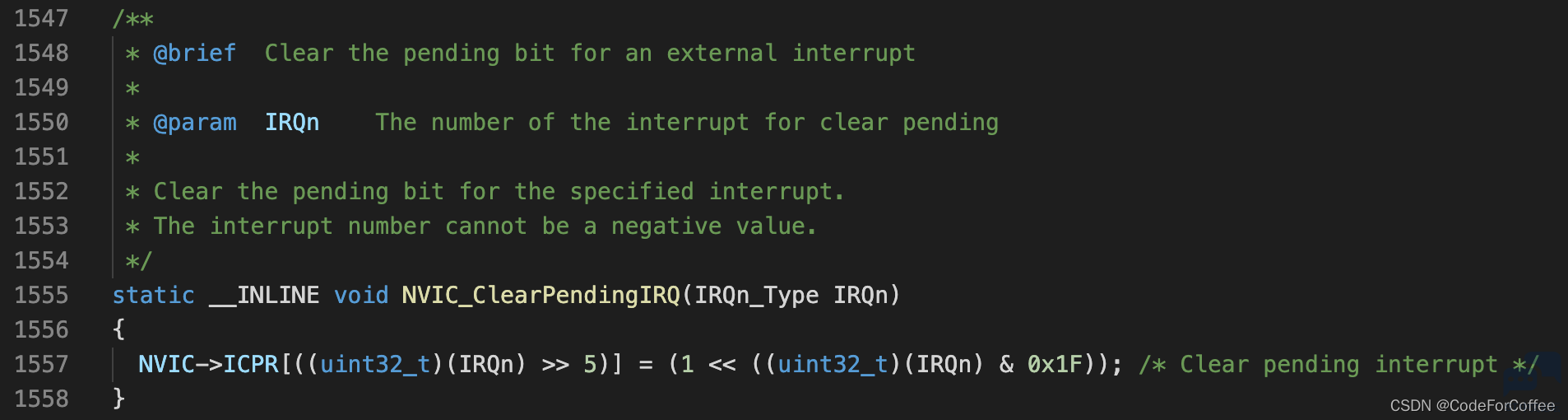

中断解挂控制寄存器ICPR ICPR[8]

中断激活标志位寄存器组IABR IABR[8] 只读,通过读取该寄存器可以知道当前执行的中断是哪一个,如果对应的位为1,则说明该中断正在执行

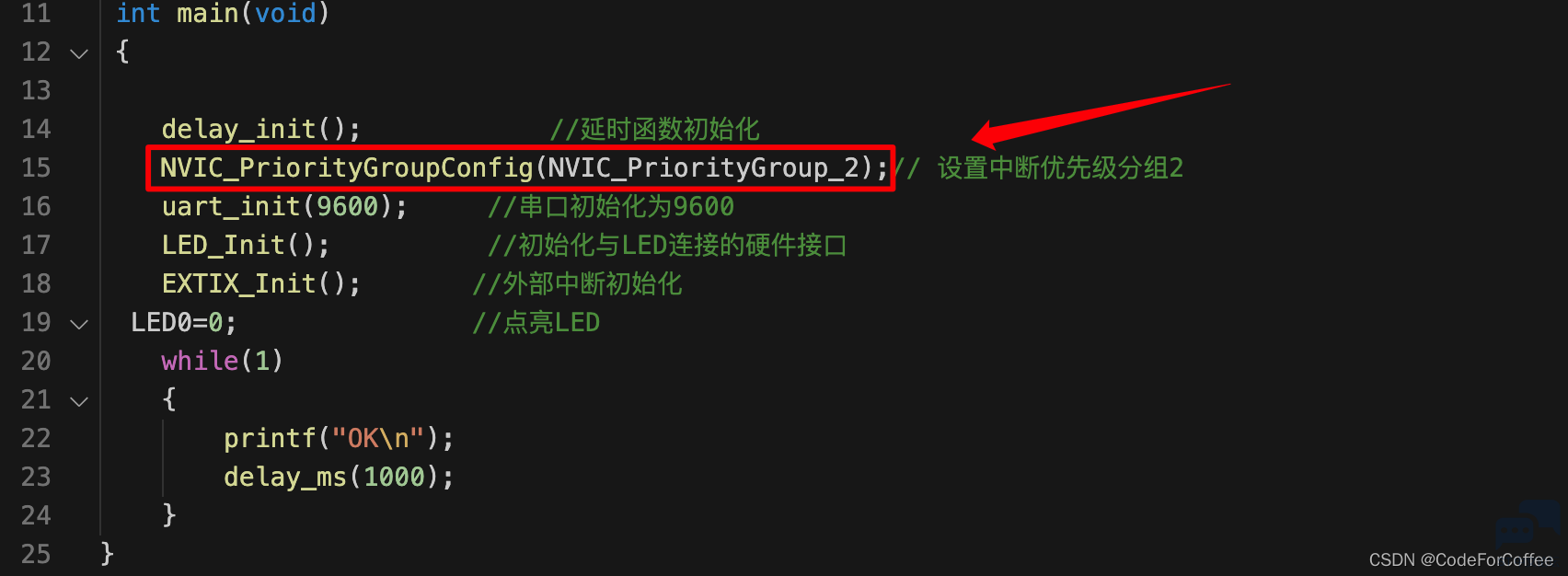

中断配置步骤总结 1. 首先设置中断优先级分组,确定系统的分组级别,知道有几位抢占优先级和几位响应优先级可以设置(这里只需要设置一次) 2. 针对每个中断,调NVIC_init函数,给定想要的抢占优先级和响应优先级,对中断进行设置 3. 如果需要挂起或解挂,查看中断当前的激活状态,调用相关函数即可 举例: main.c

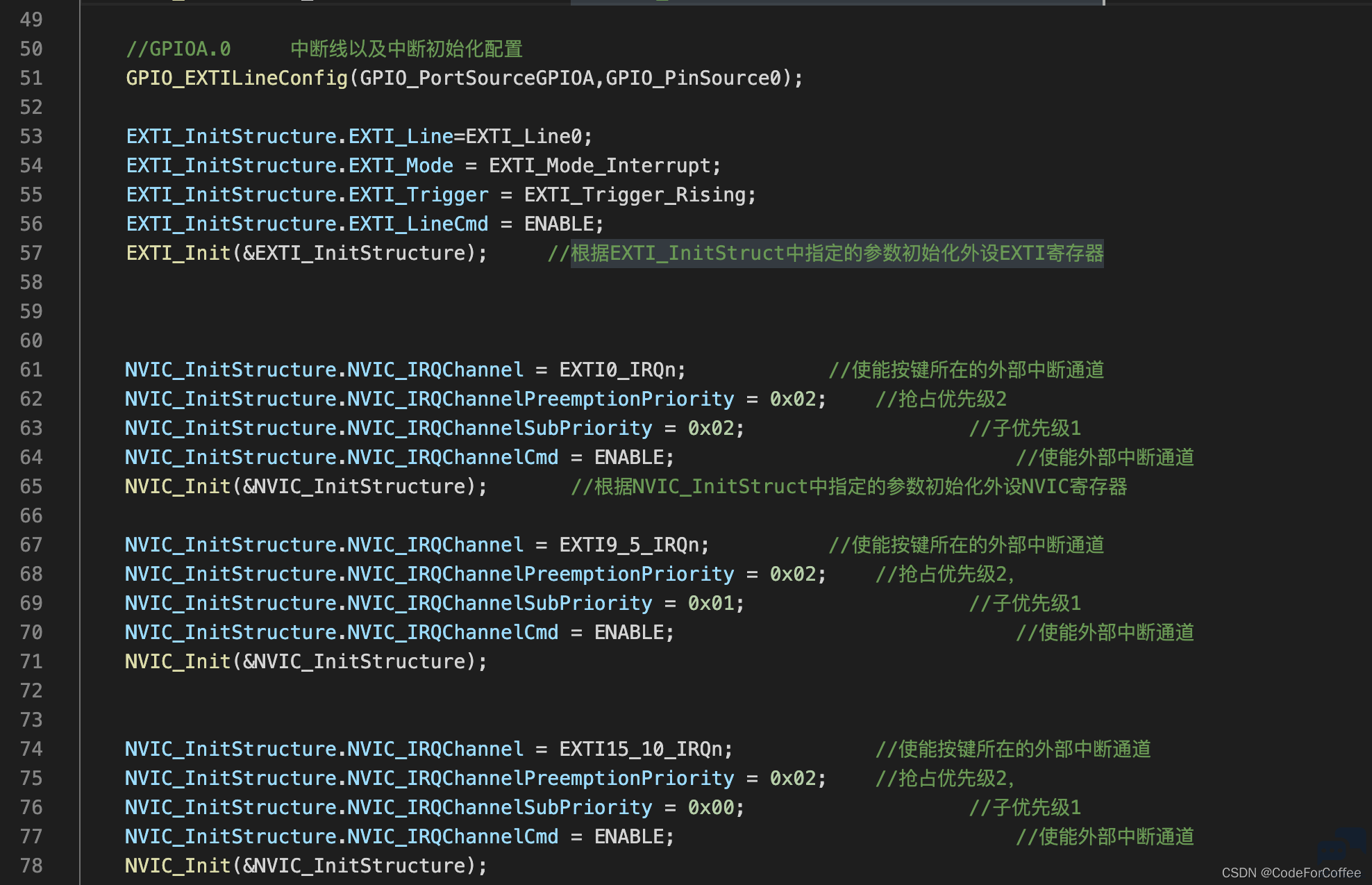

exit.c

———————————————— 版权声明:CodeForCoffee |

STM32中断响应延迟优化:从NVIC配置到DMA加速的极致性能调优

基于STM32串口中断之缓存区溢出卡死经验分享

基于STM32数组越界异常中断经验分享

基于STM32之数组越界异常中断经验分享

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32的定时器不按设定超时产生中断

基于STM32利用TIMER事件和栈帧体验中断响应经验分享

基于STM32外部中断原理和配置代码经验分享

基于stm32定时器定时中断经验分享

微信公众号

微信公众号

手机版

手机版