.png) STMCU小助手

发布时间:2022-12-29 17:00

STMCU小助手

发布时间:2022-12-29 17:00

|

STM32 NVIC与中断控制学习 NVIC全称向量中断控制器,NVIC 共支持 1 至 240 个外部中断输入(通常外部中断写作 IRQs)。NVIC 还支持一个“永垂不朽”的不可屏蔽中断(NMI)输入。NVIC 的访问地址是 0xE000_E000。所有 NVIC 的中断控制/状态寄存器都只能在特权级下访问。不过有一个例外——软件触发中断寄存器可以在用户级下访问以产生软件中断。所有的中断控制/状态寄存器均可按字/半字/字节的方式访问。此外,有几个中断屏蔽寄存器也与中断控制密切相关,它们是第三章中讲到的“特殊功能寄存器”,只能通过 MRS/MSR及 CPS 来访问。 中断配置基础 每个外部中断都在 NVIC 的下列寄存器中“挂号”: 使能与除能寄存器 悬起与“解悬”寄存器 优先级寄存器 活动状态寄存器 中断的使能与除能中断的使能与除能分别使用各自的寄存器来控制,CM3 中可以有 240 对使能位/除能位,每个中断拥有一对。这240 个对子分布在 8 对 32 位寄存器中(最后一对没有用完)。欲使能一个中断,你需要写 1 到对应 SETENA 的位中;欲除能一个中断,你需要写 1 到对应的 CLRENA 位中;如果往它们中写 0,不会有任何效果。通过这种方式,使能/除能中断时只需把“当事位”写成1,其它的位可以全部为零。再也不用像以前那样,害怕有些位被写入0 而破坏其对应的中断设置(写 0 没有效果),从而实现每个中断都可以自顾地设置,而互不侵犯——只需单一的写指令,不再需要读‐改‐写。如上所述,SETENA 位和 CLRENA 位可以有 240 对,对应的 32 位寄存器可以有8 对,因此使用数字后缀来区分这些寄存器,如 SETENA0, SETENA1…SETENA7,如表 8.1 所示。但是在特定的芯片中,只有该芯片实现的中断,其对应的位才有意义。因此,如果你使用的芯片支持 32 个中断,则只有SETENA0/CLRENA0 才需要使用。SETENA/CLRENA 可以按字/半字/字节的方式来访问。又因为前 16 个异常已经分配给系统异常,故而中断 0 的异常号是 16。

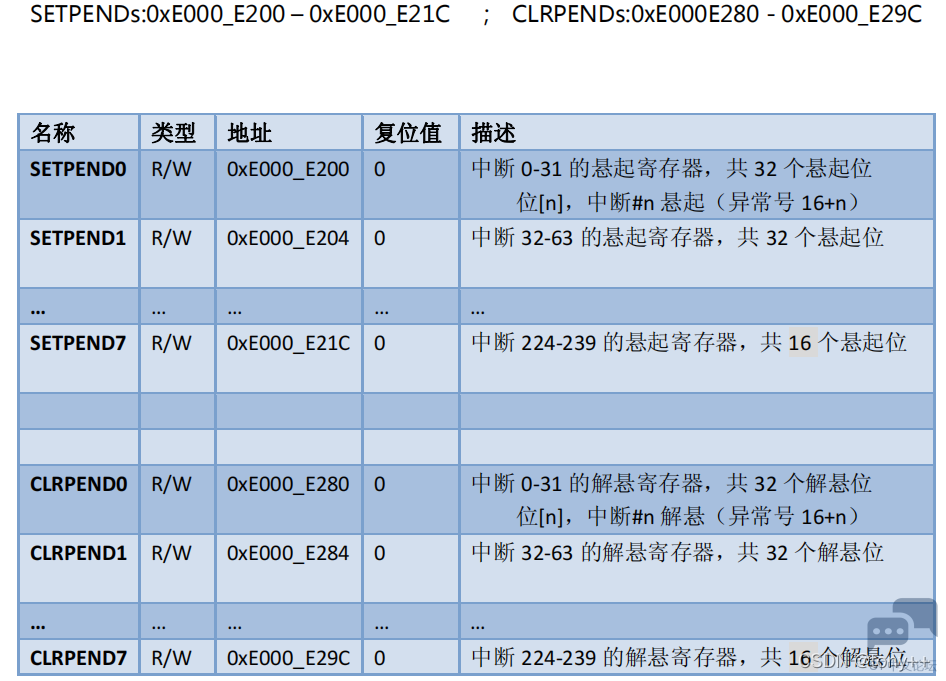

中断的悬起与解悬 如果中断发生时,正在处理同级或高优先级异常,或者被掩蔽,则中断不能立即得到响应。此时中断被悬起。 中断的悬起状态可以通过“中断设置悬起寄存器(SETPEND)”和“中断悬起清除寄存器(CLRPEND)”来读取,还可以写它们来手工悬起中断。悬起寄存器和“解悬”寄存器也可以有 8 对,其用法和用量都与前面介绍的使能/除能寄存器完全相同。

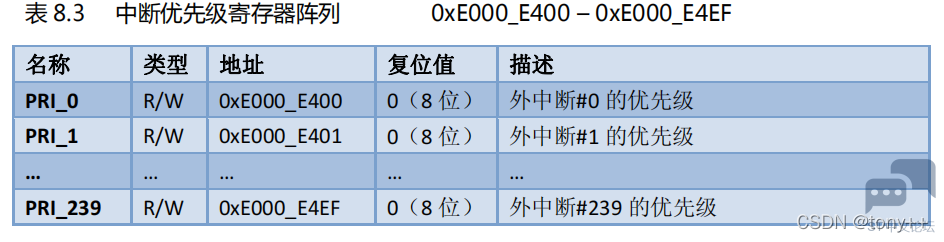

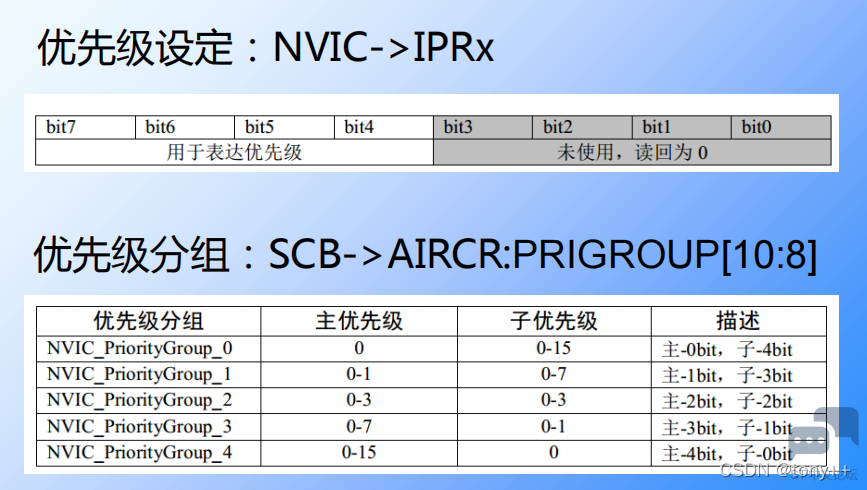

优先级 每个外部中断都有一个对应的优先级寄存器,每个寄存器占用 8 位,但是允许最少只使用最高 3 位。4 个相临的优先级寄存器拼成一个 32 位寄存器。如前所述,根据优先级组设置,优先级可以被分为高低两个位段,分别是抢占优先级和亚优先级。优先级寄存器都可以按字节访问,当然也可以按半字/字来访问。有意义的优先级寄存器数目由芯片厂商实现的中断数目决定。

活动状态 每个外部中断都有一个活动状态位。在处理器执行了其 ISR 的第一条指令后,它的活动位就被置 1,并且直到 ISR 返回时才硬件清零。由于支持嵌套,允许高优先级异常抢占某个ISR。然而,哪怕一个中断被抢占,其活动状态也依然为 1(请仔细琢磨前文讲到的“直到 ISR返回时才清零)。活动状态寄存器的定义,与前面讲的使能/除能和悬起/解悬寄存器相同,只是不再成对出现。它们也能按字/半字/字节访问,但他们是只读的。

这里提一下这个优先级分组,这个优先级分组寄存器SBC->AIRCR作用就是指定NVIC中抢占优先级和次优先级分别占几位,如果是grop1,那么就表示抢占优先级占1位,子优先级占3bit

两个重要的库文件:core_cm4.h和misc.c

以串口中断初始化例程说明:

所以总结流程如下: 1-使能中断请求 2-配置中断优先级分组(只需配置一次即可) 3-配置NVIC寄存器,初始化NVIC_InitTypeDef; 4-编写中断服务函数 ———————————————— 版权声明:tony++ |

STM32中断响应延迟优化:从NVIC配置到DMA加速的极致性能调优

基于STM32串口中断之缓存区溢出卡死经验分享

基于STM32数组越界异常中断经验分享

基于STM32之数组越界异常中断经验分享

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32连接参数更新进程后导致断连的问题分析

基于STM32的定时器不按设定超时产生中断

基于STM32利用TIMER事件和栈帧体验中断响应经验分享

基于STM32外部中断原理和配置代码经验分享

基于stm32定时器定时中断经验分享

微信公众号

微信公众号

手机版

手机版