.png) STMCU小助手

发布时间:2023-1-11 14:03

STMCU小助手

发布时间:2023-1-11 14:03

|

1.引言 在 STM32 MCU 中,ADC 有多种启动触发方式,本文对各种触发源的原理进行介绍,方便大家以后如何选择合适的触发源。 2. ADC 的架构与触发源 以 STM32G474 为例,ADC 模块的架构框图如下,基于逐次逼近原理(SAR)完成模拟量到数字量的转换。前端通过多通道选择开关(input selection)来对转换通道进行切换,从而实现对多个输入通道的信号进行采样。 ADC 模块的信道可以工作在规则模式或是注入模式下,对应的触发源分别为规则触发源与注入触发源。所有规则通道共享一个 ADC 结果寄存器,一个通道转换完成后需要及时读取转换结果,否则转换结果可能会被覆盖,具体取决于 overrun 的相关设置。

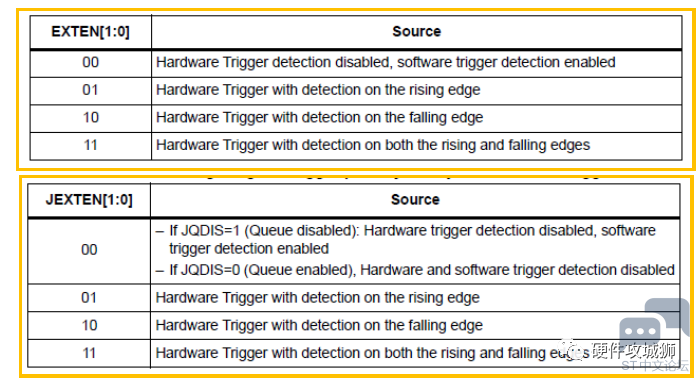

2.1. 各类触发源工作方式 ADC 的触发源整体上可以分为两类:软件触发与硬件触发。如下面两个表所示,EXTEN[1 :0]与 JEXTEN[1 :0]分别用于设定规则信道和注入信道的触发方式,当其值为 0 时,触发方式为软件触发,否则为硬件触发。

如果选择软件触发,那么当 ADSTART 或 JADSTART 被置位时,ADC 会立即启动转换。如果选择硬件触发,那么当 ADSTART 或 JADSTART 被置位后,要等待指定的外部事件发生时,ADC 才会启动转换。 对于硬件触发即外部事件触发来说,有多达 32 种外部事件可以选择,这些触发源大致可以分为以下四类,具体可以参考 RM 中关于adc_ext_trgx 和 adc_jext_trgx 的描述。 • 定时器的比较/捕获事件 • 定时器的触发输出 TRGO/TRGO2 • 高精度定时器的 ADC 触发 • 外部输入管脚 一个 ADC 单元可以选择多个硬件触发源,多个硬件触发源之间为“OR”的关系,即任何一个被选定的外部事件发生都可以触发 ADC 启动转换。 下面对几类触发源的工作方式进行介绍。 2.1.1. 定时器的比较/捕获事件 选用定时器的比较/捕获事件来触发 ADC 时,比如 TIM1_CC1,首先需要说明是虽从文档的描述来看比较事件与捕获事件都可以用来触发 ADC,但是实际中捕获事件是不能用来触发 ADC 的,只能使用比较事件,且需要结合触发源的上升沿与下降沿(见上表中的说明)的设置来设置TIM_CC1 的电平在比较事件点动作方式。比如设置通道电平在比较事件点由低电平变为高电平,即上升沿,那么在 ADC 触发源的沿选择上也需要选择上升沿,这样才能保证在正确的位置触发ADC 启动转换。 2.1.2. 定时器的触发输出 TRGO/TRGO2 TRGO 或是 TRGO2 来自于定时器的触发输出,可以选择的触发方式也比较多,如下 TRGO2的选择项:

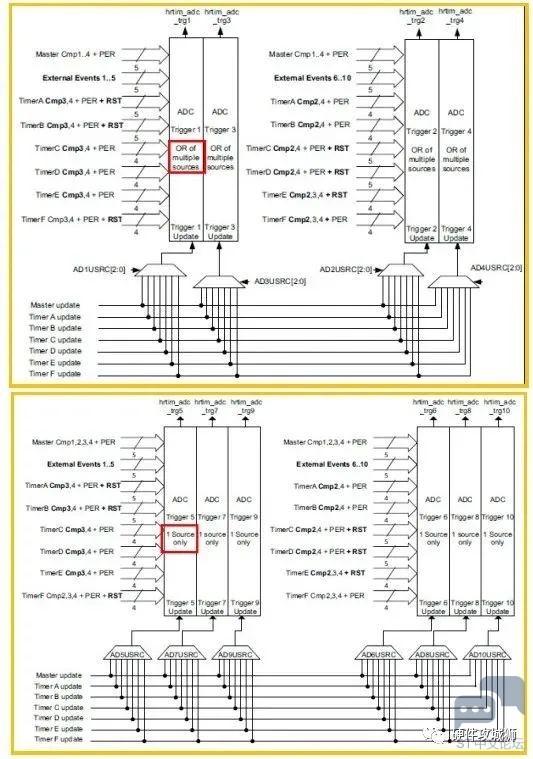

定时器的 Reset 事件、Enable 事件、Update 事件以及和 Compare 相关的事件都可以用来做TRGO2。这里以 TRGO2 为例对相关的事件进行简单说明。 • Reset/Enable/Update :定时器 Reset/Enable/Update 事件作为 TRGO2 输出,并触发ADC 转换,选择这几个事件时,可以忽略 ADC 触发源的沿方式的选择。 • Compare pulse:通道的捕获事件或是比较事件作为 TRGO2 输出,触发 ADC 转换,在up-down counting(Center-aligned mode)模式下,可以通过设定 CMS 位的值来确定比较事件是发生在向上计数阶段还是向下计数阶段,或是向上/向下都产生,此种方式下可以忽略ADC 触发源的沿方式的选择。 • Compare - tim_ocxrefc :定时器通道输出信号作为 TRGO2 输出,触发 ADC 转换,此种方式下,需要结合信道输出波形参考的沿与 ADC 触发源的沿方式来确定最终的 ADC 触发点。 • Compare Pulse - tim_ocxrefc:定时器通道输出波形参考指定的沿作为 TRGO2 输出,触发 ADC 转化,此种方式下可以忽略 ADC 触发源的沿方式的选择。 2.1.3. 高精度定时器的 ADC 触发 在高精度定时器中,包含了 10 个 ADC 触发输出,ADC Trigger 1 ~10,每个触发输出可以有多达 32 个触发事件可以选择。对于 ADC Trigger 1~4,可以同时选择多个触发事件(最多 32),多个触发事件之间为“OR”的关系,其中任意一个事件发生,都将产生 ADC 触发输出;对于 ADC Trigger 5~10,则只能选择其 32 个触发事件中的一个来产生触发输出。 另外,可以对高精度定时器中的 ADC 触发输出进行分频。高精度定时器的频率可以上 G,但是很多情况下 ADC 的采样速率并不需要那么高,通过对 ADC 触发输出进行分频可以降低 ADC 的采样速率,实现多个定时器周期才触发一次 ADC 采样。 选择高精度定时器的 ADC 触发方式时,可以忽略 ADC 触发源的沿方式的选择。

2.1.4. 外部输入管脚(EXIT LINE) 当选择的 EXIT LINE 对应的管脚电平出现上升沿或是下降沿时触发 ADC 转换,通过这种方式将 ADC 触发信号与 MCU 外部的信号关联起来,灵活的控制 ADC 转换。 该方式下需要对 ADC 触发源的沿方式的选择,以确定具体的触发时刻是发生在信号的上升沿或是下降沿。 小结 这里对 ADC 的架构进行了简单的介绍,重点说明了 ADC 的各种触发源和工作原理以及在实际选择中需要注意的事项。 转载自:硬件攻城狮 |

NUCLEO-G474RE 扩展 LSM6DSO 传感器数据融合实操演示全解析

经验分享 | STM32G474 高精度定时器同步功能全解析 从内部互联到多芯片协同的实现方案

经验分享 | STM32N6 ADC DMA 传输失败案例分享

经验分享 | STM32G4双BANK启动应用演示

STM32G4 LPTIM+DMAMUX 实现并行输出应用示例

实战经验 | LAT1578 SAU对NSC分区的影响

实战经验 | MC SDK V6.x软件HSO功能ADC采样设计说明

经验分享 | STM32G474 HRTIM Triggered-half模式实现两相交错电源180°相位同步方案

STM32大神笔记,超详细单片机学习汇总资料

经验分享 | 为什么重启ADC的DMA传输要先停掉ADC?

微信公众号

微信公众号

手机版

手机版