.png) STMCU小助手

发布时间:2023-2-2 18:21

STMCU小助手

发布时间:2023-2-2 18:21

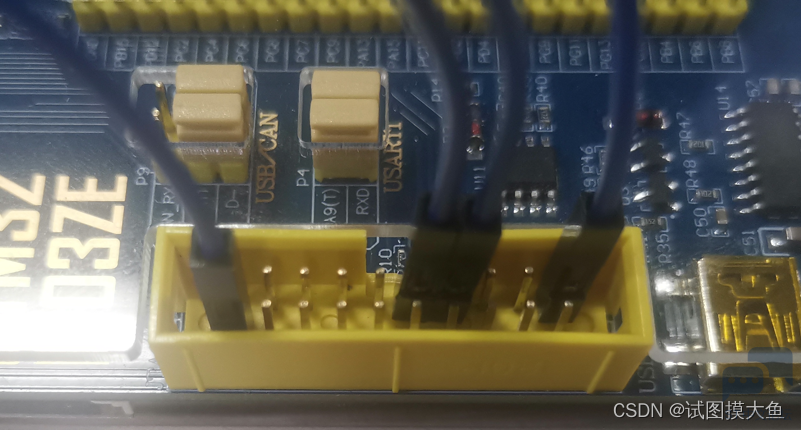

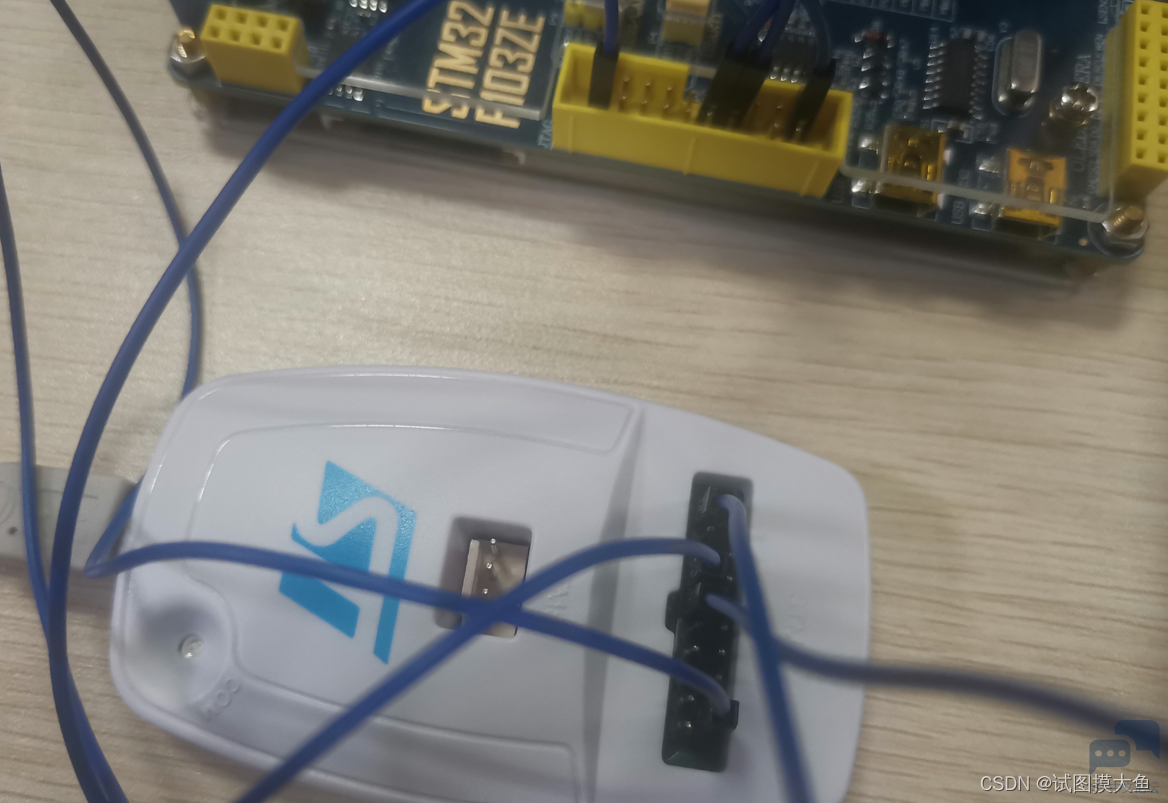

ST-LINK/V2实物图和STM32板子上的接口

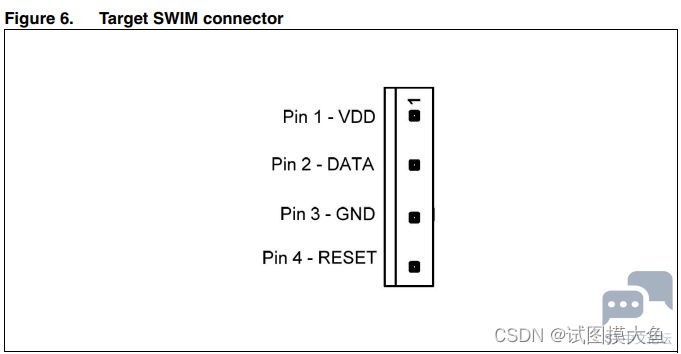

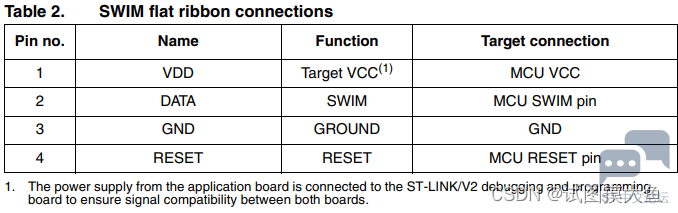

下面是相关知识和我的理解,可能会有错误,直接指出即可 如果不想继续看只想知道STM32的SWD接法需要接哪几个引脚,先说明,必接第1、7、9、20脚,如果需要供电再加上第19脚 好的,然后接着仔细说 ST-LINK/V2实物图中,上面的4脚SWIM接口是用来连接STM8的,引脚分布和作用如下,截图自ST-LINK/V2用户使用手册,STM8的不进行分析

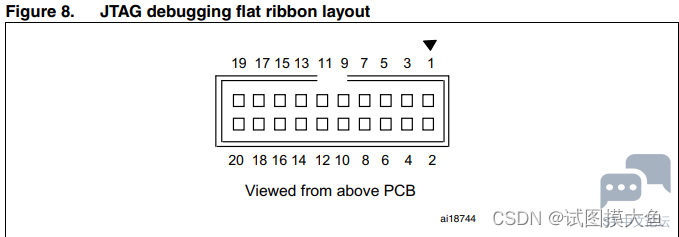

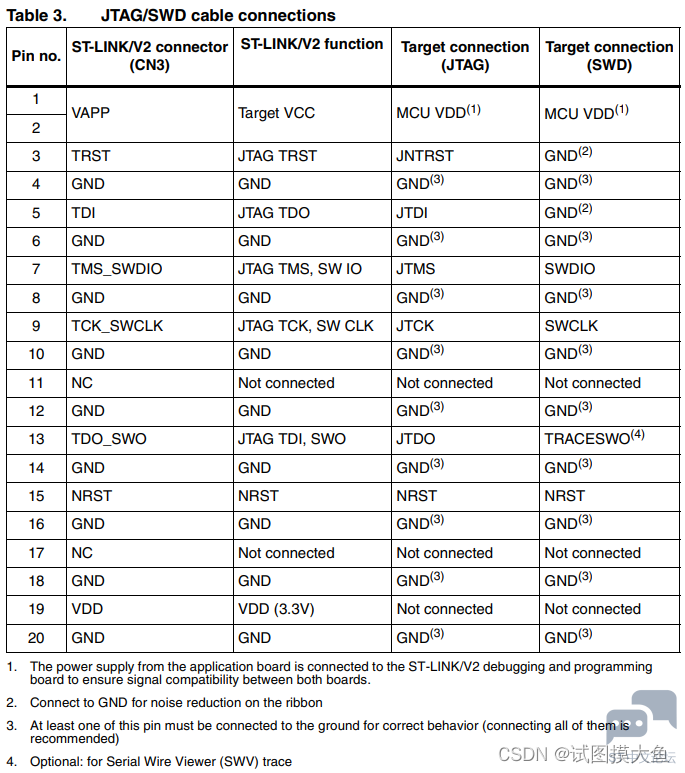

ST-LINK/V2实物图中,下面的20脚JTAG接口是用来连接STM32的,引脚分布和作用如下,截图自ST-LINK/V2用户使用手册

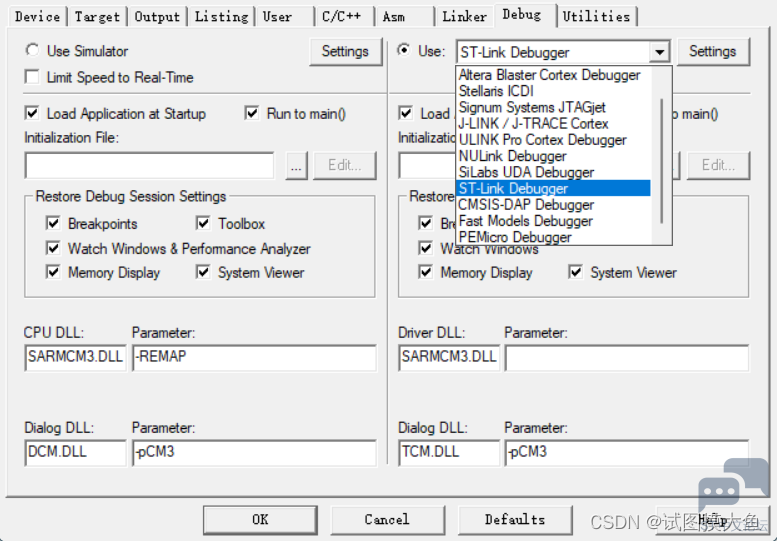

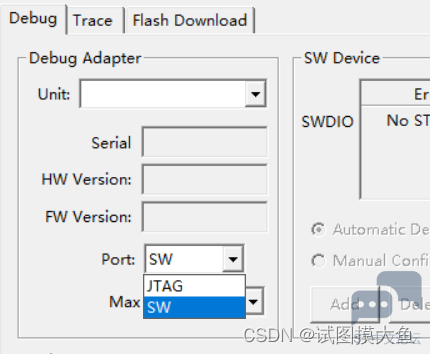

JTAG接法有20脚呢,如何判断是第几脚呢?从用户手册的截图和实物图都可以看出来一长边侧的中间有一缺口,就是以中间的缺口判断方向的,这个缺口朝上,左边的就是第11脚,右边的就是第9脚,判断出来两个之后,其他就很好判断了 所以在本文一开始的图片,就把有缺口侧朝上了,以方便对应引脚 Keil5中的Debug选择ST-Link Debugger,点击Settings,然后点击Port,可以看到有两种连接方式

JTAG JTAG连接方式,共20脚,直接对应连接即可,实物图如下

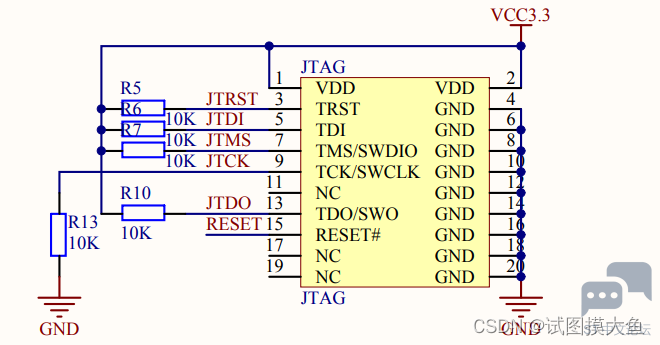

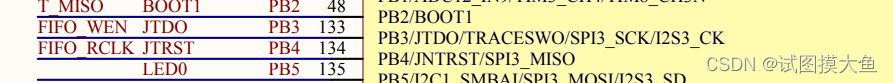

既然都看到这里了,不如更加深入的看一下,这个JTAG是怎么和芯片引脚连接的呢,找到原理图,是STM32F103ZET6,正点原子的板子 JTAG的原理图

到了“喜闻乐见”的对着图找引脚环节 没有标接到芯片名字的1、2脚接电源,11、17、19脚不接,4、6、8、10、12、14、16、18、20接地,剩下几个脚就去找吧 JTRST(3脚TRST)接PB4(134脚),JTDO(13脚TDO/SWO)接PB3(133脚)

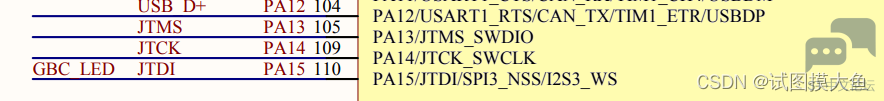

JTDI(5脚TDI)接PA15(110脚),JTMS(7脚TMS)接PA13(105脚),JTCK(9脚TCK)接PA14(109脚)

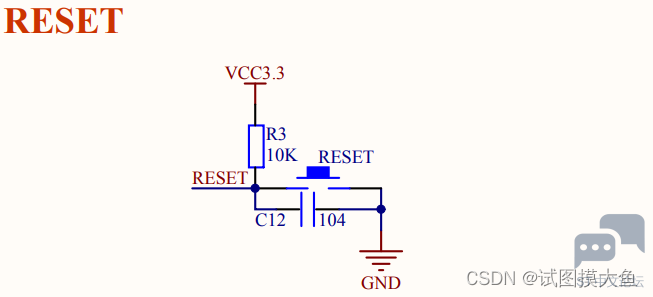

RESET(15脚)和芯片上的NRST(25脚)一样直接接到复位电路上

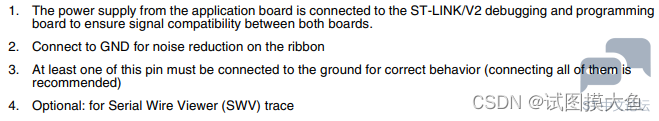

由于JTAG需要20脚,所以有的板子为了节省空间或引脚等原因,而采用SW连接方式 SW SW连接方式,一般来说需要4脚,分别是VCC(第1脚),SWIO(第7脚),SWCLK(第9脚),GND(第20脚),如果需要使用ST-Link供电,则需要多连接VDD(第19脚),其实在用户手册中的第3点,也说明了那么就算是JTAG多个接地脚其实接一个就可以了,不过官方建议全接上

实物连接图

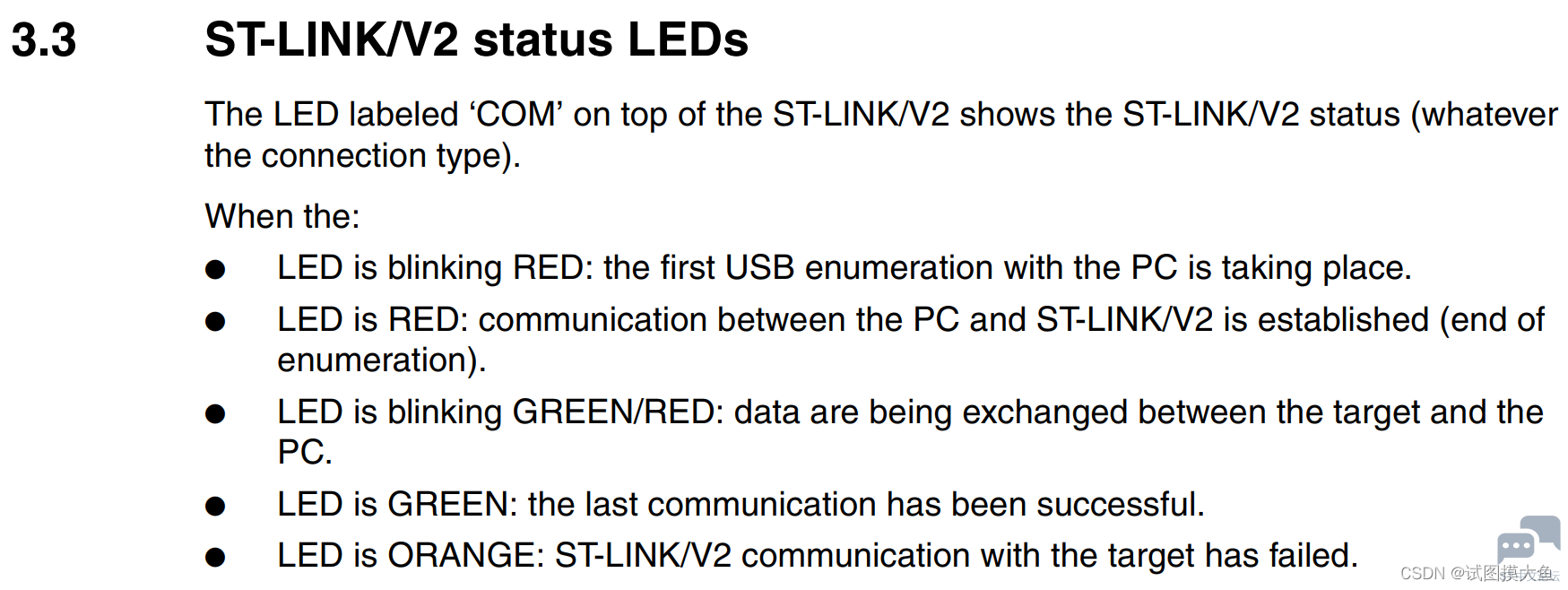

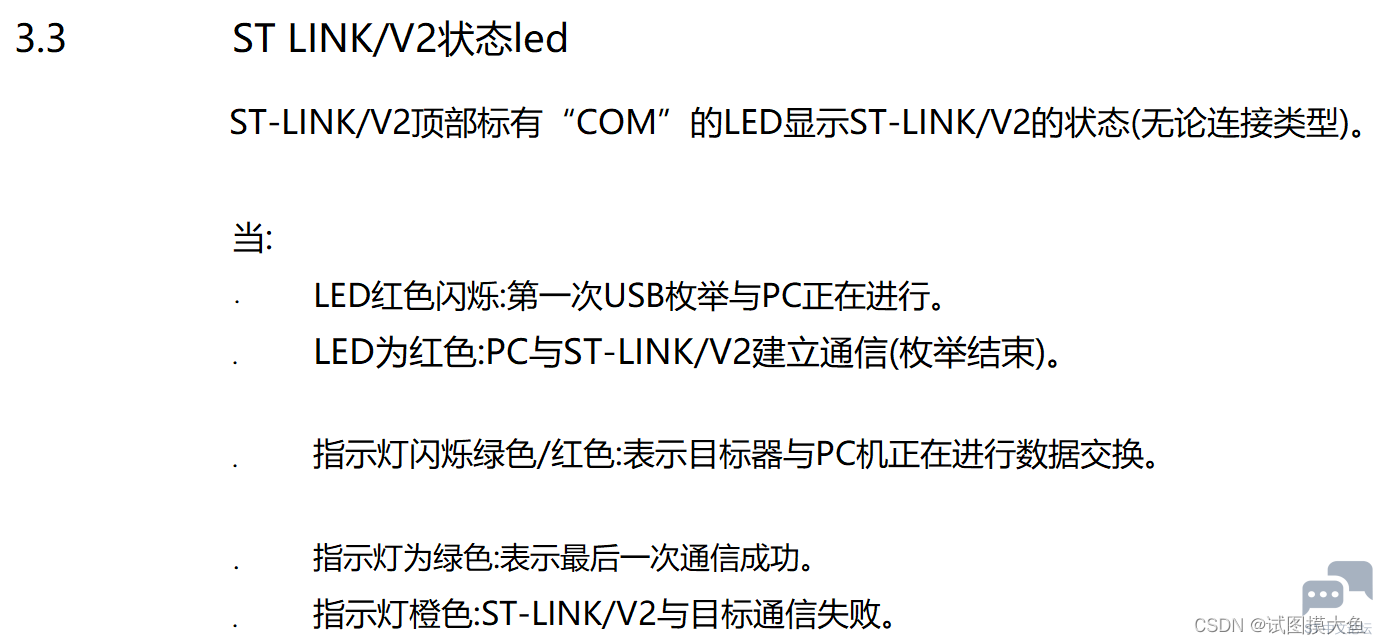

还是STM32F103ZET6,正点原子的板子,再看一下JTAG的原理图 然后发现一共接着的4个脚,1脚接电源,20脚接地,就还剩下7、9两脚 JTMS(7脚TMS)接PA13(105脚),JTCK(9脚TCK)接PA14(109脚) 这样就看完了两种连接方式,除此之外,我们可以看到ST-LINK/V2实物图中左上角有个LED灯,这个灯会以不同方式亮 LED灯 再看一眼ST-LINK/V2实物图

ST-LINK/V2用户手册里也写了LED亮的方式反映出来的信息

由于英语不好,所以机翻一下,将就理解一下就好

———————————————— 版权声明:试图摸大鱼 |

兔哥的L4【001】——32脚的小板

拷打cubemx【001】——艰难的选型路

汇编浮点库qfplib移植STM32F769I-DISCO开发板与硬件浮点运算性能测试对比

【STM32H7S78-DK评测】CoreMark移植和优化--兼记printf重定向实现方法及常见问题

【STM32H7S78-DK评测】移植AI框架TensorFlow【DSP指令加速篇】

【STM32H7S78-DK评测】开发板初识与工程模板创建

【STM32H7S78-DK评测】搭建基于ST官方VSCode扩展的STM32开发环境

[STM32WB55评测] 开箱

通过 STLINK-V3SET I2C 接口将程序下载到 SRAM 中并执行的方法

ST IO-Link 从站执行器设计方案

微信公众号

微信公众号

手机版

手机版