.png) STMCU小助手

发布时间:2022-2-22 20:34

STMCU小助手

发布时间:2022-2-22 20:34

|

问题: 该问题由某客户提出,发生在 STM32F103VDT6 器件上。据其工程师讲述:在其产品中,需要使用STM32 的 ADC 对多路模拟信号进行同步采样。在具体的实现上,采用了 ADC 常规通道的扫描模式来完成这一功能。然而,在调试中过程中发现一个奇怪的现象:当将各路模拟信号的电平设置成相同时,ADC 对各路模拟信号的转换结果相同,用 A 来表示。改变其中一路模拟信号的电平,并保持其各路模拟信号的电平不变,则 ADC 对该路信号的转换结果变为 B。然而,此时与其在扫描次序上相邻的下一路模拟信号的转换结果也发生了变化,记作 C。经多次实验发现,B 和 C 在数值上相对于 A 有相同的变化方向。于是,怀疑 ADC 的相邻通道间存在着某种串扰。 调研: 重复试验,确认现象如其所述。检查其硬件设计,在与 VDD、VDDA、VSS、VSSA、Vref+、Vref-相关的电路中未发现异常。修改软件,增大 ADC 各个通道的采样保持时间 Ts 。重新测试,发现 C 相对于 A的变化量有所减小。进一步增大 ADC 各个通道的采样保持时间 Ts,发现 C 相对 A 的变化量进一步减小。 结论: 对 ADC 所设置的采样保持时间 Ts偏小,导致相邻通道之间透过采样电容发生了藕合。 处理: 根据公式: ![C(H8K]571_~5S(YBN_Q1~2Y.png C(H8K]571_~5S(YBN_Q1~2Y.png](data/attachment/forum/202202/22/203550f0ffsfshzffshi0d.png)

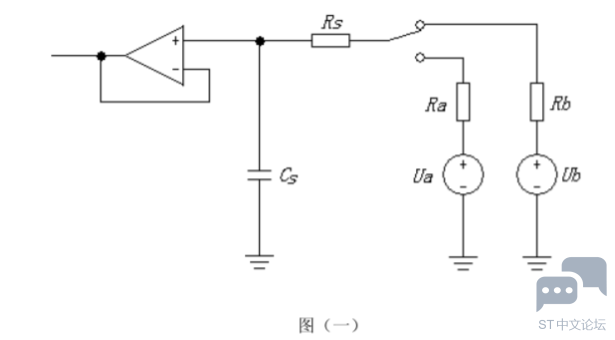

由该公式计算出的采样保持时间 Ts,可以保证采样电容上的采样值,相对于信号源的电平的偏差不大于 1/4LSB。 建议: 当 ADC 的采样电容在两个通道之间进行切换时,其电路如图(一)所示:

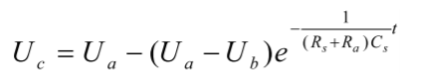

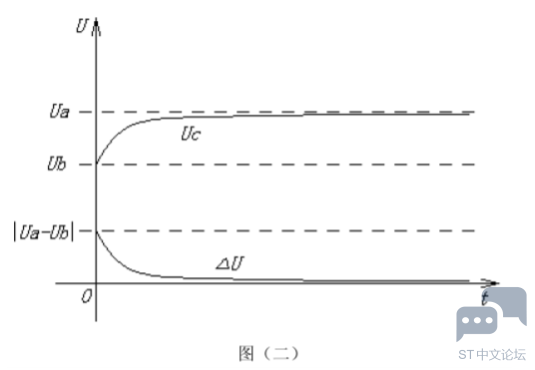

其中, Cs 是 ADC 的采样电容,Rs 是 ADC 的采样电阻。两路信号源 A 和 B 的电平分别为 Ua 和 Ub,其内阻分别是 Ra 和 Rb。为了简化问题,假定两路信号的扫描次序是由信号源 B 到信号源 A,且信号源B 接入的时间足够长,以至在通道切换时采样电容 Cs 上的电压可以近似的等于 Ub ,于是,在通道切换到信号源 A 后,采样电容 Cs 上的电压将按如下曲线变化:

随着时采样保持时间 t 的增长,采样电容 Cs 上的电压逐渐趋近于 Ua ,而其与 Ua 之间的误差为: ![N@_IEAU3IRKJF})A]ZC5K{O.png N@_IEAU3IRKJF})A]ZC5K{O.png](data/attachment/forum/202202/22/203550khrt5y8er6yberhr.png)

该误差 ![(YQ[I3RPE{3D%Q`QE0]G7.png (YQ[I3RPE{3D%Q`QE0]G7.png](data/attachment/forum/202202/22/203717wobajj9g8fgca8pa.png)

1. 通过增加采样保持时间 t,使 获得更多的衰减时间; 2. 通过减小信号源的内阻 Ra,使 具有更快的衰减速率;

以上两点可以作为消除 ADC 不同通道之间通过采样电容 Cs 产生寄生藕合的理论依据。在实际运用时,在增加采样保持时间方面可以通过修改 ADC 的设置参数来实现,而在降低信号源内阻方面可以通过在信号源与 ADC 之间加入跟随器进行隔离来实现。 |

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

微信公众号

微信公众号

手机版

手机版