.png) STMCU小助手

发布时间:2022-5-9 19:00

STMCU小助手

发布时间:2022-5-9 19:00

|

前言 使用中断前,需了解中断优先级管理, CM3 内核支持 256 个中断,其中包含了 16 个内核中断和 240 个外部中断,并且具有 256 级的可编程中断设置。但 STM32 并没有使用 CM3 内核的全部东西,而是只用了它的一部分。 STM32 有 84 个中断,包括 16 个内核中断和 68 个可屏蔽中断,具有 16 级可编程的中断优先级。 而我们常用的就是这 68 个可屏蔽中断,但是 STM32 的 68 个可屏蔽中断,在 STM32F103 系列 上面,又只有 60 个(在 107 系列才有 68 个)。因为我们开发板选择的芯片是 STM32F103 系列 的所以我们就只针对 STM32F103 系列这 60 个可屏蔽中断进行介绍。 一、STM32 NVIC 中断优先级管理 在 MDK 内,与 NVIC 相关的寄存器,MDK 为其定义了如下的结构体:

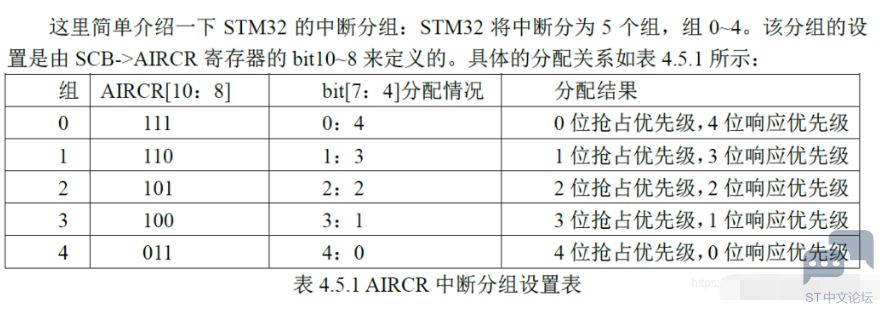

ISER[8]: 中断使能寄存器组,使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能,配合中断分组、屏蔽、IO 口映射等设置。 ICER[8]: 中断除能寄存器组,用来清除某个中断的使能。 ISPR[8]: 中断挂起控制寄存器组,通过置 1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写 0 是无效的。 ICPR[8]: 中断解挂控制寄存器组,通过设置 1,可以将挂起的中断接挂。写 0 无效。 IABR[8]: 中断激活标志位寄存器组 IP[240]: 中断优先级控制的寄存器组,由 240 个 8bit 的寄存器组成,每个可屏蔽中断占用 8bit,240 个可屏蔽中断。只用了高 4 位,这 4 位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。 二、STM32 的中断分组 STM32 将中断分为 5 个组,组 0~4。该分组的设置是由 SCB->AIRCR 寄存器的 bit10~8 来定义的。

每个中断,你可以设置抢占优先级为 0~7,响应优先级为 1 或 0。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。 这里需要注意两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。 中断优先级分组函数 NVIC_PriorityGroupConfig void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup); 这个函数的作用是对中断的优先级进行分组,这个函数在系统中只能被调用一次,一旦分 组确定就最好不要更改。

分组范围为 0-4 中断初始化函数 NVIC_Init

NVIC_InitTypeDef 是一个结构体

NVIC_InitTypeDef 结构体中间有三个成员变量,这三个成员变量的作用是: NVIC_IRQChannel:定义初始化的是哪个中断,这个我们可以在 stm32f10x.h 中找到每个中断对应的名字。 例如 USART1_IRQn。 NVIC_IRQChannelPreemptionPriority:定义这个中断的抢占优先级别。 NVIC_IRQChannelSubPriority:定义这个中断的子优先级别。 NVIC_IRQChannelCmd:该中断是否使能。 中断优先级设置的步骤: 系统运行开始的时候设置中断分组。确定组号,也就是确定抢占优先级和子优先级的 分配位数。调用函数为 NVIC_PriorityGroupConfig(); 设置所用到的中断的中断优先级别。对每个中断调用函数为 NVIC_Init(); |

实战经验 | Keil工程使用NEAI库的异常问题

经验分享 | FDCAN数据段波特率增加后发送失败的问题分析

STM32几种流行开发环境的优缺点

好用软件推荐-TouchGFX Designer

OpenSTLinux 6.1发布:M33-TD加持+安全升级,STM32MPU开发效率翻倍!

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

微信公众号

微信公众号

手机版

手机版