.png) STMCU小助手

发布时间:2022-6-14 13:44

STMCU小助手

发布时间:2022-6-14 13:44

|

01. FSMC简介 STM32F407 或 STM32F417 系列芯片都带有 FSMC 接口,ALIENTEK 探索者 STM32F4 开发板的主芯片为 STM32F407ZGT6,是带有 FSMC 接口的。 FSMC,即灵活的静态存储控制器,能够与同步或异步存储器和 16 位 PC 存储器卡连接,STM32F4 的 FSMC 接口支持包括 SRAM、NAND FLASH、NOR FLASH 和 PSRAM 等存储器。 02. FSMC主要特性 FSMC 能够连接同步、异步存储器和 16 位 PC 存储卡。其主要用途如下: ● 将 AHB 数据通信事务转换为适当的外部器件协议 ● 满足外部器件的访问时序要求 所有外部存储器共享地址、数据和控制信号,但有各自的片选信号。FSMC 一次只能访问一个外部器件。 FSMC 具有以下主要功能: ● 连接静态存储器映射的器件: — 静态随机访问存储器 (SRAM) — 只读存储器 (ROM) — NOR Flash/OneNAND Flash — PSRAM(4 个存储区域) ● 两个带有 ECC 硬件的 NAND Flash 存储区域,可检查多达 8 KB 的数据 ● 16 位 PC 卡兼容设备 ● 支持对同步器件(NOR Flash 和 PSRAM)的突发模式访问 ● 8 或 16 位宽的数据总线 ● 每个存储区域有独立的片选控制 ● 每个存储区域可独立配置 ● 可对时序进行编程,以支持各种器件,尤其是: — 等待周期可编程(最多 15 个时钟周期) — 总线周转周期可编程(最多 15 个时钟周期) — 输出使能和写入使能延迟可编程(最多 15 个时钟周期) — 独立的读和写时序和协议,以支持各种存储器和时序 ● 写使能和字节通道选择输出,可配合 PSRAM 和 SRAM 器件使用 ● 将 32 位的 AHB 事务转换为针对外部 16 位或 8 位器件进行的连续 16 位或 8 位访问。 ● 用于写入的 FIFO,2 字长(对于 STM32F42x 和 STM32F43x,为 16 字长),每个字为32 位宽,仅用于存储数据,而不存储地址。因此,此 FIFO 仅会缓冲 AHB 批量写事务。从而可对慢速存储器执行写入操作后能快速释放 AHB,以供其它操作使用。每次仅缓冲一个突发事务:如果在有操作正在进行时发生一个新的 AHB 突发事务或者一个单独事务,则 FIFO 将会清空。FSMC 将插入等待周期,直至当前存储器访问已完成)。 ● 外部异步等待控制 定义外部器件类型和其特性的 FSMC 寄存器通常在启动时进行设置,并且在下次上电或复位前保持不变。但也可随时更改这些设置。 03. FSMC框图 FSMC 包含四个主要模块: ● AHB 接口(包括 FSMC 配置寄存器) ● NOR Flash/PSRAM 控制器 ● NAND Flash/PC 卡控制器 ● 外部器件接口 ![BOAP}1ERW4E9LD8]DY5K6{G.png BOAP}1ERW4E9LD8]DY5K6{G.png](data/attachment/forum/202206/14/134447rcnatdf7fhgazfbc.png)

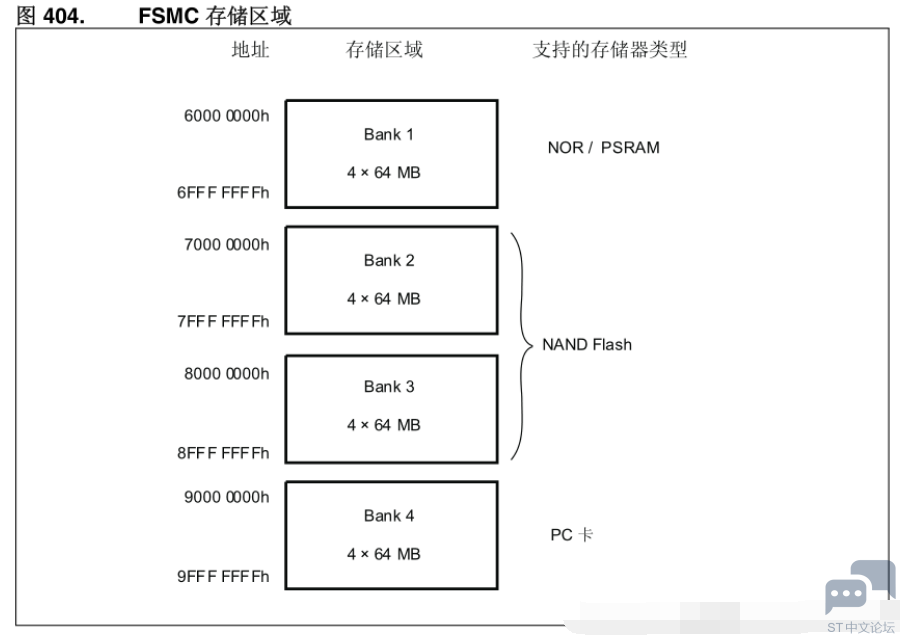

04. 外部器件地址映射 从 FSMC 的角度,外部存储器被划分为 4 个固定大小的存储区域,每个存储区域的大小为256 MB: ● 存储区域 1 可连接多达 4 个 NOR Flash 或 PSRAM 存储器器件。此存储区域被划分为 4 个NOR/PSRAM 区域,带 4 个专用片选信号。 ● 存储区域 2 和 3 用于连接 NAND Flash 器件(每个存储区域一个器件) ● 存储区域 4 用于连接 PC 卡设备 对于每个存储区域,所要使用的存储器类型由用户在配置寄存器中定义。

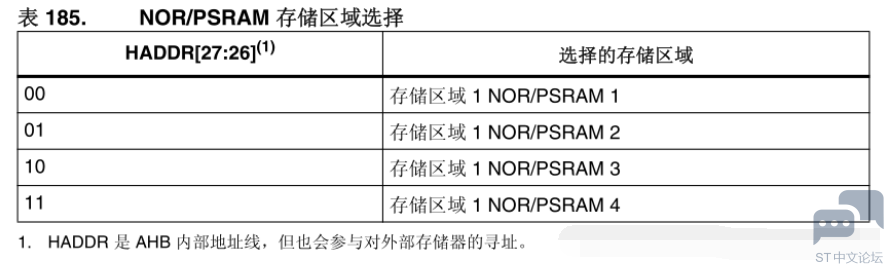

4.1 NOR/PSRAM地址映射 HADDR[27:26] 位用于从 表 185 中所示的四个存储区域之中选择其中一个存储区域。

HADDR[25:0] 包含外部存储器地址。由于 HADDR 为字节地址,而存储器按字寻址,所以根据存储器数据宽度不同,实际向存储器发送的地址也将有所不同,如下表所示。 ![[P2[D1N_@LG]P$~F@L`P]YM.png [P2[D1N_@LG]P$~F@L`P]YM.png](data/attachment/forum/202206/14/134447q3c191n3v701t1t1.png)

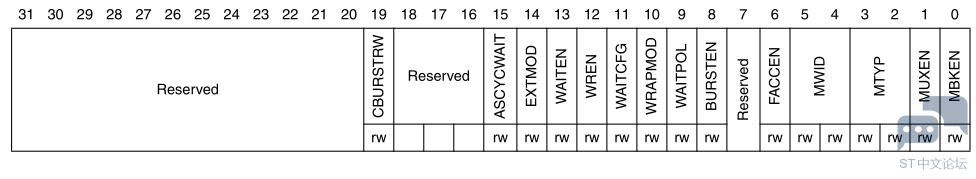

4.2 NOR Flash/PSRAM控制器 FSMC 会生成适当的信号时序,以驱动以下类型的存储器: ● 异步 SRAM 和 ROM — 8 位 — 16 位 — 32 位 ● PSRAM(Cellular RAM) — 异步模式 — 突发模式 — 复用或非复用 ● NOR Flash — 异步模式或突发模式 — 复用或非复用 FSMC 会为每个存储区域输出唯一的片选信号 NE[4:1]。所有其它信号(地址、数据和控制)均为共享信号。 对于同步访问,FSMC 只有在读/写事务期间才会向所选的外部器件发出时钟 (CLK)。HCLK时钟频率是该时钟的整数倍。每个存储区域的大小固定,均为 64 MB。 每个存储区域都通过专用的寄存器进行配置(请参见 第 32.5.6 节 )。 存储器的可编程参数包括访问时序(请参见 表 189)和对等待管理的支持(用于在突发模式下访问 NOR Flash 和 PSRAM)。 05. 寄存器描述 5.1 SRAM/NOR-Flash 片选控制寄存器 1…4 (FSMC_BCR1…4) SRAM/NOR-Flash chip-select control registers 1…4 偏移地址:0xA000 0000 + 8 * (x — 1),x = 1…4 复位值:0x0000 30DX 该寄存器包含每个存储区域的控制信息,用于 SRAM、ROM 和异步或突发 NOR Flash。

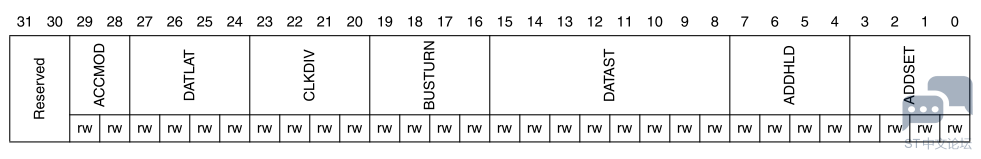

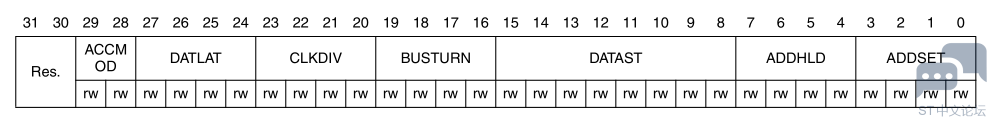

5.2 SRAM/NOR-Flash 片选时序寄存器 1…4 (FSMC_BTR1…4) SRAM/NOR-Flash chip-select timing registers 1…4 偏移地址:0xA000 0000 + 0x04 + 8 * (x — 1),x = 1…4 复位值:0x0FFF FFFF 该寄存器包含每个存储区域的控制信息,用于 SRAM、ROM 和 NOR Flash。如果FSMC_BCRx 寄存器中的 EXTMOD 位置 1,该寄存器将和另外一个寄存器配合来配置写入和读取的时序参数。也就是说有 2 个寄存器可用:一个用于配置读取访问(此寄存器),另一个用于配置写入访问(FSMC_BWTRx 寄存器)。

5.3 SRAM/NOR-Flash 写入时序寄存器 1…4 (FSMC_BWTR1…4) SRAM/NOR-Flash write timing registers 1…4 偏移地址:0xA000 0000 + 0x104 + 8 * (x — 1),x = 1…4 复位值:0x0FFF FFFF 该寄存器包含每个存储区域的控制信息,用于 SRAM、ROM 和 NOR Flash。当 FSMC_BCRx 寄存器中的 EXTMOD 位置 1 时,该寄存器将处于有效状态,可以进行写入访问。

|

【经验分享】STM32CubeIDE汉化

手把手教你VSCode搭建STM32开发环境

RTOS在STM32中的应用

【下载有礼】STM32 Finder华为应用商店正式上线!移动选型工具助力开发效率升级

【2025·STM32峰会】GUI解决方案实训分享5-调通板载的NRF24L01 SPI接口并使用模块进行无线通信(发送和接收)

【2025·STM32峰会】GUI解决方案实训分享2-编译运行TouchGFX咖啡机例程(含桌面仿真)

实战经验 | Keil工程使用NEAI库的异常问题

STM32 ISP IQTune:真正零门槛的免费ISP调整软件

【经验分享】STM32 新建基于STM32F40x 固件库的MDK5 工程

意法半导体MCU双供应链策略,打消中国客户后顾之忧

微信公众号

微信公众号

手机版

手机版