.png) STMCU小助手

发布时间:2022-7-14 18:00

STMCU小助手

发布时间:2022-7-14 18:00

|

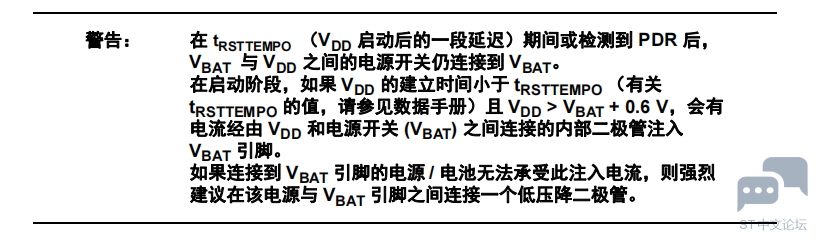

前言 本应用笔记为系统开发者们提供了所需的开发板特性硬件实现概述,如供电电源、时钟管理、复位控制、自举模式设置、调试管理。它显示了如何使用 STM32L4 MCU,说明了开发使用 STM32L4 系列的应用所需的最低硬件资源。 本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式 1 电源 1.1 电源 STM32L4 系列器件要求 1.71 V 至 3.6 V 的 VDD 工作电压电源。多个独立电源 (VDDA, VDDIO2, VDDUSB, VLCD),可支持特定外设: • VDD = 1.71 V 至 3.6 V VDD 是为 I/O、内部调压器和系统模拟信号 (如复位、电源管理和内部时钟)供电的外部电源。通过 VDD 引脚从外部提供。 • VDDA = 1.62 V (ADC/COMP) / 1.8 V (DAC/OPAMP) / 2.4 V (VREFBUF) 至 3.6 V VDDA 是为 A/D 转换器、 D/A 转换器、电压参考缓冲器、运算放大器和比较器供电的外部模拟电源。 VDDA 电压电平独立于 VDD 电压。 • VDDUSB = 3.0 至 3.6 V (使用 USB) VDDUSB 为外部独立电源,为 USB 收发器供电。 VDDUSB 电压电平独立于 VDD 电压。 • VDDIO2 = 1.08 至 3.6 V VDDIO2 是为 14 个 I/O (Port G[15:2])供电的外部电源。 VDDIO2 电压电平独立于 VDD电压。 注: 当功能由 VDDA 供电时,不使用 VDDIO2 或 VDDUSB,这些电源应当分别短接到 VDD。 • VLCD = 2.5 至 3.6 V LCD 控制器可由 VLCD 引脚外部供电,或由嵌入式升压转换器产生的内部电压内部供电。 VLCD 与 PC3 (当 LCD 不用时, PC3 可用作 GPIO)复用。 • VBAT = 1.55 到 3.6 V 当 VDD 掉电时, VBAT 作为 RTC、 32 kHz 外部时钟振荡器和备份寄存器的电源 (通过电源开关供电)。 • VREF-, VREF+ VREF+ 为 ADC 和 DAC 的输入参考电压。使能时,它还是内部电压参考缓冲器的输出。 当 VDDA < 2 V 时, VREF+ 必须等于 VDDA。 当 VDDA ≥ 2 V 时, VREF+ 必须在 2 V 和 VDDA 之间。 当 ADC 和 DAC 不活动时, VREF+ 可接地。 内部电压参考缓冲器支持两个输出电压,可利用 VREF_CSR 寄存器中的 VRS 位进行配置: – VREF+ 大约为 2.048 V。这要求 VDDA 大于等于 2.4 V。 – VREF+ 大约为 2.5 V。这要求 VDDA 大于等于 2.8 V。 VREF- 和 VREF+ 引脚不是在所有封装上都可用。当不可用时,它们分别与 VSSA 和VDDA 绑定。 当 VREF+ 与 VDDA 在一个封装中互相绑定时,内部电压参考缓冲器不可用且必须禁用(关于封装引脚分配说明,请参考数据手册)。 VREF- 必须始终等于 VSSA。 使用一个嵌入式线性调压器来为内部数字电源 VCORE 供电。VCORE 是为数字外设,SRAM1和 SRAM2 供电的电源。 Flash 由 VCORE 和 VDD 供电。 ![F7%$)HM@SXE[A%]KEV3@W@Y.png F7%$)HM@SXE[A%]KEV3@W@Y.png](data/attachment/forum/202207/13/182407u8e9e6i25f50si80.png)

1.1.1 独立模拟外设电源 为了提高 ADC 和 DAC 转换精度、扩展供电的灵活性,模拟外设配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。 • 模拟外设电压源从单独的 VDDA 引脚输入。 • VSSA 引脚提供了独立的电源接地连接。 VDDA 供电电压可与 VDD 不同。在使能任一由 VDDA 供电的模拟外设 (A/D 转换器, D/C 转换器,比较器,运算放大器,电压参考缓冲器)之前,必须检查是否存在 VDDA。 VDDA 电源可由外设电压监测功能监测,并与两个阈值 (对于 PVM3,阈值为 1.65 V,或对于 PVM4,为 2.2 V)进行比较,更多详细内容请参考参考手册章节:外设电压监测 (PVM)。 当使用单供电时, VDDA 可外部连接至 VDD,为得到无噪声的 VDDA 参考电压,需通过外部滤波电路。 ADC 和 DAC 参考电压 为确保低电压输入和输出上的更好精度,用户可将 VREF+ 连接至一个独立的,低于 VDDA 的参考电压源。对于模拟输入 (ADC)或输出 (DAC)信号, VREF+ 为最高电压,以满量程值表示。 VREF+ 可由外部参考或内部缓冲的电压参考 (VREF)来提供。 通过设置 VREF 控制和状态寄存器 (VREF_CSR)中的 ENVR 位,可使能内部电压参考。 当 VRS 位置位时,电压参考设为 2.5 V,当 VRS 位清零时,电压参考设为 2.048 V。内部电压参考还可通过 VREF+ 引脚为外部元件供电。请查阅器件数据手册或参考手册 以获取更多信息。 1.1.2 独立 I/O 电源轨 来自 Port G (PG[15:2])的一些 I/O 由一个单独的电源轨供电。此轨的电源范围为 1.08 至3.6 V,可通过 VDDIO2 引脚外部提供。 VDDIO2 电压电平与 VDD 或 VDDA 完全独立。 VDDIO2引脚仅在一些封装中可用。关于 I/O 列表,请参考相关器件数据手册中的引脚分配图表。 复位后,由 VDDIO2 供电的 I/O 是逻辑隔离且电隔离的,因而不可用。当 VDDIO2 电源存在时,从 PG[15:2] 使用任一 I/O 前,须通过设置 PWR_CR2 寄存器中的 IOSV 位,解除此隔离。 VDDIO2 电源可由外设电压监测功能 (PVM2)监测,并与内部参考电压 (3/4 VREFINT, 0.9 V 左右)进行比较,更多详细内容请参考参考手册章节:外设电压监测 (PVM)。 1.1.3 独立的 USB 收发器电源 USB 收发器通过一个单独的电源引脚 VDDUSB 供电。VDDUSB 范围是从 3.0 V 到 3.6 V,完全独立于 VDD 或 VDDA。 复位后,由 VDDUSB 供电的 USB 功能是逻辑隔离且电隔离的,因而不可用。当 VDDUSB 电源存在时,使用 USB OTG 外设前,须通过设置 PWR_CR2 寄存器中的 USV 位,解除此隔离。 VDDUSB 电源可由外设电压监测功能 (PVM1)监测,并与内部参考电压 (VREFINT, 1.2 V左右)进行比较,更多详细内容请参考参考手册章节:外设电压监测 (PVM)。 1.1.4 独立 LCD 供电 VLCD 引脚用于控制玻璃 LCD 的对比度。可用两种方法使用这一引脚: • 它可从外部电路接收所需的最大电压,由微控制器通过 segment 和 common 线供给玻璃LCD。 • 还可用它连接外部电容,微控制器将该电容用于内部的升压转换器。此升压转换器由软件控制,以向玻璃 LCD 的 segment 和 common 线提供所需的电压。 向 segment 和 common 线提供的电压定义了玻璃 LCD 像素的对比度。当对帧之间的死区时间进行配置,可降低此对比度。 • 向 VLCD 引脚提供外部电源时,该电源范围应为 2.5 V 至 3.6 V。它不依赖于 VDD。 • 当 LCD 基于内部升压转换器时,VLCD 引脚应当连接一个电容(更多信息请参见产品数据手册)。 1.1.5 电池备份域 为了在 VDD 掉电时,还能保留备份寄存器的内容,且让 RTC 继续工作,可将 VBAT 引脚连接到电池或者其他备用电源上。 VBAT 引脚为 RTC 单元、 LSE 振荡器和 PC13 到 PC15 I/O 供电,允许 RTC 在主电源关闭时也可工作。 VBAT 电源的开关由复位模块中内置的掉电复位电路进行控制。

如果没有使用任何外部电池,建议将该 VBAT 连接到带有 100 nF 外部去耦电容的 VDD 上。 当备份域由 VDD(模拟开关连接到 VDD)供电时,PC13、PC14 和 PC15 引脚(属于 VBAT域)有这些功能: • GPIO 引脚 • RTC 或 LSE 引脚 (请参考参考手册章节:RTC 功能说明) 注: 由于模拟开关仅能传递有限的电流 (3 mA),因此使用输出模式的 GPIO PC13 到 PC15 是受限的:速率必须限制在 2 MHz,最大负载为 30 pF,且这些 I/O 不能作为电流源使用(如,驱动 LED)。 通过 VBAT 对备份域供电时 (由于不存在 VDD,内部电源开关连接到 VBAT),可实现以下功能: • PC13、PC14 和 PC15 可仅由 RTC 或 LSE 控制,请参考参考手册章节:RTC 功能说明 • PA0 和 PE6 可用作 RTC 的入侵输入 (分别为 RTC_TAMP2 和 RTC_TAMP3) 备份域访问 系统复位后,备份域 (RTC 寄存器和备份寄存器)将受到保护,以防止意外的写访问。要使能对备份域的访问,请按以下步骤进行操作: 1. 将 APB1 外设时钟使能寄存器 1 (RCC_APB1ENR1)中的 PWREN 位置 1,可使能电源接口时钟。 2. 将电源控制寄存器 1 (PWR_CR1)中的 DBP 位置 1,使能对备份域的访问。 3. 在备份域控制寄存器 (RCC_BDCR)中选择 RTC 时钟源。 4. 将备份域控制寄存器 (RCC_BDCR) 中的 RTCEN [15] 位置 1,使能 RTC 时钟。 VBAT 电池充电 当 VDD 存在时,可通过内部电阻为 VBAT 上的外部电池充电。 VBAT 充电可通过一个 5 kΩ 的电阻或 1.5 kΩ 的电阻来实现,取决于 PWR_CR4 寄存器中VBRS 位的值。 可将 PWR_CR4 寄存器中的 VBE 位置 1 来使能电池充电。在 VBAT 模式下自动禁用。 1.1.6 调压器 两个嵌入式线性调压器为待机电路和备份域以外的所有数字电路供电。根据系统的最大工作频率,主调压器输出电压 (VCORE)可由软件编程为两种不同的电源范围 (Range 1 和Range 2),以优化功耗 (请参考参考手册章节:时钟源频率与电压的比例关系 和 章节:读访问延迟。 调压器在复位后始终处于使能状态。根据应用模式, VCORE 电源由主调压器 (MR)或低功耗调压器 (LPR)提供。 • 在运行模式和睡眠模式中,两个调压器使能,主调压器 (MR)为 VCORE 域 (内核、存储器和数字外设)提供全功率。 • 在低功耗运行模式和低功耗睡眠模式中,主调压器关闭,低功耗调压器 (LPR)为VCORE 域提供低功率,保持寄存器及内部 SRAM1 和 SRAM2 的内容。 • 在 Stop 1 和 Stop 2 模式中,主调压器关闭,低功耗调压器(LPR)为 VCORE 域提供低功率,保持寄存器及内部 SRAM1 和 SRAM2 的内容。但是可使主调压器在 Stop 1 模式下保持为 ON。 • 在待机模式且 SRAM2 内容保持时 (PWR_CR3 寄存器中的 RRS 位置 1),主调压器(MR)关闭,低功耗调压器 (LPR)仅为 SRAM2 供电。内核和数字外设 (待机电路和备份域除外)和 SRAM1 掉电。 • 在待机模式中,两个调压器均掉电。除待机电路和备份域外,寄存器、 SRAM 和SRAM2 的内容都将丢失。 • 在关断模式中,两个调压器均掉电。离开关断模式时,产生一个上电复位。因此,除备份域外,寄存器、 SRAM 和 SRAM2 的内容都将丢失。 1.1.7 动态电压调节管理 动态电压调节是一种电源管理技术,包括根据应用性能和功耗要求,增大或减小用于数字外设的电压 (VCORE)。 动态电压调节增大 VCORE 称作过压。它可提高器件性能。 动态电压调节减小 VCORE 称作欠压。它用来节省功率,尤其是用于笔记本电脑和其他移动设备,其有限能源来自电池的场合。 • Range 1:高性能范围。 主调压器提供了 1.2 V 的典型输出电压。系统时钟频率可达 80 MHz。读访问的 Flash 访问时间最小,可进行写入和擦除操作。 • Range 2:低功耗范围。 主调压器提供了 1.0 V 的典型输出电压。系统时钟频率可达 26 MHz。相比于 Range 1,其读访问的 Flash 访问时间增加;可进行写入和擦除操作。 通过 PWR_CR1 寄存器中的 VOS 位选择电压调节。 从 Range 1 进入 Range 2 的时序为: 1. 降低系统频率至低于 26 MHz。 2. 根据 Range2 中新的频率目标来调整等待状态的数量 (FLASH_ACR 中的 LATENCY位)。 3. 将 PWR_CR1 寄存器中的 VOS 位编程为 “10”。 从 Range 2 进入 Range 1 的时序为: 1. 将 PWR_CR1 寄存器中的 VOS 位编程为 “01”。 2. 等待,直至 PWR_SR2 寄存器中的 VOSF 标志清零。 3. 根据 Range1 中新的频率目标来调整等待状态的数量 (FLASH_ACR 中的 LATENCY位)。 4. 增加系统频率。 完整版请查看:附件 |

DM00125306_ZHV1.pdf

下载808.2 KB, 下载次数: 58

STM32L4R9 QuadSPI Flash通讯速率优化解析 32位总线的DMA传输适配核心方案

【STEVAL-STWINKT1B评测】运行Datalog固件并记录运行时间

【STEVAL-STWINKT1B评测】数字麦/模拟麦对比测试+音频配套上位机软件开发

【板卡评测】STEVAL-STWINKT1B读取 ACC/GYRO/MAG 实时数据

小白也能明白的STM32的低功耗与唤醒机制

【STM32入门学习路径指南】(四步走)

STM32和Arduino对比,谁更耐打?

STM32系统中2种数据掉电保护的方法

STM32 LL为什么比HAL高效?

STM32小白入门指南:从基础到OTA实现方案

微信公众号

微信公众号

手机版

手机版

红红火火恍恍惚惚哈哈哈哈哈哈哈哈哈哈哈

想了解具有一点点的内容。