.png) STMCU小助手

发布时间:2023-10-19 14:11

STMCU小助手

发布时间:2023-10-19 14:11

|

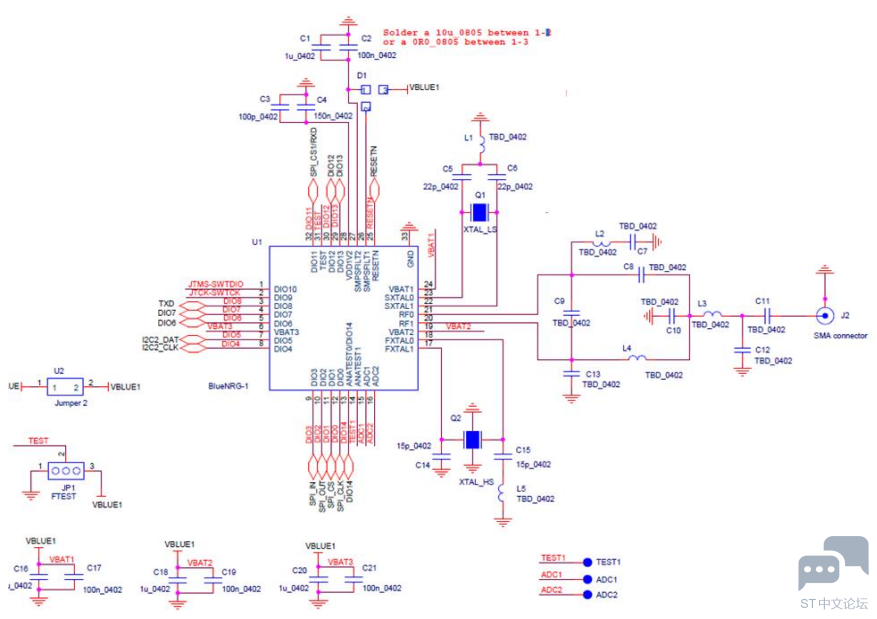

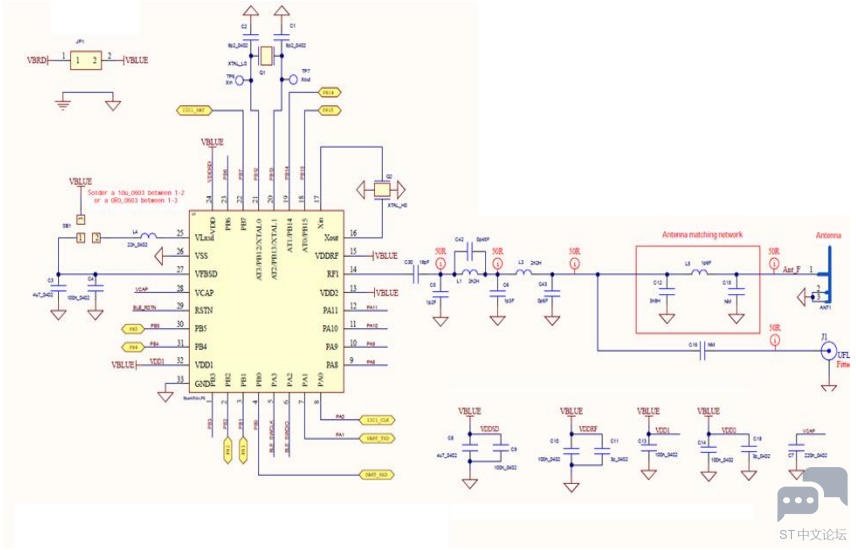

01前言 为了让客户在原理图设计阶段少走弯路,我这里结合客户评估和设计阶段常遇到的问题,整理了一下 BlueNRG-1/-2 相关设计及注意事项以备客户解惑用。 02BlueNRG-1/-2 的原理图参数说明及设计注意事项 2.1. BlueNRG-1/-2 原理图及参数如下: 通过断点和单步调试,我们发现出现问题的指令如下所示:

图1.IDB007V1_schematic

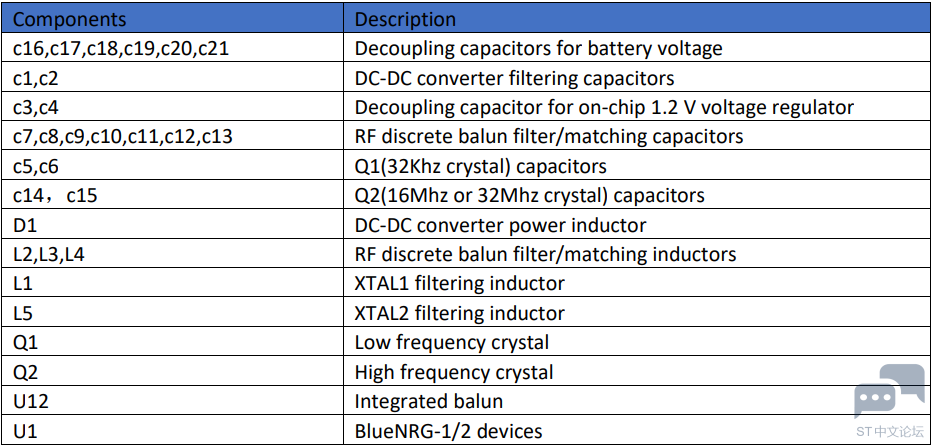

图2.IDB008V2_schematic

表1. 基于 BlueNRG-1/2 板子的元器件说明 2.2. 原理图设计注意事项: 1. C4 的取值只能是 150nf 或者 220nf,否则会影响系统的稳定。 2. 设计成 SMPS ON 的是时候,D1 中的 pin1 和 pin2 之间焊接一颗电感,该电感的具体要求如下:标称值为 10 uH 或 4.7 uH ,但 DCR 务必小于 1ohm 且额定电流必须大于 100 mA。 3. RXD/TXD 必须接到 DIO11 和 DIO08 pin,否则后续将无法使用 RF Flash utility 工具和 BlueNRG GUI 工具。 4. 这里的 L1=2nH,L5=3.9nH 建议保留,这有助于抑制最后通道的杂散并减少晶体和RF 信号间的相互影响。 5. 建议预留 ANATEST0 pin 和 ANATEST1 pin 的测试点,以便后续测试高速晶体的启振时间。 6. DIO7 建议通过 100kohm 电阻接地并预留测试点:为强制执行 updater 代码(参见预先编程的引导加载程序),建议将 IO7 引脚拉高并硬件复位设备。 03BlueNRG-LP/LPS 的原理图参数说明及设计注意事项 3.1. BlueNRG-LP 原理图及参数如下:

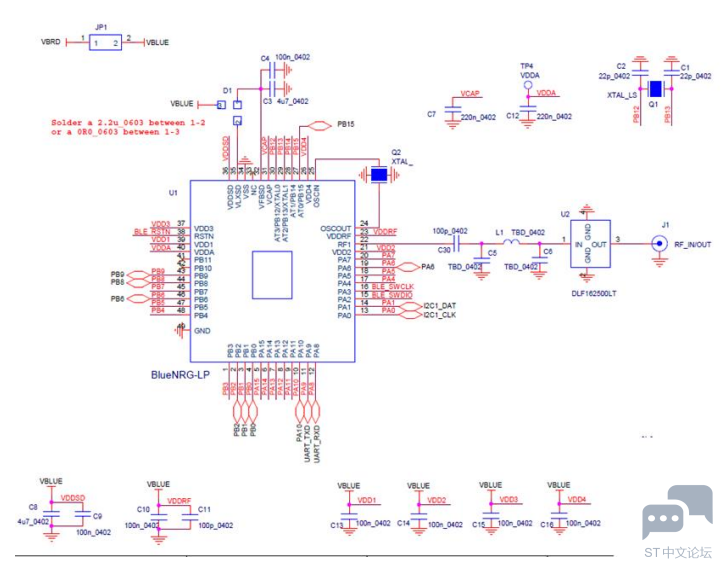

图3.IDB011V1_schematic

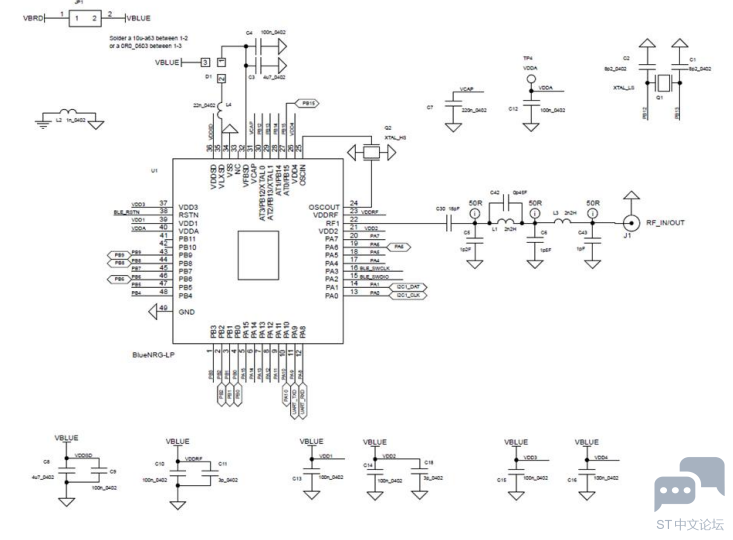

图4.IDB011V2_schematic 3.2. BlueNRG-LPS 原理图及参数说明如下:

图5.IDB012V1_schematic

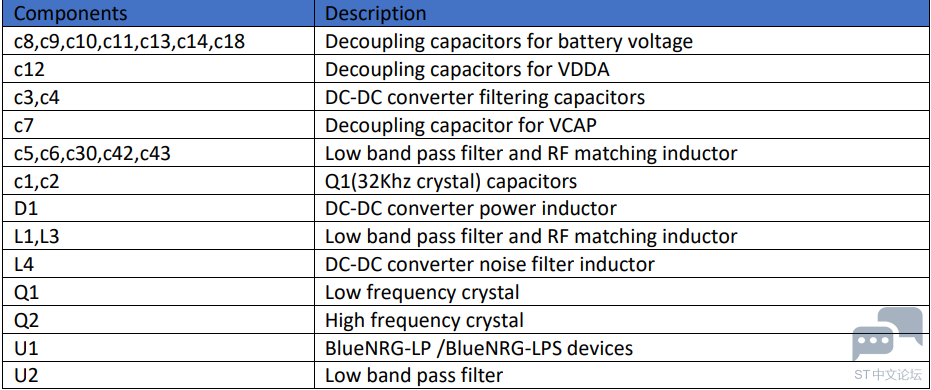

表2. 基于 BlueNRG-LP/LPS 板子的元器件说明 3.3. 原理图设计注意事项: 1. CAP 的取值只能是 150nf 或者 220nf,否则会影响系统的稳定。

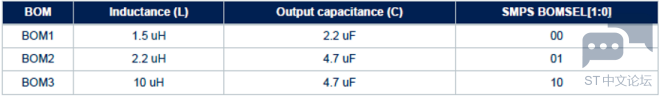

2. 设计成 SMPS ON 的是时候,D1 中的 pin1 和 pin2 之间焊接一颗电感,该电感的具体要求如下:标称值为 10 uH 或 2.2 uH 或 1.5uH,但 DCR 务必小于 1ohm 且额定电流必须大于 100 mA。

表3.SMPS BOM information 3. 对于 BlueNRG-LP 芯片 RXD/TXD 必须接到 PA8 和 PA9 pin,而对于 BlueNRGLPS 芯片 RXD/TXD 必须接到 PB0 和 PA1 pin。否则,后续将无法使用 RF Flash utility 工具和 BlueNRG GUI 工具。 4. 实际应用中 Q1(32KHZ 晶体)可以省略,Q2(32MHZ 晶体)需符合 Fnom=32Mhz,fTOL建议选择±20ppm, PD 不要超过 100uW,CL 选用 6~8pf 的。 5. 建议预留 VCAP 和 PB6 pin 的测试点,以便后续测试高速晶体的启振时间。 6. PA10 建议预留测试点。 04小结 为方便客户、代理 FAE 更好地理解 DEMO 板的原理图,以便客户项目顺利进行, 以及方便后续的测试和调试,这里特意分享以上章节针对不同 DEMO 板的原理图和设计事项做了说明。 转载自: STM32单片机 如有侵权请联系删除 |

【STM32MP257-DK】01开发板开箱、ST MPU 生态资源使用、环境搭建以及镜像更新

基于STM32在线升级OTA经验分享

【STM32C0测评】Nucleo-C092开发板驱动DS1302实验

Keil下的STM32N6之RAM运行工程配置说明

兔哥的初代M33【002】-H503Nucleo 内部flash操作

兔哥的杂谈【002】——如何性价比更高地去编译STM32

汇编浮点库qfplib移植STM32F769I-DISCO开发板与硬件浮点运算性能测试对比

FreeRTOS学习笔记2

【NUCLEO-H533RE评测】+05 调试PWM

基于STM32 hardfault问题分析经验分享

微信公众号

微信公众号

手机版

手机版