.png) STMCU小助手

发布时间:2022-2-19 17:41

STMCU小助手

发布时间:2022-2-19 17:41

|

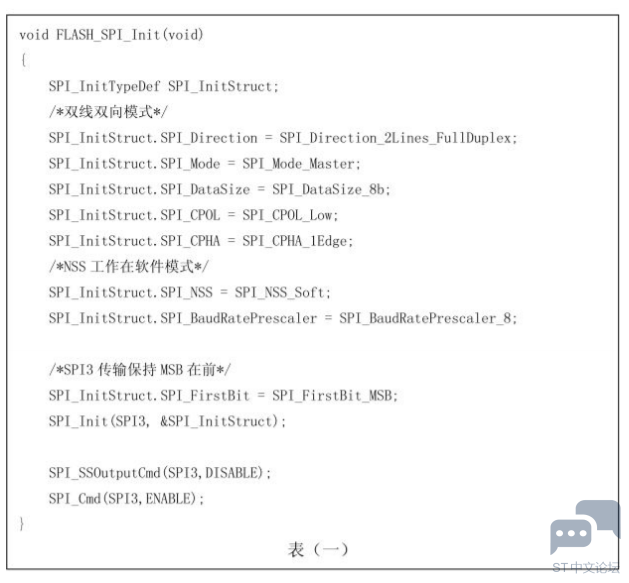

问题: 该问题由某客户提出,发生在 STM32F103VDT6 器件上。据其工程师讲述:在其产品设计中,使用了STM32 的 SPI3 接口连接到一个串行 EEPROM。在软件调试时,发现该接口没有信号送出。反复检查相关设置,未能找出原因,甚感疑惑。 调研: 在确认其硬件系统没有问题之后,检查其软件中相关的设置: 1. 检查 RCC 的 APB2ENR 寄存器中各个 GPIO 的时钟门控位,匀为允许状态; 2. 检查 RCC 的 APB2ENR 寄存器中 AFIO 的时钟门控位,状态为允许; 3. 检查 RCC 的 APB1ENR 寄存器中 SPI3 的时钟门控位,状态为允许; 4. 检查 GPIOB 的 CRL 寄存器中 PB3(SPI3 CLK)的模式设置,其模式为 AF 推拉输出,未见异常; 5. 检查 GPIOB 的 CRL 寄存器中的 PB4(SPI3 MISO)的模式设置,其模式为 AF 推拉输出,正常应为高阻输入; 6. 检查 GPIOB 的 CRL 寄存器中的 PB5(SPI3 MOSI)的模式设置,其模式为 AF 推拉输出,未见异常; 7. 检查 AFIO 的 MAPR 寄存器中的 SWJ CFG 设置,其值为 000,应设为 010,禁止 JTAG DP 而保留 SW DP; 8. 检查 SPI3 的初始化代码,如表(一)所示,未见异常:

修改(5)、(7)中所发现的问题,重新测试,SPI3 有信号送出。 结论: 在 STM32F 系列产品中,PB3、PB4 的缺省功能分别为 JTDO 和 JNRST,只有在对 AFIO 寄存器中的相关的控制位做了正确的设置之后,该管脚才能提供给用户信号使作用。而在本案例中,使用者恰恰没有做相关的设置。 处理: 略。 建议: STM32F 的参考手册在有关 DBG 的章节中,对如何将调试接口所对应的管脚用作用户管脚做出了明确的说明,如表(二)所示:

与此类似,在 64 脚及其以下的封装中,PD0、PD1 分别与 OSC_IN、OSC_OUT 共享管脚。这两个管脚在缺省状态下被设置为用户管脚,如果要将这两个管脚用作 OSC_IN 和 OSC_OUT,也要对 AFIO 的MAPR 寄存器的相关控制位做所要求的设置,具体如下: 1. 当 PD01_REMAP = 0 时,PD0、PD1 用作用户管脚; 2. 当 PD01_REMAP = 1 时,PD0、PD1 分别用作 OSC_IN 和 OSC_OUT; |

经验分享 | STM32C0 HAL 库的 SPI 驱动导致的 Hardfault 问题分析

经验分享 | SPI传输时为何丢失2个数据?

经验分享 | STM32H7 EXTI + SPI +DMA 双缓冲应用演示

使用Nano板验证驱动SPI串口屏的颜色显示

【经验分享】STM32的SPI的原理与使用(W25Q128附代码)

【STM32C0评测】4、驱动Lorasx126x,实现透传

基于STM32的SPI传输时会丢失数据吗?

基于STM32基础的SPI总线概述

基于STM32的SPI读取数据的最后位出错问题经验分享

基于STM32关闭SPI会导致WRPERR错误的问题分析

微信公众号

微信公众号

手机版

手机版