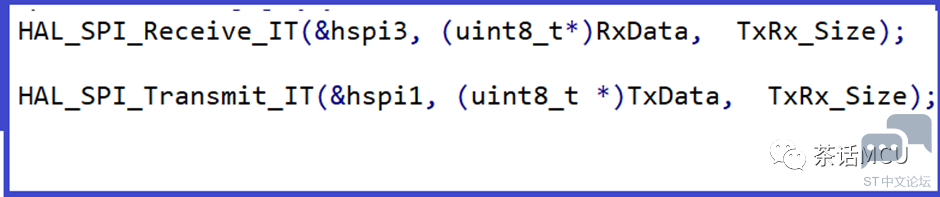

有人使用STM32F4芯片验证SPI功能。当使用片内两个SPI模块基于中断方式进行收发时,发现总是出现接收数据丢失的情况,貌似总丢失末尾2个数据。代码使用HAL库提供的API函数。这是怎么回事呢? 我拿STM32F407开发板进行验证测试。使用SPI1做发送,SPI3做接收,都使用中断方式。

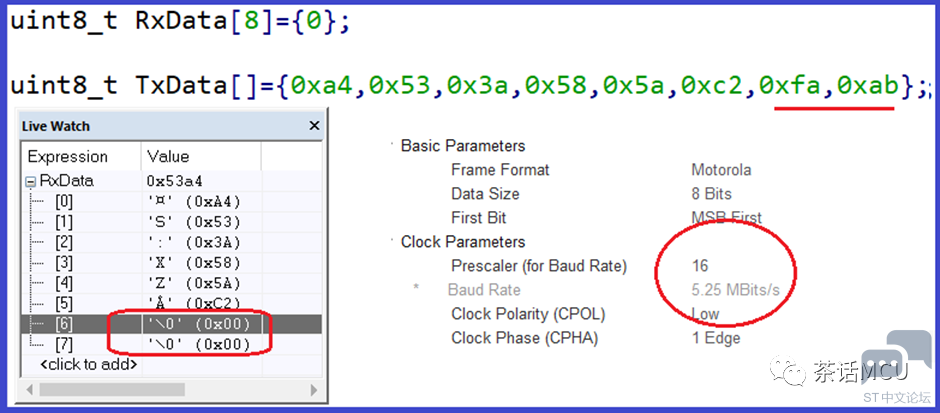

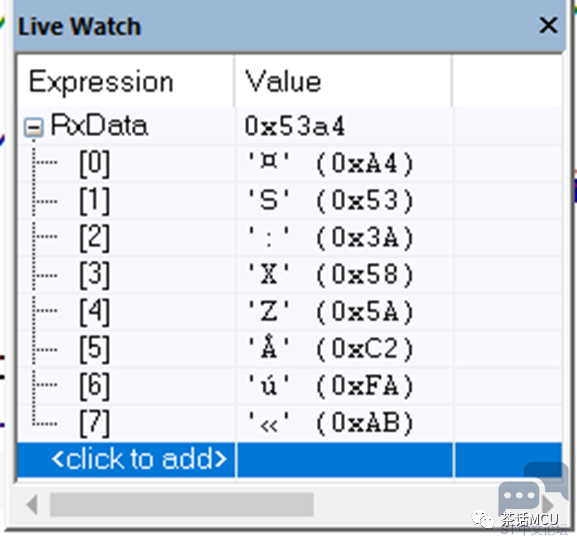

很快重现了问题现象,即发生接收数据丢失的情形。见下图验证结果,发了8个数据,只收到6个数据。

现在是同一颗芯片,即同一CPU基于中断方式完成收发。怀疑会不会是不同SPI收发模块中断优先级的安排不合理导致的问题。如果二者优先级一样的话,这里的发送中断往往先于接收中断的产生,势必会出现接收不及时的情形。通过对代码跟踪调试,也的确发现了SPI接收溢出的现象,即接收数据提取不及时。

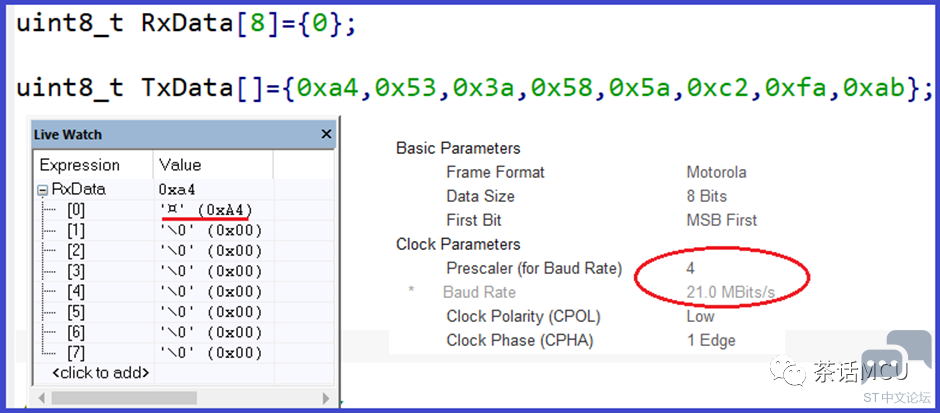

这样分析下来,感觉数据丢失应该跟通信速率有关,丢失数据的多少不应该固定。于是,我大幅度提升SPI通信速率再行测试,果真丢失的数据更多了。见下图测试结果,发8个数据只收到1个数据。【前面测试时SPI波特率是5.25Mb/s,现在改为21Mb/s了】

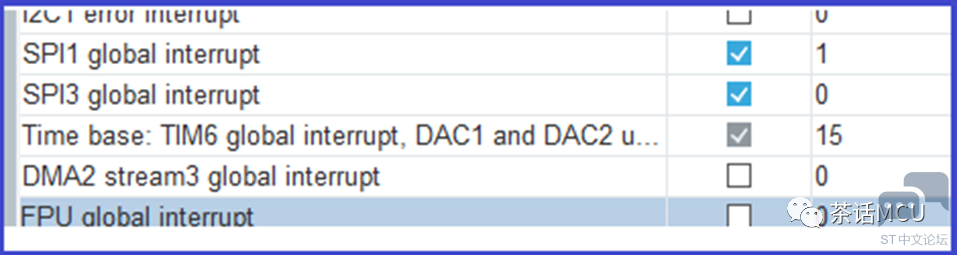

我将SPI3接收中断的优先级调得比SPI1发送中断的还高,如下图所示。

基于重新调整中断优先级后的代码再做测试,结果就完全正常了。

当然,我们还可以有其它灵活处理的办法。比方发送用中断,接收用DMA,或者发送用轮训,接收用中断或DMA,或者都用DMA方式也行。 这里的核心问题是中断优先级没有合理安排好。STM32 ARM核中断的内容不多,不过内容不多的东西往往意味着使用上更为灵活。好,今天的话题就分享到这里。 转载自: 茶话MCU 如有侵权请联系删除 |

SPI 高温读错最后一位?STM32F42xx 官方根治方案

经验分享 | LAT1470 SPI传输长度超过1024时出现异常的问题分析

经验分享 | 使用EXIT0同步触发SPI的DMA发送话题

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

【STM32C0评测】4、驱动Lorasx126x,实现透传

经验分享 | STM32 SPI半工单线通信示例

经验分享 | 多个SPI的DMA传输为何仅1个有效?

经验分享 | STM32C0 HAL 库的 SPI 驱动导致的 Hardfault 问题分析

经验分享 | SPI传输时为何丢失2个数据?

经验分享 | STM32H7 EXTI + SPI +DMA 双缓冲应用演示

微信公众号

微信公众号

手机版

手机版