|

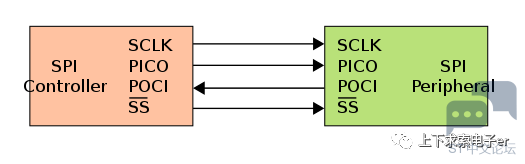

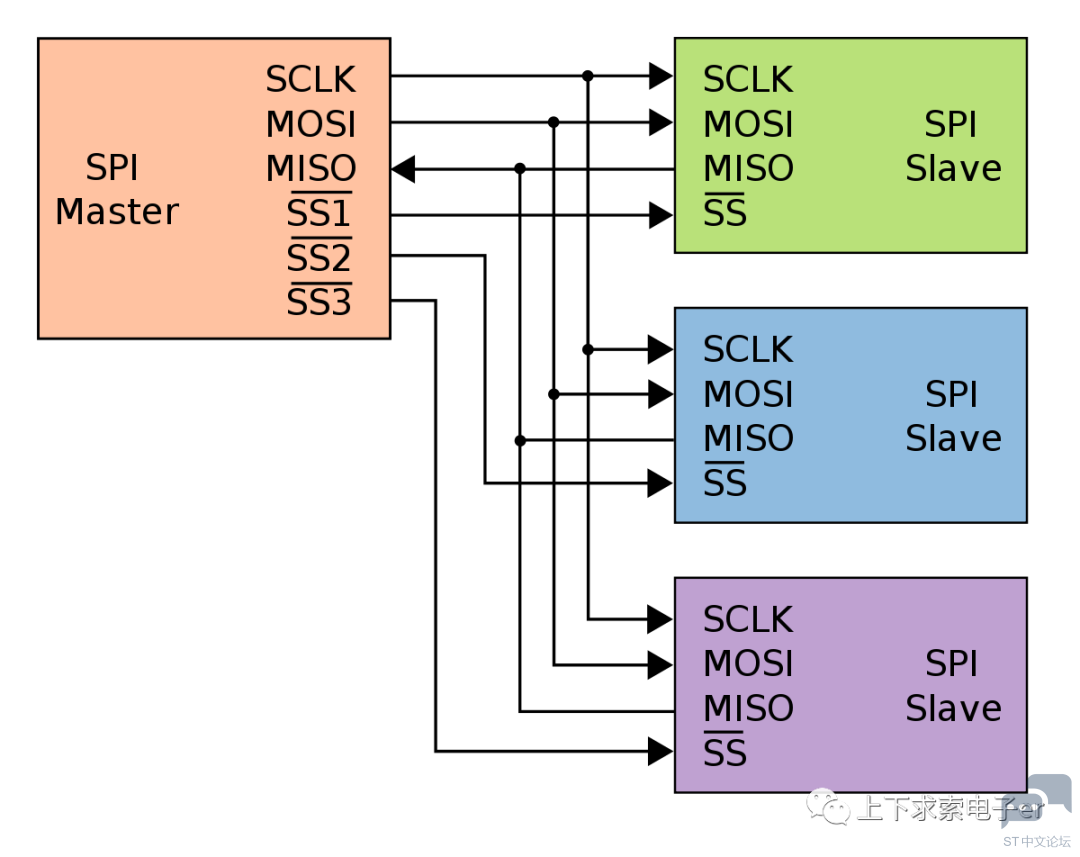

SPI总线概述1 基本概念 串行外设接口(Serial Peripheral Interface)的简称也叫做SPI,是一种高速、全双工同步通信的一种接口,串行外设接口一般是需要4根线来进行通信(NSS、MISO、MOSI、SCK),但是如果打算实现单向通信也可以只使用3根线(NSS、MISO/MOSI、SCK),就可以利用这种机制实现一对多或者一对一的通信。

通常SPI通过4个引脚与外部器件相连:

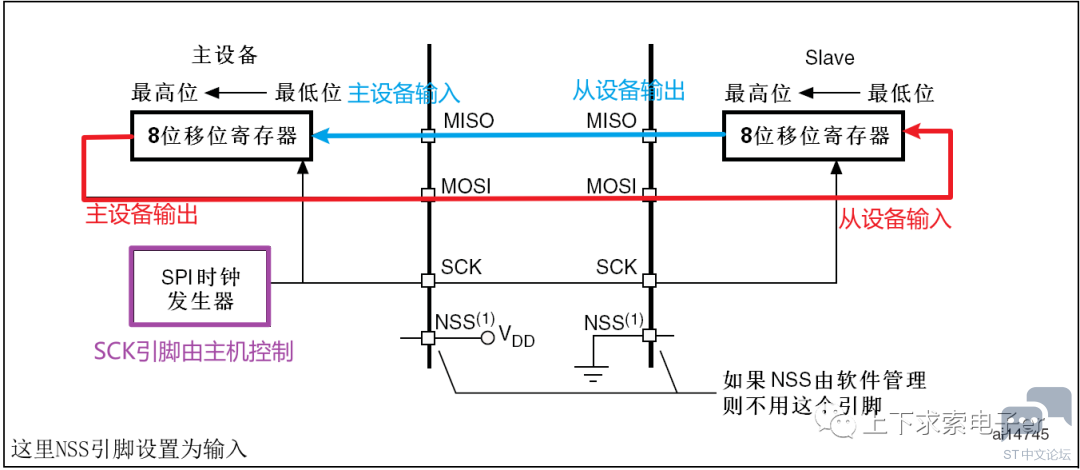

SPI总线采用的环形结构,利用的是主从模式(主机→从机)进行数据的传输,由于是同步通信,所以在主机发送数据的同时也会收到从机发送的数据。

MOSI脚相互连接,MISO脚相互连接。这样,数据在主和从之间串行地传输(MSB位在)。通信总是由主设备发起。主设备通过MOSI脚把数据发送给从设备,从设备通过MISO引脚回传数据。这意味全双工通信的数据输出和数据输入是用同一个时钟信号同步的;时钟信号由主设备通过SCK脚提供。

NSS的说明:主机的NSS引脚在空闲状态下应处于高电平(VDD),主机发送数据时,主机的NSS应为输出模式,从机的NSS为输入模式,当主机的NSS引脚拉低,从设备的NSS引脚可以检测到低电平,该设备被选中。

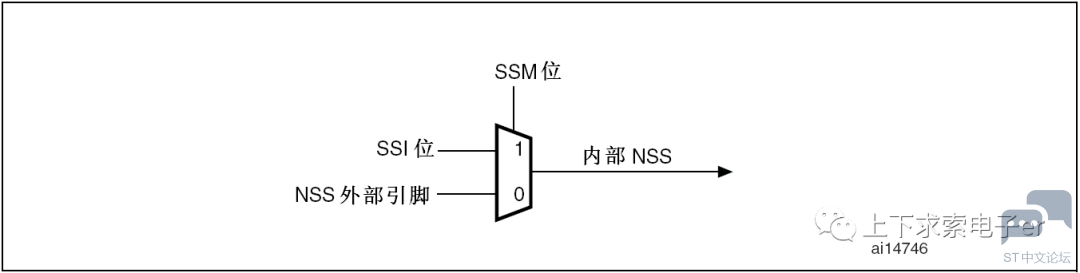

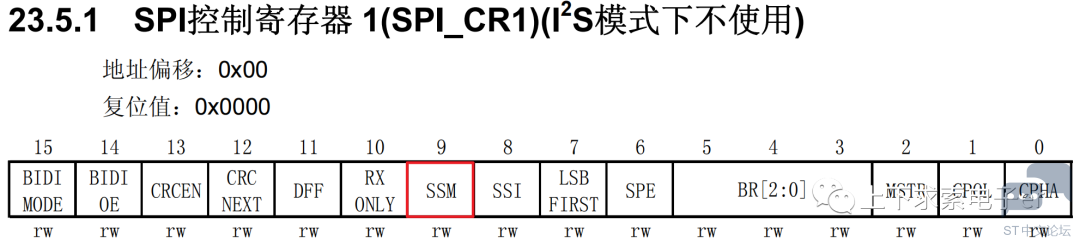

从SPI的结构框图中可以看到NSS也是外部引脚的名称,其实控制SPI收发数据是通过内部的NSS信号实现的,而这个内部的NSS信号源可以由SPI_CR1寄存器的SSM(Software slave management)位来配置。

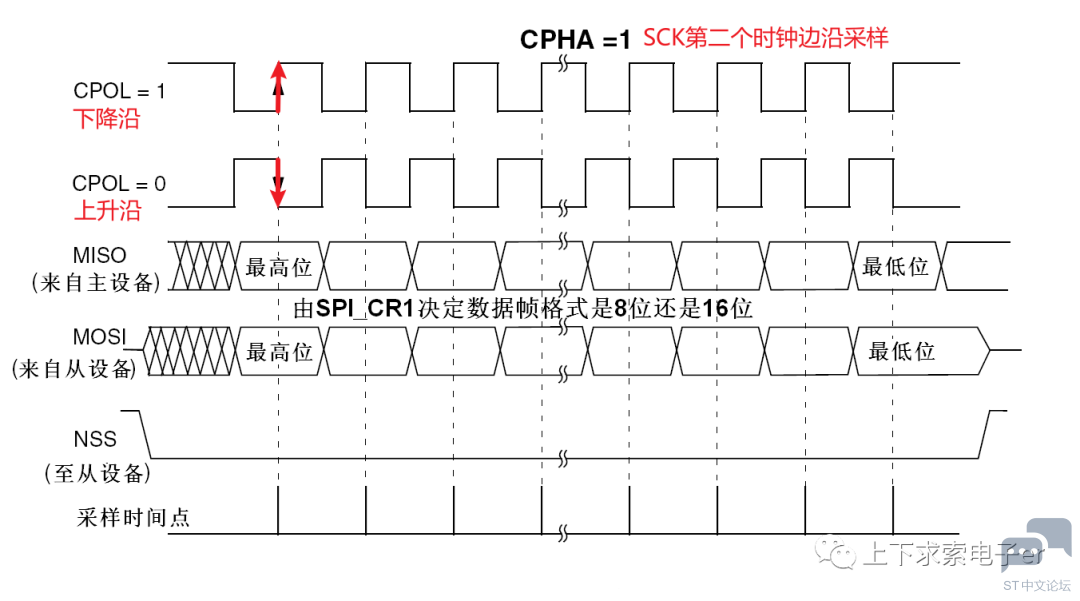

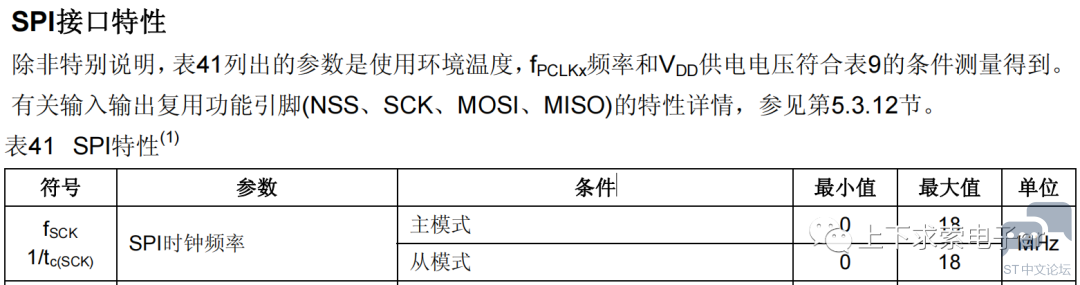

注意:由于SPI外设是全双工同步通信,所以时钟信号就由SCK引脚来生成,SCK引脚只能由主设备控制,从设备是无法控制的,所以SCK引脚输出的脉冲信号的极性和相位就需要进行配置。

SPI_CR寄存器的CPOL(时钟极性位)和CPHA(时钟相位位),能够组合成四种可能的时序关系。

![DQ5]PQ22EK{DJ4}JY1J07XL.png DQ5]PQ22EK{DJ4}JY1J07XL.png](data/attachment/forum/202309/20/170847c0ibbxh0hu33i9o9.png)

通过这两位可以得到四种不同的组合,就被作为SPI总线的工作模式(模式0~模式3),到底要选择哪种模式,主机的工作模式必须根据从设备的数据手册的说明进行设置。 在实际的开发过程中,使用最多是模式0和模式3,比如2.4G无线通信模块NRF24L01采用模式0来通信。

3.2 数据帧格式

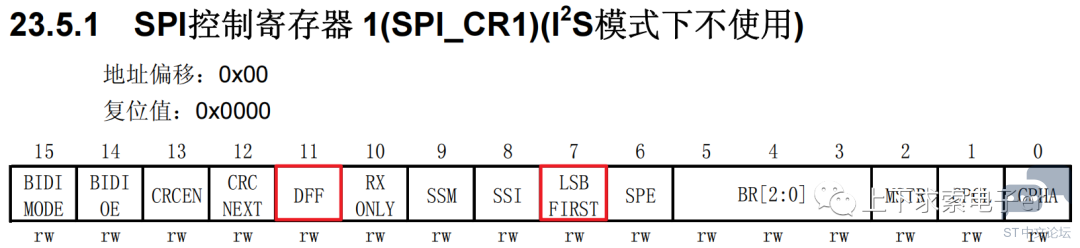

DFF:数据帧格式 (Data frame format)

LSBFIRST:帧格式 (Frame format)

5 使用流程 The SPI HAL driver can be used as follows: (#) **Declare a SPI_HandleTypeDef handle structure**, for example: `SPI_HandleTypeDef hspi`; (#)**Initialize the SPI low level resources** by implementing the `HAL_SPI_MspInit()` API: (##) **Enable the SPIx interface clock** (##) **SPI pins configuration** (+++) Enable the clock for the SPI GPIOs (+++) Configure these SPI pins as alternate function push-pull (##) **NVIC configuration if you need to use interrupt process** (+++) Configure the SPIx interrupt priority (+++) Enable the NVIC SPI IRQ handle (##) **DMA Configuration if you need to use DMA process** (+++) Declare a DMA_HandleTypeDef handle structure for the transmit or receive Stream/Channel (+++) Enable the DMAx clock (+++) Configure the DMA handle parameters (+++) Configure the DMA Tx or Rx Stream/Channel (+++) Associate the initialized hdma_tx(or _rx) handle to the hspi DMA Tx or Rx handle (+++) Configure the priority and enable the NVIC for the transfer complete interrupt on the DMA Tx or Rx Stream/Channel (#) **Program the Mode, BidirectionalMode , Data size, Baudrate Prescaler, NSS management, Clock polarity and phase, FirstBit and CRC configuration in the hspi Init structure.** (#) **Initialize the SPI registers by calling the** `HAL_SPI_Init() API`: (++) This API configures also the low level Hardware GPIO, CLOCK, CORTEX...etc) by calling the customized HAL_SPI_MspInit() API. 简述如下:

转载自:上下求索电子er 如有侵权请联系删除 |

经验分享 | LAT1470 SPI传输长度超过1024时出现异常的问题分析

经验分享 | 使用EXIT0同步触发SPI的DMA发送话题

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

【STM32C0评测】4、驱动Lorasx126x,实现透传

经验分享 | STM32 SPI半工单线通信示例

经验分享 | 多个SPI的DMA传输为何仅1个有效?

经验分享 | STM32C0 HAL 库的 SPI 驱动导致的 Hardfault 问题分析

经验分享 | SPI传输时为何丢失2个数据?

经验分享 | STM32H7 EXTI + SPI +DMA 双缓冲应用演示

使用Nano板验证驱动SPI串口屏的颜色显示

微信公众号

微信公众号

手机版

手机版