.png) STMCU小助手

发布时间:2021-11-28 22:00

STMCU小助手

发布时间:2021-11-28 22:00

|

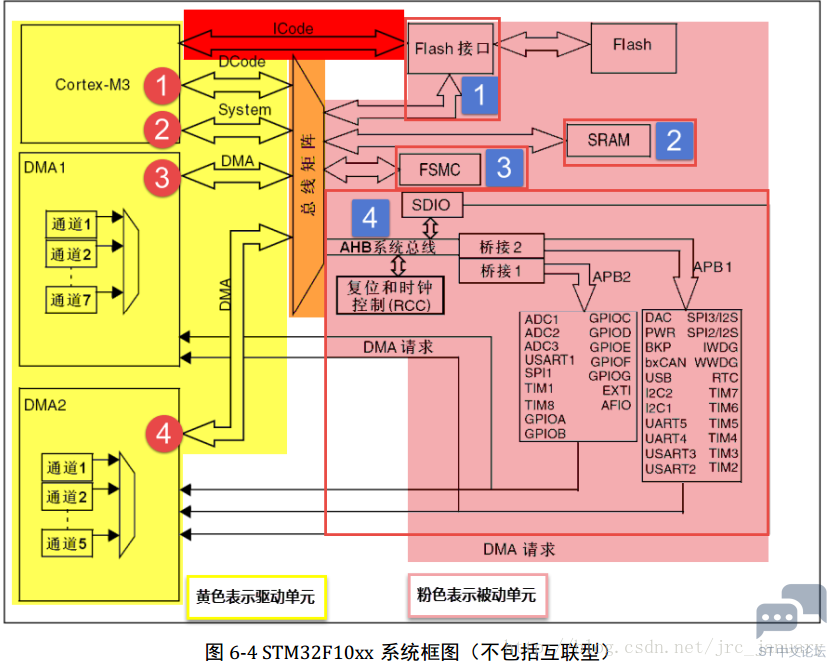

STM32F10xx系列单片机是意法半导体推出的ARM核心32bit单片机。性价比非常高,真正做到了高性能、低价格并且极易使用,因此受到了工程师和应用厂商的共同青睐。 1. ST和ARM ST是半导体设计、制造公司,它设计并生产芯片。 ARM是知识产权(IP intellectual property)供应商,它的产品是ARM内核(只做设计)。 对于STM32F10XX,其中CPU是ARM公司设计的,其他部分是ST公司设计的,整个芯片是ST公司制造的。 2. STM32F10X 对于一个MCU(microcontroller unit),就像它的名字一样,其主要角色就是一个控制器(controller)而且是一个微(micro)控制器,并且它自成一个单元(unit),因此它是一系列组件的结合。 这些组件包括CPU(中央处理器)、ROM、RAM、总线、各种被控制设备(外设)等等。。。 2.1 STM32F10X系统架构 简单一点,所谓的系统架构就是:MCU里面有哪些东西?这些东西是怎么布置(连接)的? 通过这幅框图(来自野火的资料),理解它的架构就足够了:

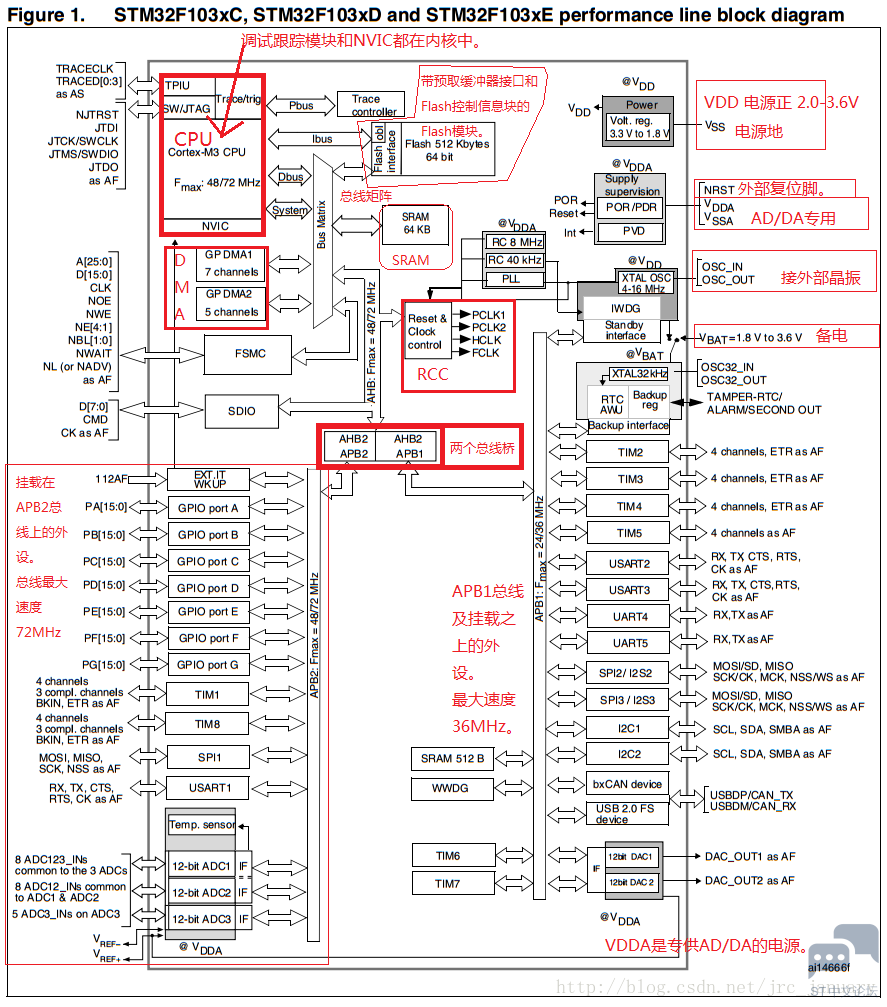

通过上面框图可以看到MCU的组成: ICode总线; 驱动单元; 被动单元; 总线矩阵; 其中: 1.ICode总线:该总线将Cortex™-M3内核的指令总线与闪存指令接口相连接。指令预取在此总线上完成。 2.驱动单元 DCode总线:该总线将Cortex™-M3内核的DCode总线与闪存存储器的数据接口相连接(常量加载和调试访问)。 DCode 中的 D 表示 Data,即数据,那说明这条总线是用来取数的。 我们在写程序的时 候,数据有常量和变量两种,常量就是固定不变的,用 C 语言中的 const关键字修饰,是放 到内部的 FLASH 当中的,变量是可变的,不管是全局变量还是局部变量都放在内部的 SRAM。 因为数据可以被 Dcode 总线和 DMA 总线访问,所以为了避免访问冲突,在取数的 时候需要经过一个总线矩阵来仲裁,决定哪个总线在取数。 系统总线:此总线连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间的访问。 系统总线主要是访问外设的寄存器,我们通常说的寄存器编程,即读写寄存器都是通 过这根系统总线来完成的。 DMA 总线:DMA 总线也主要是用来传输数据,这个数据可以是在某个外设的数据寄存器,可以在 SRAM,可以在内部的 FLASH。因为数据可以被 Dcode 总线和 DMA 总线访问,所以为了 避免访问冲突,在取数的时候需要经过一个总线矩阵来仲裁,决定哪个总线在取数。 3.被动单元 内部的Flash:用于存放指令和只读数据,也包括未加载的程序的存储以及用户自由存储的数据; 内部SRAM:用于全局变量和堆栈的开销; FSMC:flexible static memory controller,可用于扩展设备。 AHB到APB的桥:APB1和APB2上挂载者各种外设,它们速度相对较低,因此使用AHB到APB的桥来衔接。 4.总线矩阵:总线矩阵协调各个总线之间的访问仲裁,仲裁利用轮换算法。 来个更详细的:

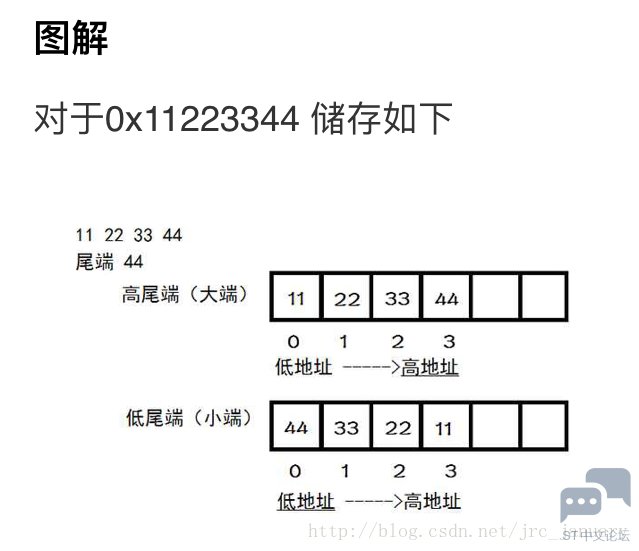

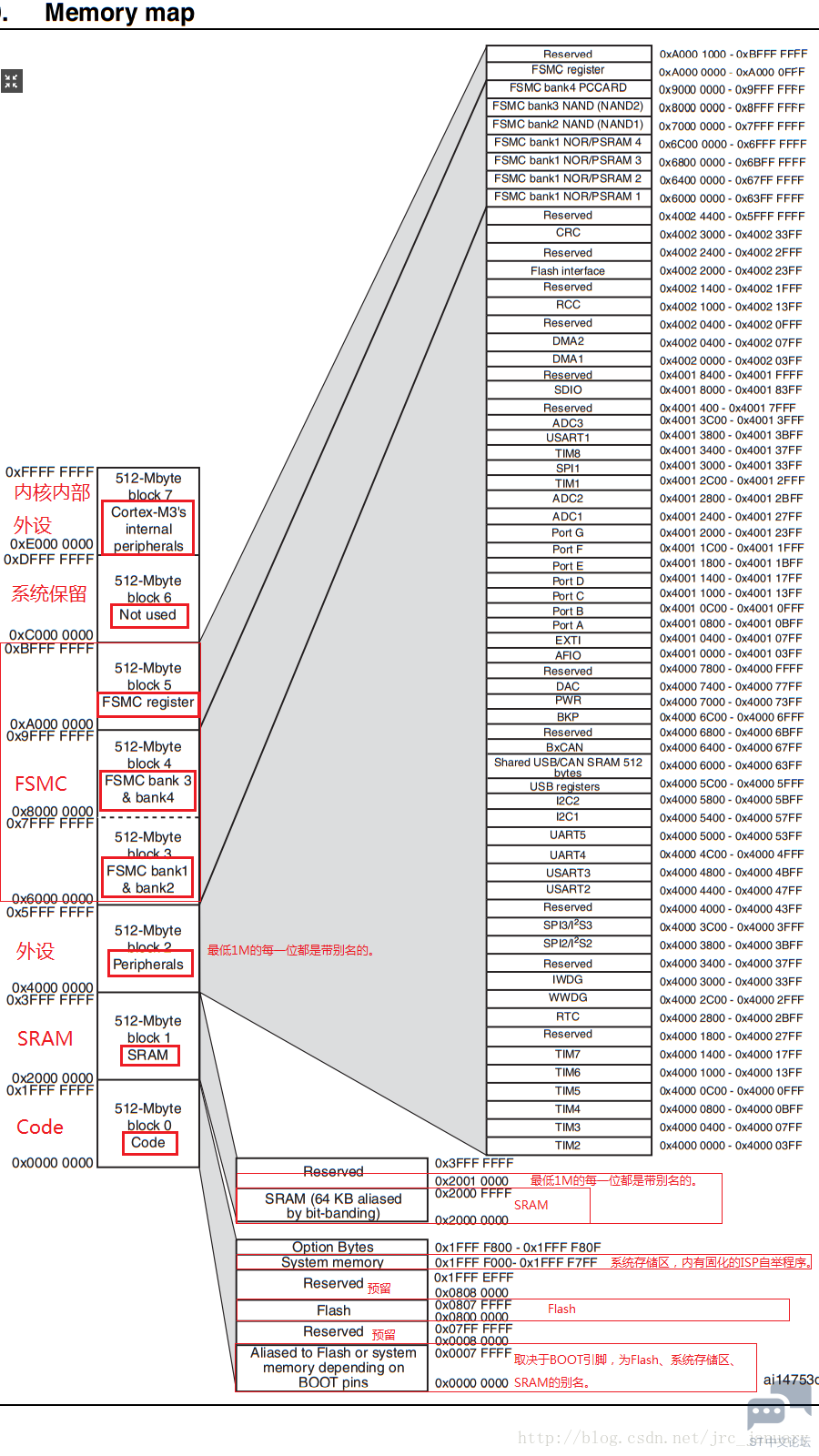

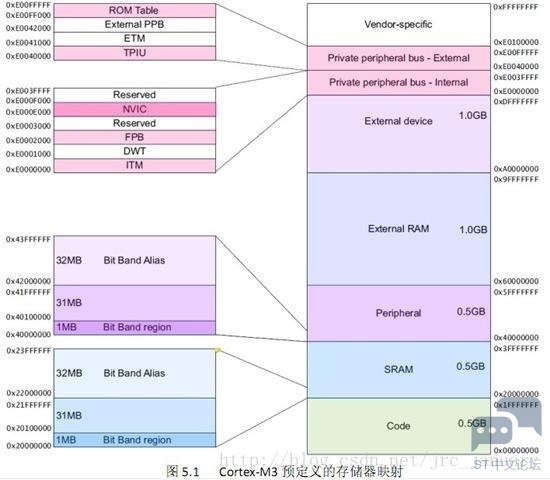

小结: 芯片内各个组件都连接到各自总线->各个总线都连接到总线矩阵->总线矩阵协调各个总线之间的访问仲裁。 2.2 存储器映射 为使CPU能控制芯片中的每个被动单元,这些被动单元的每个组件就必须要有一个确切的地址。 各个组件和4GB地址空间的对应关系就是储器映射。 程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。可访问的存储器空间被分成8个主要块,每个块为512MB。 数据字节以小端格式存放在存储器中。其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间。(没有分配的不要用,是系统保留的,用了会出问题。) 知识点: - 小端:低尾端,即字节序的尾端存储在低地址的存储单元。 - 大端:反过来即是。

存储器映射图:

其实,上面的具体分配是ST做的,但是ARM提供了一个框架,ST具体了每个组件的地址。下面是ARM的存储器映射框架:

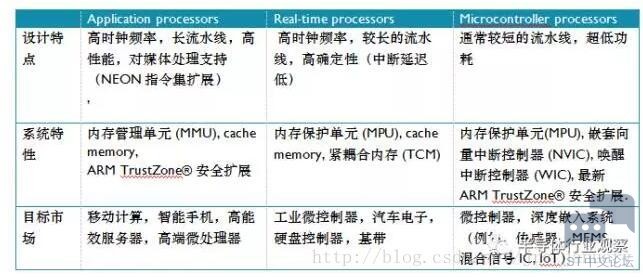

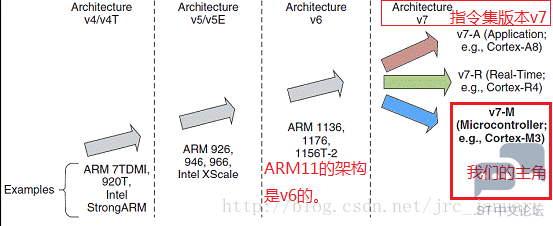

2.3 寄存器映射 在block2地址块中编排的是外设寄存器的地址。 外设寄存器是用来控制外设或缓存外设数据的数字电路结构。在本质上,它们和存储器(如FLASH或SRAM)没什么区别,都是不同功能的数字电路。只是在应用上主要用于外设的访问和控制。 映射的定义没有改变,就是对应关系。 寄存器映射是指:一个(寄存器的)地址与一个(我们取的)名字的对应关系。有了这样的映射关系,在写程序时就可以用一个符号来代指一个寄存器,而不要通过一个个地址来代指,大大地方便了程序的编写(特别是C语言程序)。 3. Cortex系列处理器 前面简单地看了看STM32的功能结构,在单片机中最重要的一部分便是CPU,往往,我们在做应用时与它打交道是最少的,但对于整个单片机来讲,它是最重要的,也是最复杂的。 ARM公司设计的处理器自从ARM11(指令集版本为ARMv6)之后,命名为Cortex。 Cortex分为三个系列,如下图(指令集版本分别为ARMv7-A、ARMv7-R、ARMv7-M):

Cortex-A:Application,面向尖端的基于虚拟内存的操作系统和用户应用。 Cortex-R:Realtime,面向实时应用。 Cortex-M:Mircocontroller,面向微控制器。 ARM指令集架构历史回顾:

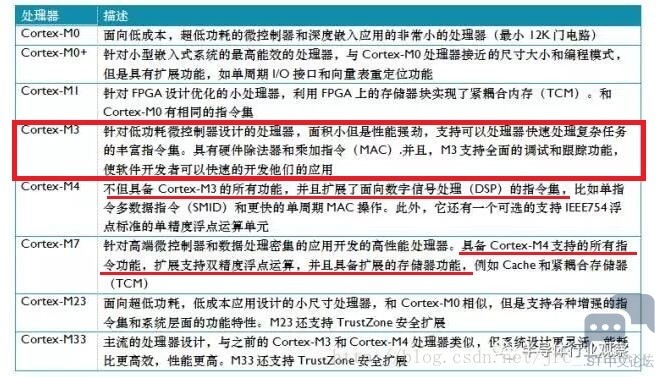

3.1 Cortex-M家族:

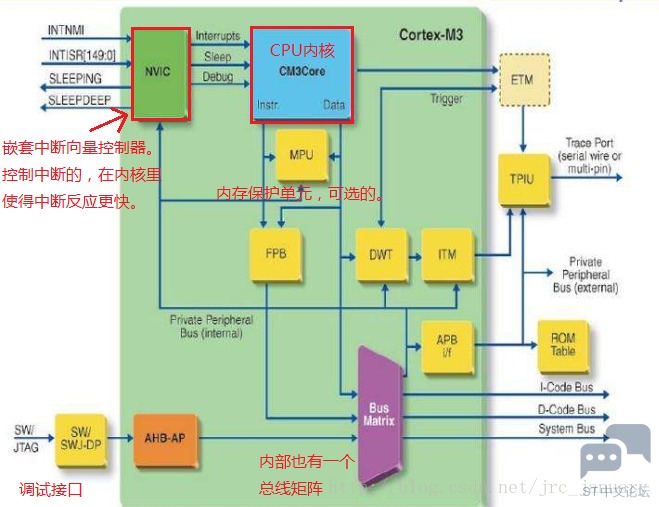

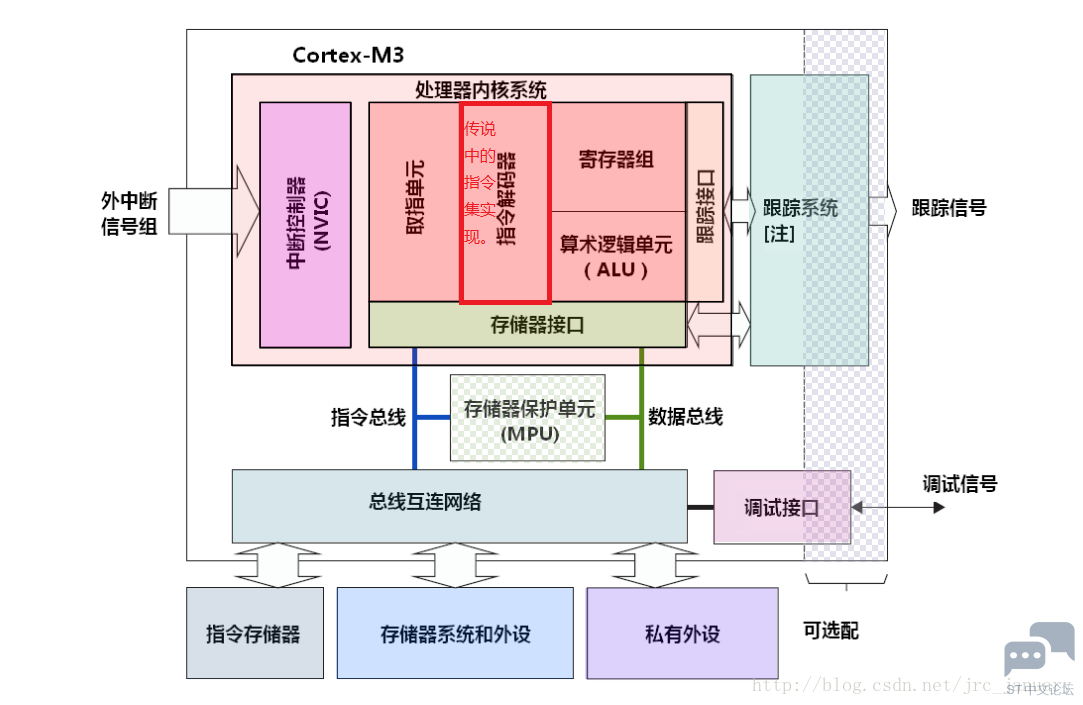

3.2 Cortex-M结构 和其他哈佛结构的精简指令集CPU一样,Cortex-M3的指令总线和数据总线是分开的,这样的设计大大提高了执行效率。 这货比较底层,也没什么好说的,不是太简单而是太复杂,不懂,所以不敢乱说。 看图:

内核的详细知识请看一本书: Cortex-M3 权威指南 Joseph Yiu 著 宋岩 译 4. 小结 主要描述了基于ARMv7架构的Cortex-M3内核的STM32F10XX芯片的架构。它包括: 哈佛结构的Cortex-M3内核(单片机的核心)。 驱动设备:数据总线、系统总线、DMA1、DMA2. 被驱动设备:嵌入式片上Flash、片上SRAM、FSMC、总线桥以及各种外设。 连接各个总线的总线矩阵。 还描述了存储器的映射关系。 意思意思了一下Cortex-M3内核。 |

【评分有奖】STM32 AI Sidekick聊天工具上线,快来体验一下吧!

ST TouchGFX 实操系列视频+如何选择正确的帧缓冲区策略

ST TouchGFX 实操系列视频++如何添加图像

ST TouchGFX 实操系列视频+如何进行屏幕转换

ST TouchGFX 实操系列视频+控件的淡入淡出

ST TouchGFX 实操系列视频+移动控件的三种方法

ST TouchGFX 实操系列视频+如何创建用户界面(UI)

ST TouchGFX 实操系列视频+如何安装TouchGFX Designer和STM32Cube软件环境

【经验分享】STM32F1 GPIO工作原理

【经验分享】STM32F0xx_DMA收发USART数据配置详细过程

微信公众号

微信公众号

手机版

手机版