.png) STMCU小助手

发布时间:2022-7-17 21:21

STMCU小助手

发布时间:2022-7-17 21:21

|

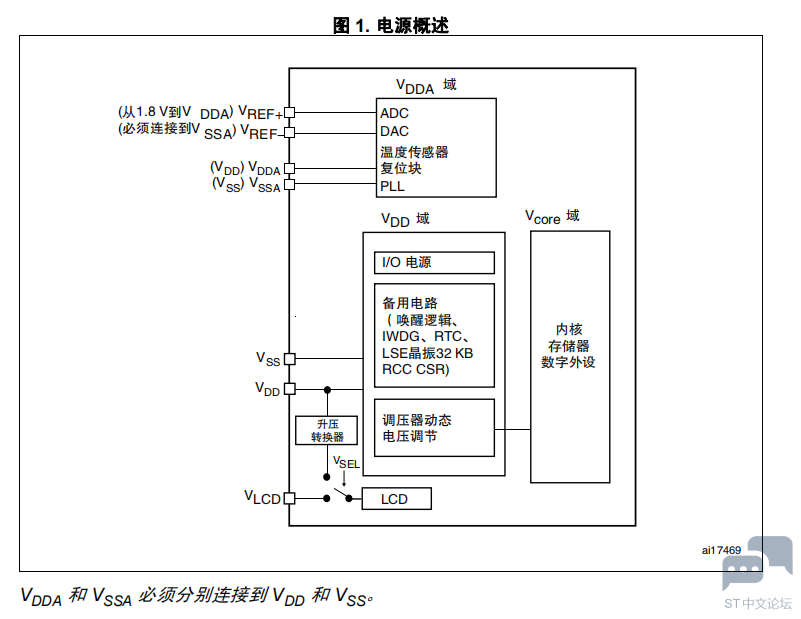

前言 本应用笔记为系统开发者们提供了所需的开发板特性硬件实现概述,如供电电源、时钟管理、复位控制、自举模式设置、调试管理。它显示了如何使用 STM32L1xxx 产品系列,说明了开发 STM32L1xxx 应用所需的最低硬件资源。 本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式。 1词汇表 •中容量器件为 Flash 范围为 32 至 128 K 字节的微控制器。 •中容量 + 器件为 Flash 等于 256 K 字节的微控制器。 •高容量器件为 Flash 等于 384 K 字节的微控制器。 2电源 2.1前言 数字电源电压 (VCORE)配有嵌入式的线性调压器,具有 1.2 至 1.8 V 的三个不同的可编程范围。 为达到全速、全功能,器件需要 2.0 至 3.6 V 的工作电压供电 (VDD),可达到 1.8 V 的数字电源电压VCORE (产品电压范围 1)。 当 VDD 工作于 1.65 至 3.6 V 时,可选择产品电压范围 2 (VCORE = 1.5 V)和 3 (VCORE =1.2 V)。此,频率分别限定为 16 MHz 和 4 MHz。 当不使用 ADC 和欠压复位 (BOR)时,器件可在 1.8 V 下至 1.65 V 的电源电压工作。

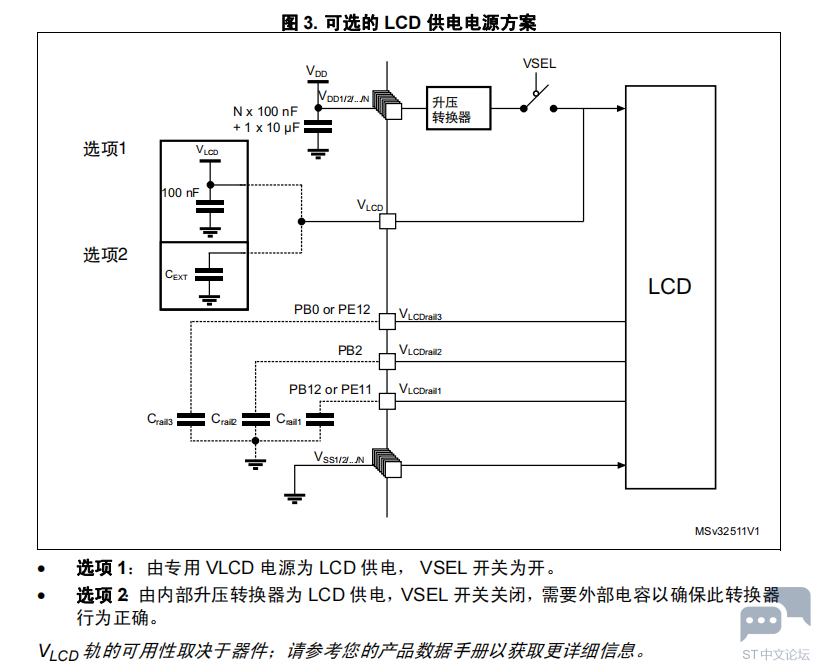

2.1.1独立 A/D 转换器电源和参考电压 为了提高转换精度, ADC 和 DAC 配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。 •ADC 电压源从单独的 VDDA 引脚输入。 •VSSA 引脚提供了独立的电源接地连接。 VDDA 和 VREF 需要一个稳定的电压。 VDDA 上的耗电电流可达若干 mA (若需更多信息,请参见产品手册中的 IDD (ADCx)、 IDD (DAC)、 IDD (COMPx)、 IVDDA、 IVREF)。 当可行时 (取决于封装), VREF- 必须连至 VSSA。 在 BGA 64 引脚和所有超过 100 引脚的封装上 为确保低电压输入和输出上的更好精度,用户可将 VREF+ 连接至一个独立的,低于 VDD 的外部参考电压源。对于模拟输入 (ADC)或输出 (DAC)信号, VREF+ 为最高电压,以满量程值表示。 •对于 ADC –对于全速 (ADCCLK = 16 MHz, 1 Msps), 2.4 V ≤ VREF+ = VDDA –对于中速 (ADCCLK = 8 MHz, 500 Ksps), 1.8 V ≤ VREF+ = VDDA –对于中速 (ADCCLK = 8 MHz, 500 Ksps), 2.4 V ≤ VREF+ ≠ VDDA –对于低速 (ADCCLK = 4 MHz, 250 Ksps), 1.8 V ≤ VREF+ < VDDA –当选择产品电压范围 3 时 (VCORE = 1.2 V), ADC 为低速 (ADCCLK = 4 MHz,250 Ksps) •对于 DAC – 1.8 V≤ VREF+ < VDDA 在 64 引脚及以下的封装上 (除了 BGA 封装) VREF+ 和 VREF- 引脚不可用。它们内部连至 ADC 电压供电 (VDDA)和地 (VSSA)。 2.1.2独立 LCD 供电 VLCD 引脚用于控制玻璃 LCD 的对比度。可用两种方法使用这一引脚: •它可从外部电路接收所需的最大电压,由微控制器通过 segment 和 common 线供给玻璃LCD。 •还可用它连接外部电容,微控制器将该电容用于内部的升压转换器。此升压转换器由软件控制,以向玻璃 LCD 的 segment 和 common 线提供所需的电压。请参考专门的产品数据手册以获得该电容值。 向 segment 和 common 线提供的电压定义了玻璃 LCD 像素的对比度。当在帧间配置了死区时,可降低此对比度。 2.1.3调压器 此内部调压器在复位后始终处于使能状态。可配置其为内核提供三个不同的电压范围。选择一个低 Vcore 范围可降低耗电,但会降低最大可接受内核速度。以降序排列的耗电范围如下: •范围 1,仅对高于 2.0 V 的 VDD 可用,具有最大速度 •范围 2 具有高至 16 MHz 的 CPU 频率 •范围 3 具有高至 4 MHz 的 CPU 频率 根据应用模式的不同,调压器可采用三种不同的模式工作。 •在运行模式中,调压器为 Vcore 域 (内核、存储器和数字外设)提供全功率。 •在停止模式、低功耗运行与低功耗等待模式中,调压器为 Vcore 域提供低功耗,以保留寄存器和 SRAM 的内容。 •在待机模式中,调压器掉电。除了连至备用电路的部分,寄存器和 SRAM 的内容丢失。 2.2电源方案 电路由稳定的供电电源 VDD 供电。 •VDD 引脚必须连至带有外部去耦电容的 VDD ;封装的单个钽电容或陶瓷电容 (最低4.7 µF,典型 10 µF) + 每个 VDD 引脚一个 100 nF 陶瓷电容)。 •VDDA 引脚必须连至两个外部去耦电容 (100 nF 陶瓷电容 + 1 µF 钽电容或陶瓷电容)。 •VREF+ 引脚可连至 VDDA 外部供电电源。若在 VREF+ 上施加了一个单独的外部参考电压,则必须将一个 100 nF 和一个 1 µF 电容连至此引脚。若需补偿 Vref 上的峰值耗电,当采样速度高时,可将 1 µF 电容增加至最大 10 µF。当使用 ADC 或 DAC 时, VREF+ 必须保持在 1.8 V 和 VDDA 之间。当 ADC 和 DAC 未激活时, VREF+ 可接地;这可让用户能够关闭外部电压参考。 •可采用更多措施过滤模拟噪声:VDDA 可通过铁氧体磁环连至 VDD。

完整版请查看:附件 |

![T~A~M6P[~2]E{]7(Z[GC915.png T~A~M6P[~2]E{]7(Z[GC915.png](data/attachment/forum/202207/17/211727yz0um4kn7xk04m49.png)

CD00273528_ZHV7.pdf

下载715.79 KB, 下载次数: 3

微信公众号

微信公众号

手机版

手机版